# **OPEN**

# High Performance All Nonmetal SiN<sub>x</sub> Resistive Random Access Memory with Strong Process Dependence

Te Jui Yen<sup>1</sup>, Albert Chin<sup>1\*</sup> & Vladimir Gritsenko<sup>2,3,4</sup>

All-nonmetal resistive random access memory (RRAM) with a N<sup>+</sup>–Si/SiN<sub>x</sub>/P<sup>+</sup>–Si structure was investigated in this study. The device performance of SiN<sub>x</sub> developed using physical vapor deposition (PVD) was significantly better than that of a device fabricated using plasma-enhanced chemical vapor deposition (PECVD). The SiN<sub>x</sub> RRAM device developed using PVD has a large resistance window that is larger than 10<sup>4</sup> and exhibits good endurance to 10<sup>5</sup> cycles under switching pulses of 1  $\mu$ s and a retention time of 10<sup>4</sup> s at 85 °C. Moreover, the SiN<sub>x</sub> RRAM device developed using PVD had tighter device-to-device distribution of set and reset voltages than those developed using PECVD. Such tight distribution is crucial to realise a large-size cross-point array and integrate with complementary metal-oxide-semiconductor technology to realise electronic neurons. The high performance of the SiN<sub>x</sub> RRAM device developed using PVD is attributed to the abundant defects in the PVD dielectric that was supported by the analysed conduction mechanisms obtained from the measured current–voltage characteristics.

Resistive random access memory (RRAM)<sup>1-26</sup> has attracted considerable attention over the past two decades due to its simple structure, nonvolatility, high scalability, rapid switching speed, and relatively low operating power. These advantages make RRAM devices suitable for use in future artificial intelligence and neuromorphic computing applications<sup>1-4</sup>. A variety of binary composite materials, such as HfO<sub>2</sub>, TaO<sub>2</sub>, TiO<sub>2</sub>, SiO<sub>2</sub>, and GeO<sub>5</sub>, that exhibit different device properties have been used as the switching layer. Although various conduction mechanisms for RRAMs have been proposed, the carrier transport behaviour of RRAMs still has not been completely confirmed. To prevent the metal ions from contributing to transport behaviour, we pioneered nonmetal GeO<sub>x</sub> dielectric RRAM devices<sup>6-10</sup> and all-nonmetal N<sup>+</sup>-Si/SiO<sub>x</sub>/P<sup>+</sup>-Si RRAM devices<sup>11</sup>. In this study, we investigated the all-nonmetal SiN<sub>x</sub> RRAM devices in which the bond enthalpy of SiN is lower than that of SiO<sup>27</sup>. The SiN<sub>x</sub> material has been widely used in the semiconductor industry for various applications, such as the passivation layer of an integrated circuit and the charge-trapping layer of a flash memory. This material can be easily integrated into complementary metal-oxide-semiconductor (CMOS) technology. Moreover, the RRAM device performance strongly depends on the SiN<sub>x</sub> formation process. A high-performance RRAM device with a large memory window, good endurance, long retention time, and tight device-to-device distribution of the set–reset voltages  $V_{\mathit{set}}$  –  $V_{\mathit{reset}}$  is only achievable when the  $\mathrm{SiN_x}$  layers are formed using low-temperature physical vapor deposition (PVD) rather than the standard plasma-enhanced chemical vapor deposition (PECVD). The high-performance SiN<sub>x</sub> RRAM device developed using PVD (PVD-SiN<sub>x</sub> RRAM device) is linked to the high number of defects and high amount of defect-related current conduction in the SiN<sub>x</sub> dielectric.

## Results

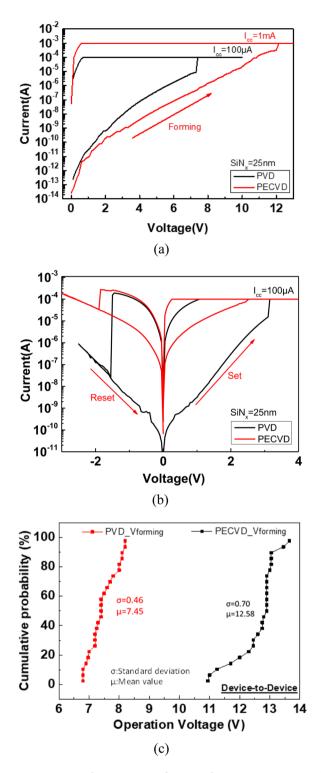

Figure 1(a) displays the forming process of the PVD-SiN<sub>x</sub> RRAM device and the SiN<sub>x</sub> RRAM device developed using PECVD (PECVD-SiN<sub>x</sub> RRAM device). While the forming step of fabricating the PECVD-SiN<sub>x</sub> RRAM device, the  $I_{cc}$  value was increased from 100  $\mu$ A with a 100- $\mu$ A step until the resistance state could be switched to the low-resistance state (LRS) at an  $I_{cc}$  value of 1 mA. The PVD-SiN<sub>x</sub> RRAM device exhibited lower  $I_{cc}$  and lower forming voltage than those of the PECVD-SiN<sub>x</sub> RRAM device. These results reflect that the initial PVD-SiN<sub>x</sub>

<sup>1</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, 300, Taiwan. <sup>2</sup>Rzhanov Institute of Semiconductor Physics. Siberian Branch, Russian Academy of Sciences, Novosibirsk, Russia. <sup>3</sup>Novosibirsk State University, Pirogova street, 2, Novosobirsk, 630090, Russia. <sup>4</sup>Novosibirsk State Technical University, K. Marx Ave., 20, Novosibirsk, 630073, Russia. \*email: achin@nctu.edu.tw

**Figure 1.** *I-V* characteristics of PVD and PECVD  $SiN_x$  RRAM devices of (a) forming process, (b) set-reset processes, and (c) forming voltage distributions.

RRAM device has more defects to form a conduction path than the PECVD-SiN<sub>x</sub> RRAM device. Figure 1(b) depicts the typical bipolar switching characteristics of both PVD-SiN<sub>x</sub> and PECVD-SiN<sub>x</sub> RRAM devices. The PVD-SiN<sub>x</sub> RRAM device exhibits a significantly lower high-resistance state (HRS) current and a larger resistance window than those of the PECVD-SiN<sub>x</sub> RRAM device. The much higher HRS current in the PECVD-SiN<sub>x</sub> RRAM device may be related to the higher  $I_{cc}$  and bias voltage values needed during the forming process, where such high power may damage the SiN<sub>x</sub> and create unrecoverable defects. The asymmetric LRS *I-V* curve of the PECVD device may be due to the large forming voltage and power to generate excessive defects, which may be partially annihilated by injected electrons during negative voltage swept. Figure 1(c) shows the forming voltage

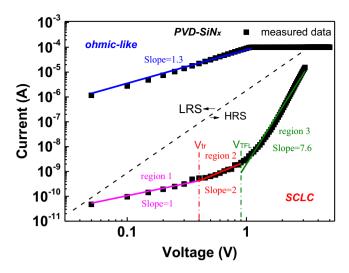

**Figure 2.** I-V characteristics of PVD-SiN<sub>x</sub> RRAM device were analyzed by the space-charge limited conduction (SCLC) in HRS and ohmic-like behavior conduction in LRS.

distributions of PVD-SiN $_{\rm x}$  and PECVD-SiN $_{\rm x}$  devices, which are ranged from 6.8 to 8.2 V and from 11.0 to 13.7 V, respectively.

To further understand the carrier conduction mechanism, we analysed the measured data by using various transport mechanisms. Because there is no metal inside the dielectric to form the metallic filament, the conduction mechanism of nonmetal RRAM device is attributed to defect-related hopping conduction  $^{10,12,13}$ . Figures 2 and 3 display the analysed conduction mechanisms for PVD-SiN<sub>x</sub> and PECVD-SiN<sub>x</sub> RRAM devices, respectively. The very low HRS current in the PVD-SiN<sub>x</sub> RRAM devices, as presented in Fig. 2, is attributed to the space-charge limited conduction (SCLC) mechanism  $^{14-16,28}$ . The SCLC regions are divided into three regions by using the transition voltage  $V_{tr}$  and trap-filled limited voltage  $V_{TFL}$ . For the low-bias voltage region that is less than  $V_{tr}$  the current is proportional to voltage and follows Ohm's law, with an extremely high resistance of approximately 10 G $\Omega$ . The current density-voltage (J-V) relationship obtained when the applied voltage is larger than  $V_{tr}$  but lower than  $V_{TFL}$  (region 2) can be expressed as follows  $^{17,29}$ :

$$J = \frac{9\mu\varepsilon\theta}{8d^3}V^2, \,\theta = \frac{J_{free}}{J_{trap} + J_{free}},\tag{1}$$

where I,  $\mu$ ,  $\varepsilon$ , d, and  $\theta$  represent the current density, electron mobility, static dielectric constant, dielectric layer thickness, and ratio of the free current density to the trapped and free current densities, respectively. In this region, shallow traps are gradually filled by increasing the electric field, and the injected free carrier current density  $I_{free}$  significantly contributes to the total current density. All the traps at voltages larger than  $V_{TFL}$  are filled by injected carriers. A massive number of free carriers contribute to current conduction under a high electric field, thus leading to a steep current–voltage (I-V) slope (region 3) For the PVD device, the currents of HRS I-V curves increase with increasing temperature  $I^{18}$ . Conversely, the LRS, which exhibited ohmic-like behavior, can be analysed with a slope of I.  $I^{19}$ .

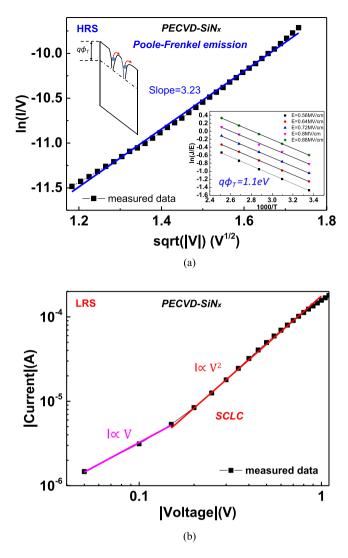

For the HRS current of the PECVD-SiN<sub>x</sub> devices presented in Fig. 3(a), the current conduction resembles Poole–Frenkel (P–F) emission  $^{19,20,29-32}$ :

$$J = q\mu N_c E \exp \left[ \frac{-q(\phi_T - \sqrt{qE/\pi\varepsilon_i\varepsilon_0})}{kT} \right], \tag{2}$$

where J,  $\mu$ ,  $N_{c}$ ,  $q\phi_{T}$ , E,  $\varepsilon_{0}$ , k, and T are the current density, electron drift mobility, density state in the conduction band, energy level of trap, electric field, dynamic permittivity, vacuum permittivity, Boltzmann's constant, and absolute temperature, respectively. A trap energy  $q\phi_{T}$  of  $1.1\,\mathrm{eV}$  was determined according to the Arrhenius plots presented in Fig. 3(a) at a temperature range from 298 to 398 K. An  $\varepsilon_{i}$  value of 4.3 was obtained from the slope of P–F plots and is lower than the static permittivity ( $\varepsilon=7$ )<sup>33</sup>. P–F emission occurs due to electrons hopping between nearby traps<sup>34</sup> which leads to a high HRS current, as shown in Fig. 1(b). Figure 3(b) displays the LRS I-V characteristics of the PECVD-SiN<sub>x</sub> device that adheres to the SCLC under the most-negative voltage bias region.

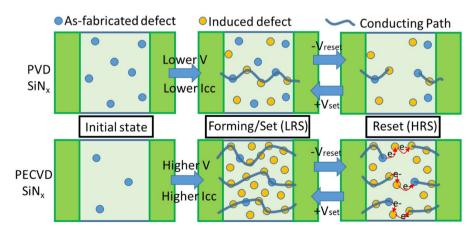

Figure 4 illustrates the potential switching behaviours of the SiN<sub>x</sub> RRAM device. The PVD-SiN<sub>x</sub> dielectric has abundant defects in the initial condition because of its room temperature deposition with a low annealing temperature of 200 °C. The current conducting path can be formed and switched to LRS with a relatively low  $I_{cc}$  value and voltage. By contrast, the PECVD-SiN<sub>x</sub> dielectric was deposited at a relatively high temperature of 300 °C, with fewer defects, so the conducting path could not be formed under low  $I_{cc}$  and voltage values. Therefore, a high forming voltage of 12 V and a high  $I_{cc}$  of 1 mA were required. Under such a high electric field, a large number of Si–N bonds were broken and excessive defects were created. The excessive defects in the PECVD-SiN<sub>x</sub> layer

**Figure 3.** *I-V* curves of PECVD-SiN<sub>x</sub> RRAM were analyzed with (a) Poole-Frenkel (P-F) emission in HRS and (b) space charge limited conduction in LRS. The inset figure in (a) is Arrhenius plot of the PF emission.

**Figure 4.** Schematic diagram of potential resistance switching in SiN<sub>x</sub> RRAM.

may create multiple conduction paths and lead to a high HRS current, as shown in Fig. 1(b). To switch from LRS back to HRS, a negative  $V_{reset}$  was applied to rupture the conducting path. Although the conducting paths were ruptured, the electrons in the PECVD-SiN<sub>x</sub> layer had a high possibility to conduct current in parallel ways via

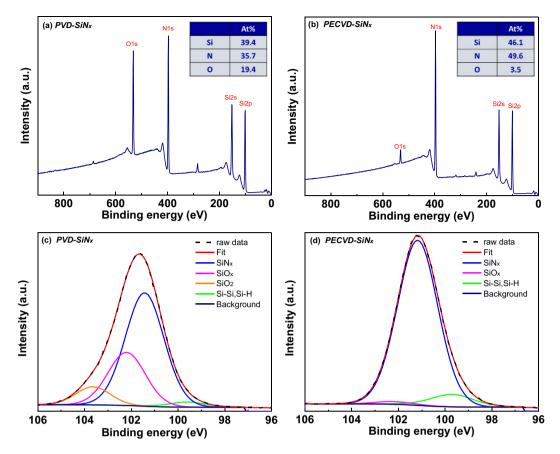

**Figure 5.** XPS data of (a) PVD-SiN<sub>x</sub> (b) PECVD-SiN<sub>x</sub> layers, and the related Si 2p spectrum of (c) PVD-SiN<sub>x</sub> film (d) PECVD-SiN<sub>x</sub> layers.

hopping through nearby defects. This further led to the high measured HRS current. Conducting paths can be formed again for electron transportation when a positive  $V_{set}$  is applied to the top electrode.

The deposited  $SiN_x$  layers were further analysed using X-ray photoelectron spectroscopy (XPS). Figure 5(a,b) depict the XPS data for PVD- $SiN_x$  and PECVD- $SiN_x$  layers, respectively. The related Si 2p spectra obtained from the XPS data are displayed in Fig. 5(c,d) for the PVD- $SiN_x$  and PECVD- $SiN_x$  layers, respectively. The N-Si composition of the as-fabricated PVD- $SiN_x$  and PECVD- $SiN_x$  layers were 0.91 and 1.08, respectively, which indicates a high number of defects inside the PVD- $SiN_x$  layer. The nitride vacancies<sup>21,35</sup> and Si dangling bonds<sup>22,23</sup> can play crucial roles to form the conducting path. The slightly higher oxygen content in the PVD- $SiN_x$  layer than in the PECVD- $SiN_x$  layer cannot explain the significantly better device performance because the bond enthalpy of SO is higher than that of SN. That is, it is more difficult to break the SO bond to form the defects. Therefore, the XPS results support the proposed model depicted in Fig. 4 and adequately explain the measured I-V characteristics in Fig. 1 and the analysed current conduction mechanisms in Figs. 2 and 3. Such defect-assisted conduction is also the major mechanism for similar  $GeO_x$  RRAM devices<sup>10</sup>. The conducting path can be constructed or broken by the different polarities of the applied voltage.

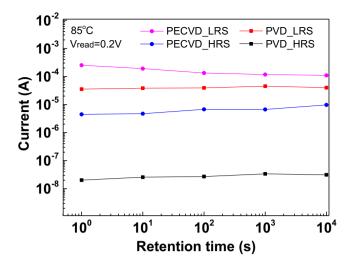

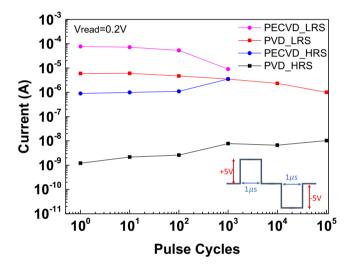

Device endurance and data retention are the crucial characteristics of a nonvolatile memory. Figure 6 shows the retention data of PVD-SiN $_{\rm x}$  and PECVD-SiN $_{\rm x}$  RRAM devices under an 85 °C test condition. The PECVD-SiN $_{\rm x}$  device exhibits a much smaller resistance window and a rapid degradation from an initial value of 56 to 11 after  $10^4$  s retention at 85 °C. The poor retention can be ascribed to the high forming voltage with large kinetic energy; then the electrons at 85 °C can partially annihilate or create a leakage path with multiple defects, as shown in Fig. 4. By contrast, the resistance window of an all-nonmetal PVD-SiN $_{\rm x}$  RRAM device slightly decreases from  $1.8 \times 10^3$  to  $1.3 \times 10^3$  after a retention time of  $10^4$  s at 85 °C. The RRAM device endurance data are shown in Fig. 7, where the  $V_{set}$  pulses of +5 V and -5 V were applied to devices with a 1- $\mu$ s pulse width. The resistance window of the PECVD-SiN $_{\rm x}$  device degraded quickly, and the device failed after  $10^3$  endurance cycles. Conversely, a large resistance window of two orders of magnitude was obtained for the PVD-SiN $_{\rm x}$  RRAM device, even after  $10^5$  pulse cycles. The excellent endurance of the PVD-SiN $_{\rm x}$  device is related to the high number of defects that can be set and reset easily, with less destruction to the dielectric material.

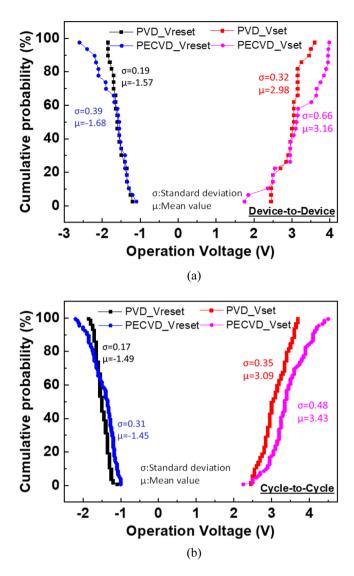

Figure 8(a,b) display the device-to-device and cycle-to-cycle distributions of  $V_{set}$  and  $V_{reset}$  respectively, which are critical for the RRAM cross-point array<sup>24–26</sup>. The coefficient of variation (CV) was used to study the distribution and is defined as follows:

Figure 6. Retention test of N<sup>+</sup>-Si/PVD-SiN<sub>x</sub>/P<sup>+</sup>-Si and N<sup>+</sup>-Si/PECVD-SiN<sub>x</sub>/P<sup>+</sup>-Si RRAM devices under 85 °C.

**Figure 7.** Endurance characteristics of N<sup>+</sup>-Si/SiN<sub>x</sub>/P<sup>+</sup>-Si RRAM devices.

$$CV = \frac{\sigma}{|\mu|} \times 100\% , \qquad (3)$$

where  $\sigma$  is the standard deviation, and  $\mu$  is the mean value. The lower CV value represents a tighter distribution and is crucial for a larger array size<sup>26</sup>. The device-to-device distributions were extracted from 25 different devices. The CVs of  $V_{set}$  and  $V_{reset}$  of the PVD-SiN $_x$  RRAM were 10.7% and 12.1%, respectively, which are remarkably tighter than the 18.3% and 23.2% of PECVD-SiN $_x$  devices, respectively. The cycle-to-cycle variations of the first 100 consecutive DC switching cycles, depicted in Fig. 8(b), also show the crucially tighter operation voltage distributions of PVD-SiN $_x$  RRAM devices than those of PECVD-SiN $_x$  ones. During the forming step, the dielectric soft breakdown must occur by breaking part of the SiN bonds. Based on the preceding discussion, the PECVD-SiN $_x$  RRAM device requires a higher  $I_{cc}$  value and voltage during fabrication to create a conducting path that has an excessive number of defects and an uncontrollable reset current. These results further lead to poor  $V_{set}$  and  $V_{reset}$  distribution and fewer endurance cycles. One issue of nonmetal RRAM device is the relatively larger operation voltage than that of metal-oxide RRAM device, even though the operation voltage is still much less than that of a flash memory GeO $_x$  dielectric, in which the defect-related conduction path can be formed by breaking the dielectric at low energy.

## Conclusion

High-performance all-nonmetal  $N^+$ -Si/SiN<sub>x</sub>/ $P^+$ -Si RRAM devices were achieved. The device performance was highly dependent on the deposition process. In this process, the current conduction in the RRAM device was highly related to the defects inside the SiN<sub>x</sub> layer. The PVD-SiN<sub>x</sub> RRAM devices exhibited favourable memory characteristics: a large memory window, high pulsed endurance, a long data retention time at 85 °C, and tight

**Figure 8.** Operation voltage distributions of SiN<sub>x</sub> RRAM devices for (a) device to device and (b) cycle-to-cycle.

device-to-device  $V_{set}$  and  $V_{reset}$  distributions. The PVD-SiN<sub>x</sub> RRAM device has high potential to realise a large-size cross-point memory array and to be embedded in CMOS technology to realise electronic neurons.

#### Methods

A  $P^+$  silicon wafer was used as a bottom gate. After conducting the RCA clean for the wafer and dipping the wafer into dilute HF to remove the native oxide, a 25-nm-thick  $\mathrm{SiN}_x$  layer was formed by either PVD using electron-beam evaporation or PECVD. Additional furnace annealing was applied to the PVD- $\mathrm{SiN}_x$  layer at  $200\,^{\circ}\mathrm{C}$  in a  $\mathrm{N}_2$  ambient for  $30\,\mathrm{min}$ . For the PECVD- $\mathrm{SiN}_x$  layer, a NH $_3$  of 6 sccm, 8%  $\mathrm{SiH}_4$  in Ar of 125 sccm, and  $\mathrm{N}_2$  of 200 sccm were used at a temperature of  $300\,^{\circ}\mathrm{C}$ . Finally, the N $^+$ -Si top electrode was fabricated as the top electrode with a diameter of  $120\,\mu\mathrm{m}^{11}$ . The electrical characteristics were measured using the HP4155B analyser. The pulse stress was generated using a pulse generator (81110, Agilent). Material analysis was performed through XPS analysis by using Thermo Scientific K-Alpha with an X-ray spot size of  $400\,\mu\mathrm{m}$ .

Received: 20 November 2019; Accepted: 27 January 2020; Published online: 18 February 2020

#### References

- 1. Wong, H.-S. P. & Salahuddin, S. Memory leads the way to better computing. Nat. Nanotech. 10, 191–194 (2015).

- 2. Yao, P. et al. Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017).

- 3. Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol. 8, 13-24 (2012).

- 4. Gao, B. et al. Modeling disorder effect of the oxygen vacancy distribution in filamentary analog RRAM for neuromorphic computing. IEDM Tech. Dig. 91–94 (2017).

- 5. Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-based resistive switching memories—Nanoionic mechanisms, prospects, and challenges. *Adv. Mater.* 21, 2632–2663 (2009).

- 6. Chou, K. I., Cheng, C. H., Zheng, Z. W., Liu, M. & Chin, A. Ni/GeO<sub>x</sub>/TiOy/TaN RRAM on flexible substrate with excellent resistance distribution. *IEEE Electron Device Lett.* **34**, 505–507 (2013).

- Cheng, C. H., Chou, K. Y., Chin, A. & Yeh, F. S. Very high performance non-volatile memory on flexible plastic substrate. IEDM Tech. Dig. 512–515 (2010).

- 8. Cheng, C. H., Chin, A. & Yeh, F. S. High performance ultra-low energy RRAM with good retention and endurance. *IEDM Tech. Dig.* 448–451 (2010).

- 9. Cheng, C. H., Chin, A. & Yeh, F. S. Novel ultra-low power RRAM with good endurance and retention. Symp. on VLSI Tech. Dig. 85–86 (2010).

- Shaposhnikov, A. V., Perevalov, T. V., Gritsenko, V. A., Cheng, C. H. & Chin, A. Mechanism of GeO<sub>2</sub> resistive switching based on the multi-phonon assisted tunneling between traps. Appl. Phys. Lett. 100, 243506 (2012).

- 11. Yen, T. J., Gismatulin, A., Volodin, V., Gritsenko, V. & Chin, A. All Nonmetal Resistive Random Access Memory. Sci. Rep. 9, 6144 (2019).

- 12. Zhang, Y. et al. Study of conduction and switching mechanisms in Al/AlO<sub>x</sub>/WO<sub>x</sub>/W resistive switching memory for multilevel applications. Appl. Phys. Lett. 102, 233502 (2013).

- 13. Wang, L. et al. Transport properties of HfO<sub>2-x</sub> based resistive-switching memories. Phys. Rev. B. 85, 195322 (2012).

- 14. Kumbhare, P. A selectorless RRAM with record memory window and nonlinearity based on trap filled limit mechanism. *IEEE Non-Volatile Memory Technol. Symp.* (NVMTS), 1–3 (2015).

- 15. Yu, L. E., Kim, S., Ryu, M. K., Choi, S. Y. & Choi, Y. K. Structure effects on resistive switching of Al/TiO<sub>x</sub> /Al devices for RRAM applications. *IEEE Electron Device Lett.* **29**, 331–333 (2008).

- Dong, R. et al. Reproducible hysteresis and resistive switching in metal-Cu<sub>x</sub>O-metal hetero structures. Appl. Phys. Lett. 90, 042107 (2007).

- 17. Kim, K. M., Choi, B. J., Shin, Y. C., Choi, S. & Hwang, C. S. Anode-interface localized filamentary mechanism in resistive switching of TiO2 thin films. *Appl. Phys. Lett.* **91**, 012907 (2007).

- 18. Gismatulin, A. A., Gritsenko, V. A., Yen, T. –J. & Chin, A. Charge transport mechanism in SiN<sub>x</sub>-based memristor. *Appl. Phys. Lett.* 115, 253502 (2019).

- Rana, A. M. et al. Endurance and cycle-to-cycle uniformity improvement in tri layered CeO<sub>2</sub>/Ti/CeO<sub>2</sub> resistive switching devices by changing top electrode material. Sci. Rep. 7, 39539 (2017).

- Gismatulin, A. A. et al. Charge transport mechanism of high-resistive state in RRAM based on SiO<sub>x</sub>. Appl. Phys. Lett. 114, 033503 (2019).

- 21. Zhang, Z. et al. All-Metal-Nitride RRAM Devices. IEEE Electron Device Lett. 36, 29-31 (2015).

- 22. Jiang, X. et al. a-SiN<sub>x</sub>:H-Based ultra-low power resistive random access memory with tunable si dangling bond conducting paths. Sci. Rep. 5, 15762 (2015).

- 23. Kim, Ś. & Park, G. B. Nonlinear and multilevel resistive switching memory in Ni/Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub>/TiN structures. *Appl. Phys. Lett.* **108**, 212103 (2016).

- 24. Zackriya, M., Kittur, H. M. & Chin, A. A novel read scheme for large size one-resistor resistive random access memory array. Sci. Rep. 7, 42375 (2017).

- 25. Zackriya, M., Chin, A. & Kittur, H. M. Impact of current distribution on RRAM array with high and low Ion/Ioff devices. *IEEE EDTM Tech. Dig.*, 156–157 (2017).

- Chen, Y. D. & Chin, A. An offset readout current sensing scheme for one-resistor RRAM-based cross-point array. IEEE Electron Device Lett. 40, 208–211 (2019)

- 27. Yu, D. S. et al. Lanthanide and Ir-based Dual Metal-Gate/HfAlON CMOS with Large Work-Function Difference. IEDM Tech. Dig. 634–637 (2005).

- 28. Rose, A. Space-charge-limited currents in solids. Phys. Rev. 97, 1538-1544 (1955).

- 29. Chiu, F. A review on conduction mechanisms in dielectric films. Adv. Mater. Sci. Eng. 2014, 1-18 (2014).

- 30. Yeargan, J. R. & Taylor, H. L. The Poole-Frenkel effect with compensation present. J. Appl. Phys. 39, 5600–5604 (1968).

- Liu, M. et al. Terahertz-field-induced insulator-to-metal transition in vanadium dioxide metamaterial. Nature. 487, 345–348 (2012).

Chiu, Y. C., King, T. J. & Pan, T. M. Current conduction mechanisms in Pr<sub>2</sub>O<sub>3</sub>/oxynitride laminated gate dielectrics. Journal of Applied Physics. 105, 074103 (2009).

- 33. Robertson, J. High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 28, 265–291 (2004).

- 34. Jonscher, A. K. & Loh, C. K. Poole-Frenkel conduction in high alternation electric fields. Solid State Phys. 4, 1341-1347 (1971).

- 35. Hassine, N. B. *et al.* Dielectrical properties of metal-insulator-metal aluminum nitride structures: Measurement and modeling. *J. Appl. Phys.* **105**, 044111-1–044111-10 (2009).

- 36. Tsai, C. Y. et al. Highly-scaled 3.6-nm ENT trapping layer MONOS device with good retention and endurance. IEDM Tech. Dig. 110–113 (2010).

# Acknowledgements

This paper's publication was supported in part by Ministry of Science and Technology of Taiwan, project no. 107-2923-E-009-001-MY3 and Russian Science Foundation (project no. 18-49-08001).

#### **Author contributions**

T.J. Yen did the experiments; Albert Chin is the principle investigator (PI) to monitor the project; Vladimir Gritsenko is the co-PI for this work. All authors reviewed the manuscript.

#### Competing interests

The authors declare no competing interests.

# **Additional information**

Correspondence and requests for materials should be addressed to A.C.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The results of this research have important contributions for RRAM device.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2020