## ARTICLE

https://doi.org/10.1038/s41467-020-20732-w

OPEN

# Benchmarking monolayer MoS<sub>2</sub> and WS<sub>2</sub> field-effect transistors

Amritanand Sebastian <sup>1</sup>, Rahul Pendurthi<sup>1</sup>, Tanushree H. Choudhury<sup>2</sup>, Joan M. Redwing<sup>2,3,4</sup> & Saptarshi Das <sup>1,3,4 \vee}</sup>

Here we benchmark device-to-device variation in field-effect transistors (FETs) based on monolayer  $MoS_2$  and  $WS_2$  films grown using metal-organic chemical vapor deposition process. Our study involves 230  $MoS_2$  FETs and 160  $WS_2$  FETs with channel lengths ranging from 5  $\mu$ m down to 100 nm. We use statistical measures to evaluate key FET performance indicators for benchmarking these two-dimensional (2D) transition metal dichalcogenide (TMD) monolayers against existing literature as well as ultra-thin body Si FETs. Our results show consistent performance of 2D FETs across  $1 \times 1 \text{ cm}^2$  chips owing to high quality and uniform growth of these TMDs followed by clean transfer onto device substrates. We are able to demonstrate record high carrier mobility of  $33 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  in WS<sub>2</sub> FETs, which is a 1.5X improvement compared to the best reported in the literature. Our experimental demonstrations confirm the technological viability of 2D FETs in future integrated circuits.

<sup>&</sup>lt;sup>1</sup> Department of Engineering Science and Mechanics, Penn State University, University Park, PA 16802, USA. <sup>2</sup> 2D Crystal Consortium-Materials Innovation Platform (2DCC-MIP), Penn State University, University Park, PA 16802, USA. <sup>3</sup> Department of Materials Science and Engineering, Penn State University, University Park, PA 16802, USA. <sup>4</sup> Materials Research Institute, Penn State University, University Park, PA 16802, USA. <sup>See</sup>email: sud70@psu.edu

wo-dimensional (2D) semiconducting materials beyond graphene<sup>1,2</sup> are receiving increasing attention owing to their ultra-thin body nature that can mitigate detrimental short-channel effects in aggressively scaled devices through improved electrostatics, enabling them to replace or complement the aging Si technology<sup>3-5</sup>. Molybdenum disulfide (MoS<sub>2</sub>) and tungsten disulfide (WS<sub>2</sub>), belonging to the family of transition metal dichalcogenides (TMDs), have been studied extensively in this context. In fact, high performance MoS<sub>2</sub> field-effect transistors (FETs) with a contact pitch of 70 nm and 42 nm have already been experimentally demonstrated<sup>6,7</sup>. Circuit level implementations of 2D FETs such as inverters, logic operators, ring oscillators, and radio-frequency devices have also been achieved<sup>8-12</sup>. Recently, a microprocessor based on MoS<sub>2</sub> FETs was reported<sup>13</sup>. Additionally, 2D FETs have found applications in various emerging technologies such as sensors for internet of things, neuromorphic computing, biomimetic devices, valleytronics, straintronics, and optoelectronic devices<sup>14-21</sup>. While initial demonstrations of prototype devices relied on exfoliated flakes, the 2D community has rapidly transitioned towards the growth of large-area films to address manufacturing needs for any commercial applications. In this context, chemical vapor deposition (CVD)<sup>22,23</sup> and metal-organic CVD (MOCVD)<sup>7,24</sup> are the most promising techniques, enabling growth of high quality 2D materials with different thermal budgets on various substrates. In fact, there are several reports demonstrating high-performance FETs based on CVD and MOCVD grown monolayer MoS<sub>2</sub> and WS<sub>2</sub>. However, most of these studies are based on one or only a few devices.

To assess the potential of 2D materials for future very large scale integrated (VLSI) circuits, it is important to study the variation in key device parameters that determine the ON-state and OFF-state performance across a large number of devices. Unfortunately, there are only a few studies that report device-todevice variation in 2D FETs<sup>7,25,26</sup>. Smithe et al. measured multiple parameters across 200 MoS<sub>2</sub> FETs and demonstrated low threshold voltage variation and low contact resistance on the order of 1 k $\Omega$ - $\mu$ m<sup>25</sup>. Similarly. Xu et al. analyzed 380 top-gated MoS<sub>2</sub> FETs and reported variation in threshold voltage and electron mobility<sup>26</sup>. However, both works concentrate on longer channel devices where the effects of contact resistance are not pronounced. In a separate study, Smithe et al.<sup>22</sup> measured scaled MoS<sub>2</sub> FETs based on synthetic monolayers; however, they did not provide any statistics. Smets et al.7 demonstrated the most significant study on scaling of CVD grown monolayer MoS<sub>2</sub>, wherein multiple devices with channel lengths ranging from 5 µm down to 29 nm were measured. However, their study was focused on the OFF-state performance. Finally, all of the aforementioned studies are based on MoS<sub>2</sub> FETs, and none exist for WS<sub>2</sub> FETs.

This work focuses on a comprehensive study of variation in key parameters related to both OFF-state and ON-state performance, such as threshold voltage, subthreshold slope, ratio of maximum to minimum current, field-effect carrier mobility, contact resistance, drive-current, and carrier saturation velocity, for different channel lengths ranging from 5 µm down to 100 nm using 230 MoS<sub>2</sub> FETs and 160 WS<sub>2</sub> FETs. In addition, we offer extensive benchmarking of our devices with respect to the abovementioned demonstrations as well as ultra-thin body (UTB) silicon (Si) on insulator (SOI) FETs with similar gate lengths to assess the technological viability and maturity of 2D FETs. Using statistical measures such as mean, median, standard deviation, and minimum/maximum values, we show low device-to-device variation. We are also able to demonstrate record high carrier mobility of 33 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in WS<sub>2</sub> FETs, which is a 1.5X improvement compared to the best reported in the literature. We attribute our accomplishments to the epitaxial growth of highly crystalline 2D monolayers on sapphire substrate *via* MOCVD technique at 1000 °C using chalcogen and sulfur precursors that minimize carbon contamination in the film, as well as to the clean transfer of the film from the growth substrate to the device fabrication substrate.

### Results

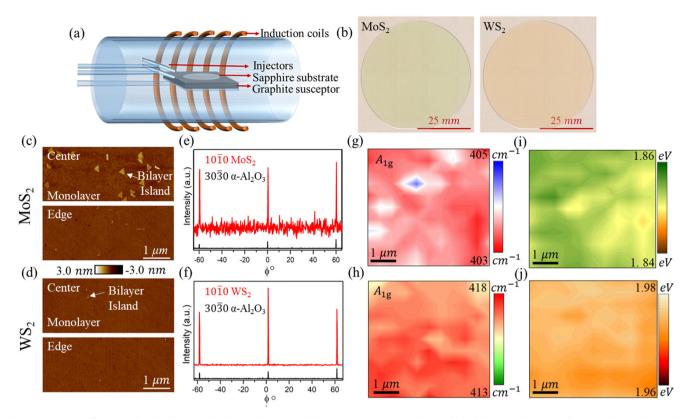

Synthesis and characterization of monolayer MoS<sub>2</sub> and WS<sub>2</sub>. MoS<sub>2</sub> and WS<sub>2</sub> were deposited by MOCVD on epi-ready 2" diameter c-plane sapphire wafers. Figure 1 summarizes the growth, structural, and optical characterization of the MOCVD grown MoS<sub>2</sub> and WS<sub>2</sub>. Figure 1a shows the schematic of the MOCVD system, comprising of a cold-wall horizontal reactor with an inductively heated graphite susceptor equipped with wafer rotation as previously described<sup>27</sup>. Molybdenum hexacarbonyl  $(Mo(CO)_6)$  and tungsten hexacarbonyl  $(W(CO)_6)$  were used as metal precursors, while hydrogen sulfide (H<sub>2</sub>S) was the chalcogen source with H<sub>2</sub> as the carrier gas. MoS<sub>2</sub> was deposited in a single step process at 1000 °C, where coalesced monolayer growth across the 2" wafer was achieved in 18 min. WS2 was deposited using a multi-step process with nucleation at 850 °C and lateral growth at 1000 °C, resulting in coalesced monolayer growth across the 2" wafer in 10 min<sup>28</sup>. In both cases, after growth the substrate was cooled in H<sub>2</sub>S to 300 °C to inhibit decomposition of the MoS<sub>2</sub> and WS<sub>2</sub> films. Figure 1b shows uniformly grown MoS<sub>2</sub> and WS<sub>2</sub> films over 2" sapphire wafers. Further growth details can be found in the "Methods" section. The morphology of the monolayer films at the center and edge of the 2" wafer is shown in Fig. 1c, d for MoS<sub>2</sub> and WS<sub>2</sub>, respectively, using atomic force microscopy (AFM). Height profiles obtained from scratch testing confirm monolayer film formation (see Supplementary Fig. 1a, b). The monolayers are fully coalesced, with undulations arising from steps on the sapphire surface. The overall bilayer density is low but a higher density of bilayers is present at the center of the MoS<sub>2</sub> film compared to the WS<sub>2</sub> film. The in-plane X-ray diffraction (XRD) patterns in Fig. 1e, f highlight the epitaxial relation between the sulfide monolayers and the underlying sapphire substrates. The fullwidth at half maxima of the  $\phi$ -scan peaks are 0.3° and 0.17° for MoS<sub>2</sub> and WS<sub>2</sub>, respectively, indicating a low rotational misorientation of domains within the monolayers. The films were transferred to Al<sub>2</sub>O<sub>3</sub>/Pt/TiN/p<sup>++</sup>-Si substrates for device fabrication, as discussed later. The transferred film quality was assessed using Raman maps as shown in Fig. 1g, h, and photoluminescence (PL) maps as shown in Fig. 1i, j, for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. Raman maps show less than 5% variation in the representative  $A_{1g}$  peak position. The uniform PL peak positions observed at 1.84 eV for  $MoS_2$  and 1.97 eV for  $WS_2$  correspond to their monolayer response. Representative Raman and PL spectra are included in the Supplementary Fig. 1c-f.

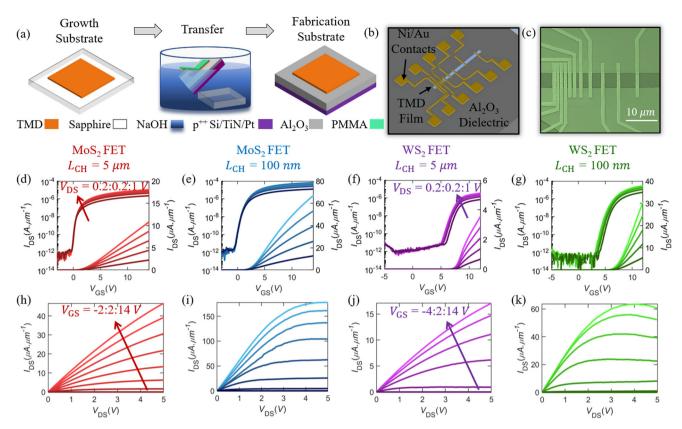

**Monolayer MoS<sub>2</sub> and WS<sub>2</sub> device fabrication and characterization**. To investigate the electrical properties of the MOCVD grown TMD films, back-gated FETs were fabricated on  $Al_2O_3/Pt/$ TiN/p<sup>++</sup>-Si substrates. 50 nm  $Al_2O_3$  gate dielectric was deposited using atomic layer deposition (ALD). The choice of a thin, high-k gate dielectric with an effective oxide thickness (EOT) of 22 nm, compared to conventionally used 300 nm SiO<sub>2</sub>, was to allow for better gate electrostatics. The Pt/TiN/ p<sup>++</sup>-Si stack acts as the gate electrode (see "Methods" section for more details on gate dielectric fabrication) for each substrate. The TMD films were transferred from sapphire (growth substrates) onto the  $Al_2O_3$ substrates *via* the poly(methyl methacrylate) (PMMA)-assisted wet-transfer process<sup>29</sup>, as shown in Fig. 2a (see "Methods" section

**Fig. 1 Monolayer film growth and characterization. a** Schematic of the MOCVD system with a cold-wall horizontal reactor. **b** 2" sapphire wafer with MOCVD grown MoS<sub>2</sub> and WS<sub>2</sub>. AFM images of **c** MoS<sub>2</sub> and **d** WS<sub>2</sub> at the center and edge of the respective wafers. Towards the center of the MoS<sub>2</sub> film, few bilayers are seen. In-plane XRD  $\phi$ -scan of **e** MoS<sub>2</sub> and **f** WS<sub>2</sub> on sapphire ( $\alpha$ -Al<sub>2</sub>O<sub>3</sub>), showing the epitaxial relationship between the monolayers and the sapphire substrate. Raman map of the A<sub>1g</sub> peak position for **g** MoS<sub>2</sub> and **h** WS<sub>2</sub> films transferred from the growth substrate onto the device fabrication substrate with 50 nm ALD Al<sub>2</sub>O<sub>3</sub>. Low variation in the peak position is observed for both MoS<sub>2</sub> and WS<sub>2</sub> with an average of ≈403.5 cm<sup>-1</sup> and ≈417 cm<sup>-1</sup>, respectively. PL peak map of **i** MoS<sub>2</sub> with an average of ≈1.85 eV and **j** WS<sub>2</sub> with an average of ≈1.97 eV, confirm monolayer films. PL is a characteristic of monolayer film owing to indirect to direct bandgap transition.

for more details on transfer of monolayer films). Following transfer, electron beam (e-beam) lithography and dry etching using SF<sub>6</sub> plasma were used to isolate the channel area of each device. Next, transmission line measurement (TLM) structures were defined using another set of e-beam exposures. Finally, ebeam evaporation was performed to sequentially deposit 40 nm Ni and 30 nm Au to serve as the contacts for the FETs (see "Methods" section for more details on device fabrication). The TLM structures were designed to have channel lengths  $(L_{CH})$  of 100 nm, 200 nm, 300 nm, 400 nm, 500 nm, 1 µm, 2 µm, 3 µm,  $4 \,\mu\text{m}$ , and  $5 \,\mu\text{m}$ , while the channel width (W) was kept constant at 5 µm. Figure 2b, c, respectively, show the schematic and scanning electron microscope (SEM) image of the fabricated TLM structures. Figure 2d-g show the transfer characteristics, i.e., drain current  $(I_{DS})$  versus gate voltage  $(V_{GS})$ , for different drain voltages  $(V_{\rm DS})$  in linear and logarithmic scales for representative longest-channel length ( $L_{CH} = 5 \,\mu m$ ) and shortest-channel length  $(L_{CH} = 100 \text{ nm})$  FETs, for both MoS<sub>2</sub> and WS<sub>2</sub>. Strong n-type conduction is observed due to Fermi-level pinning of the contact metal close to the conduction band of both  $MoS_2$  and  $WS_2^{30}$ . Figure 2h-k show the corresponding output characteristics, i.e.,  $I_{\rm DS}$  versus  $V_{\rm DS}$ , for different  $V_{\rm GS}$ . Measurement protocols are described in the "Methods" section.

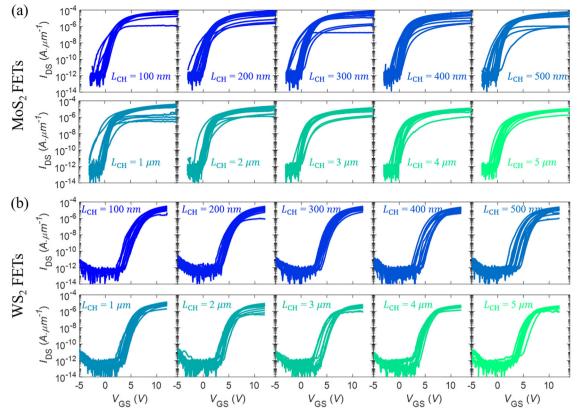

**Device-to-device variation in monolayer MoS<sub>2</sub> and WS<sub>2</sub> FETs.** To understand the variation in the FET performance across the entire  $1 \times 1$  cm<sup>2</sup> substrates, as well as to study of the impact of channel length scaling on FET performance, 230 MoS<sub>2</sub> FETs (23 TLM structures) and 160 WS<sub>2</sub> FETs (16 TLM structures) were measured. Figure 3a, b display the transfer characteristics of all measured MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively, for different  $L_{CH}$ , which were used to extract key device parameters. For each parameter, the mean, median, standard deviation, minimum, and maximum values are reported. Finally, median values are used for benchmarking since they reflect the central tendency, even in the presence of outliers in the data, and offer higher accuracy in case of skewed distributions. Devices with the best number for a given parameter are termed as "champion" devices.

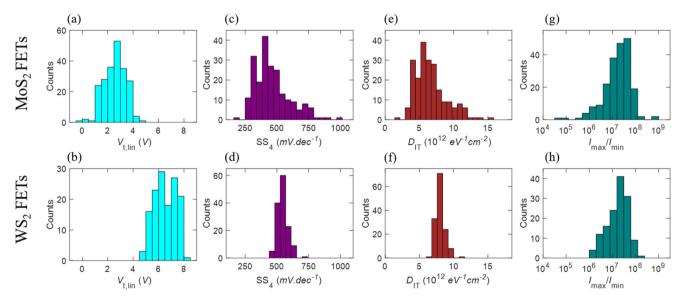

Threshold voltage. Threshold voltage is extracted using three different methods: linear extrapolation  $(V_{t_{in}})$ , Y-function  $(V_{t_y})$ , and constant-current method  $(V_{t_{cc}})$ . Supplementary Fig. 2a-c describes the extraction of  $V_{t_{lin}}$ ,  $V_{t_{Y}}$ , and  $V_{t_{cc}}$ , Supplementary Fig. 2d, e show their corresponding median values as a function of  $L_{\rm CH}$ , and Supplementary Fig. 2f, g show their distributions across all devices for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. Supplementary Note 1 and Supplementary Table 1 summarize the device-to-device variations. It was found that the threshold voltage is independent of the channel length for both MoS<sub>2</sub> and WS<sub>2</sub> FETs. Figure 4a, b show the distributions of  $V_{t_{lin}}$  for all measured MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. Median  $V_{t_{lin}}$  of 2.9 V with a standard deviation of  $\sigma_{V_t} = 0.8$  V is obtained for MoS<sub>2</sub>, and median  $V_{t_{iin}}$  of 6.4 V with a  $\sigma_{V_1} = 0.8$  V is obtained for WS<sub>2</sub>. Threshold voltage was found to be more positive for WS<sub>2</sub> FETs compared to MoS<sub>2</sub> FETs, which can be attributed to higher intrinsic n-type doping of MoS2 either due to the specific nature of the impurity present in the MOCVD grown MoS<sub>2</sub> film or due to surface charge transfer induced

**Fig. 2 Device fabrication and electrical measurements. a** Schematic representation of PMMA-assisted wet transfer of monolayer TMD films from sapphire (growth substrate) to an Al<sub>2</sub>O<sub>3</sub> substrate. **b** Schematic representation and **c** SEM of a TLM structure defined using e-beam lithography. TLM structures with channel length ( $L_{CH}$ ) from 100 nm to 5  $\mu$ m are fabricated and the channel width is defined to be 5  $\mu$ m. Transfer characteristics, i.e., drain current ( $I_{DS}$ ) versus gate voltage ( $V_{GS}$ ), for different drain voltages ( $V_{DS}$ ) in logarithmic and linear scale for **d** longest-channel ( $L_{CH} = 5 \,\mu$ m) and **e** shortest-channel ( $L_{CH} = 100 \,\text{nm}$ ) MoS<sub>2</sub> field-effect transistors (FETs), and **f** longest-channel ( $L_{CH} = 5 \,\mu$ m) and **g** shortest-channel ( $L_{CH} = 100 \,\text{nm}$ ) WS<sub>2</sub> FETs. Corresponding output characteristics, i.e.,  $I_{DS}$  versus  $V_{DS}$ , for different  $V_{GS}$  for **h** longest-channel and **i** shortest-channel MoS<sub>2</sub> FETs, and **j** longest-channel and **k** shortest-channel WS<sub>2</sub> FETs.

doping due to the underlying ALD grown  $Al_2O_3$ . This charge transfer is accredited to the higher conduction band offset between  $MoS_2$  and  $Al_2O_3$  compared to  $WS_2$  and  $Al_2O_3^{31}$ .

Variation in threshold voltage is widely used for benchmarking emerging devices based on novel materials<sup>25</sup>. Note that median  $V_{t_{lin}}$  depends on the work function of the gate metal and unintentional/intrinsic doping of the 2D material and that both  $V_{t_{lin}}$  and  $\sigma_{V_t}$  depend on the thickness of the gate oxide. Hence for a fair comparison we use  $S\sigma_{V_t}$ , which is defined as the projected threshold voltage variation at a scaled effective oxide thickness (SEOT) obtained using Eq. (1). We use SEOT = 0.9 nm for comparison with other literature results.

$$S\sigma_{V_t} = \sigma_{V_t} \frac{\text{SEOT}}{\text{EOT}}$$

(1)

This equation assumes linear scaling of variation in threshold voltage with respect to the EOT. However, for ultra-scaled devices, deviation from the linear scaling can be expected due to increased effect of metal-gate granularity<sup>32</sup>. For our MoS<sub>2</sub> and WS<sub>2</sub> FETs, we project  $S\sigma_{V_t} = 33 \text{ mV}$ , which is similar to the value projected for CVD grown monolayer MoS<sub>2</sub> FETs reported by Smithe et al.<sup>25</sup>. We also employed this method to other reports on top-gated and wafer-scale monolayer MoS<sub>2</sub> FETs and extracted  $S\sigma_{V_t} = 45 \text{ mV}$  for<sup>26</sup> and  $S\sigma_{V_t} = 11 \text{ mV}$  for<sup>12</sup>, respectively. Recently, Smets et al.<sup>7</sup> have demonstrated  $\sigma_{V_t} = 44 \text{ mV}$  for an EOT of 1.9 nm that would correspond to  $S\sigma_{V_t} = 20 \text{ mV}$  for monolayer MoS<sub>2</sub> FETs with channel lengths scaled down to

30 nm. These results are compared with the state-of-the-art UTB SOI and Si FinFET (Table 1). Channel dimensions are included in Table 1 since  $\sigma_{V_1}$  has been found to be inversely proportional to the channel area in ultra-scaled devices which is shown using Pelgrom plots<sup>32,33</sup>. However, we did not observe such a trend due to relatively large channel areas in our MoS<sub>2</sub> and WS<sub>2</sub> FETs. It is encouraging that monolayer 2D FETs show  $S\sigma_{V_{t}}$  comparable to the state-of-the art Si FETs in spite of an order of magnitude smaller body thickness. Note that UTB Si FETs are expected to encounter challenges associated with the precise thickness control, random dopant fluctuations, and detrimental quantum confinement effects beyond 5 nm body thickness<sup>34,35</sup>, which are unlikely for 2D monolayers. At the same time further improvement in threshold voltage variation can be achieved for 2D FETs through optimization of the monolayer growth and improvement in the fabrication process flow (see Supplementary Note 2 for further discussion). Hence, 2D materials offer an alternative for the realization of UTB MOSFETs. The exhibition of low deviceto-device variation in this work, which can be attributed to uniform and contaminant-free MOCVD growth of monolayer TMDs and clean device fabrication process can accelerate the incorporation of 2D FETs in future VLSI technologies.

Subthreshold slope. Subthreshold slope (SS) is extracted over 1 (SS<sub>1</sub>), 2 (SS<sub>2</sub>), 3 (SS<sub>3</sub>), and 4 (SS<sub>4</sub>) orders of magnitude change in  $I_{\text{DS}}$  for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. Supplementary Fig. 3a, b show the median values for SS<sub>1</sub>, SS<sub>2</sub>, SS<sub>3</sub>, and SS<sub>4</sub> as a function of  $L_{\text{CH}}$ , and Supplementary Fig. 3c, d show the distributions for

**Fig. 3 Statistics of scaled devices.** A total of 230 MoS<sub>2</sub> FETs and 160 WS<sub>2</sub> FETs were fabricated using 23 and 16 TLM structures with channel lengths ranging from  $L_{CH} = 100$  nm to  $L_{CH} = 5 \,\mu$ m for **a** MoS<sub>2</sub> and **b** WS<sub>2</sub>, respectively, to analyze the device-to-device variation and impact of scaling on the device performance. The corresponding transfer characteristics, i.e.,  $I_{DS}$  versus  $V_{GS}$ , for  $V_{DS}$  of 1 V are shown in the logarithmic scale.

**Fig. 4 Variation in OFF-state performance.** Histograms showing the variation in threshold voltage extracted using linear extrapolation ( $V_{t,lin}$ ) for **a** MoS<sub>2</sub> and **b** WS<sub>2</sub> FETs. The median values for these extracted threshold voltages were found to be more positive for WS<sub>2</sub> FETs compared to MoS<sub>2</sub> FETs due to higher intrinsic n-type doping of MoS<sub>2</sub>. Histograms of SS extracted across 4 orders of magnitude change in the drain current (SS<sub>4</sub>) for **c** MoS<sub>2</sub> and **d** WS<sub>2</sub> FETs. The deviation of SS from the ideal 60 mV.dec<sup>-1</sup> corresponds to the presence of interface traps. Histograms of interface trap density ( $D_{IT}$ ) for **e** MoS<sub>2</sub> and **f** WS<sub>2</sub> FETs calculated from SS<sub>4</sub>. Histograms of maximum to minimum current ratio ( $I_{max}/I_{min}$ ) for **g** MoS<sub>2</sub> and **h** WS<sub>2</sub> FETs.

$SS_1$  and  $SS_4$  for all  $MoS_2$  and  $WS_2$  devices, respectively. Supplementary Table 2 summarizes the device-to-device variation in SS. For a FET with ohmic contacts, it is expected that  $SS_1 = SS_2 = SS_3 = SS_4$ . However, for a Schottky barrier (SB) FET, the SS may increase when extracted for higher orders of magnitude change in

$I_{\rm DS}$ . A greater increase can be attributed to higher SB height at the metal/semiconductor interface, which not only limits the ON-current but also impacts the OFF-state performance. In the existing 2D FET literature there is a tendency to report SS value without mentioning the orders of magnitude change in  $I_{\rm DS}$  over

|                                                    | $\sigma_{V_t}(V)$       | Gate dielectric                      | $S\sigma_{V_t}(V)$ at SEOT = 0.9 nm | Channel dimensions (µm)                                      |

|----------------------------------------------------|-------------------------|--------------------------------------|-------------------------------------|--------------------------------------------------------------|

| <sup>25</sup> —MoS <sub>2</sub>                    | 1.05                    | 30 nm SiO <sub>2</sub>               | 33 × 10 <sup>-3</sup>               | W = 11.6, L <sub>CH</sub> = 4-8.6                            |

| <sup>26</sup> —MoS <sub>2</sub> 1 continuous layer | 0.25                    | 30 nm HfO <sub>2</sub>               | 45 × 10 <sup>-3</sup>               | W = -, L <sub>CH</sub> = 30                                  |

| $^{26}$ —MoS <sub>2</sub> 1 layer + ML             | 0.1                     | 30 nm HfO <sub>2</sub>               | 19 × 10 <sup>-3</sup>               | $W = -, L_{CH} = 30$                                         |

| <sup>12</sup> —MoS <sub>2</sub>                    | 0.17                    | 30 nm Al <sub>2</sub> O <sub>3</sub> | 11 × 10 <sup>-3</sup>               | $W = 30, L_{CH} = 4$                                         |

| <sup>7</sup> —MoS <sub>2</sub>                     | $44 \times 10^{-3}$     | 4 nm HfO <sub>2</sub>                | 20 × 10 <sup>-3</sup>               | $W = 1, L_{CH} = 0.1$                                        |

| Our work-MoS <sub>2</sub> , WS <sub>2</sub>        | 0.8                     | $50 \text{ nm Al}_2O_3$              | 33 × 10 <sup>-3</sup>               | $W = 5$ , $L_{CH} = 0.1$ , 0.2, 0.3, 0.4, 0.5, 1, 2, 3, 4, 5 |

| 33-UTB SOI                                         | 24.5 × 10 <sup>-3</sup> | EOT = 1.65  nm                       | 13 × 10 <sup>-3</sup>               | $W = 0.060, L_{CH} = 0.025$                                  |

| <sup>32</sup> —FinFET                              | 10 × 10 <sup>-3</sup>   | EOT = 0.8  nm                        | 11 × 10 <sup>-3</sup>               | $W = 0.0075, L_{CH} = 0.034$                                 |

which it is evaluated. This leads to considerable discrepancy and unfair comparisons. In fact, most SS values are reported for only one or two orders of magnitude of the drain current, whereas circuit operations require at least four orders of magnitude ON/ OFF ratio to be technologically relevant.

We found that the median SS values are independent of  $L_{CH}$ for both MoS<sub>2</sub> and WS<sub>2</sub> FETs (Supplementary Fig. 3a, b). Fig. 4c, d show the distributions of SS<sub>4</sub> for all measured MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. A median  $SS_4$  of 431.9 mV.dec<sup>-1</sup> with a standard deviation of  $\sigma_{SS} = 138.1 \text{ mV.dec}^{-1}$  is obtained for MoS<sub>2</sub>, and a median SS<sub>4</sub> of 541.4 mV.dec<sup>-1</sup> with a  $\sigma_{SS} = 41.8$  mV.dec<sup>-1</sup> is obtained for WS<sub>2</sub>. The median SS<sub>4</sub> values show slight increase from the corresponding median SS<sub>1</sub> values of 327.1 mV.dec<sup>-1</sup> and 438.2 mV.dec<sup>-1</sup> for MoS<sub>2</sub> and WS<sub>2</sub>, respectively (Supplementary Table 2). However, no significant difference is found in the standard deviation values for SS1 and SS4. Note that the "champion"  $MoS_2$  FET demonstrates  $SS_1 = 93.3$  mV.dec<sup>-1</sup> and  $SS_4 = 166 \text{ mV.dec}^{-1}$ , and the "champion" WS<sub>2</sub> FET demonstrates  $SS_1 = 295.6 \text{ mV.dec}^{-1}$  and  $SS_4 = 452.8 \text{ mV.dec}^{-1}$ . The deviation of SS from its ideal value of 60 mV.dec<sup>-1</sup>even for "champion" devices can be explained using Eq. (2).

$$SS = \frac{mk_{B}T}{q}\ln(10); m = \left(1 + \frac{C_{S}}{C_{OX}} + \frac{C_{IT}}{C_{OX}}\right); C_{IT} = qD_{IT} \quad (2)$$

Here,  $k_{\rm B}$  is the Boltzmann constant, *T* is the temperature, *q* is the electronic charge, *m* is the body factor,  $C_{\rm S}$  is the semiconductor capacitance,  $C_{\rm TT}$  is the interface trap capacitance,  $C_{\rm OX}$  is the oxide capacitance, and  $D_{\rm TT}$  is the interface trap density. For fully depleted UTB FETs such as monolayer MoS<sub>2</sub> and WS<sub>2</sub> FETs,  $C_{\rm S} = 0$ . In case of a clean oxide-semiconductor interface,  $C_{\rm TT} \ll C_{\rm OX}$ , ensuring that m = 1 and SS = 60 mV.dec<sup>-1</sup>. Clearly, in our MoS<sub>2</sub> and WS<sub>2</sub> FETs, m > 1 indicates the presence of interface traps at the 2D/ dielectric interface (finite value of  $C_{\rm TT}$ ).

Interface traps. To evaluate the quality of the interface, we have extracted  $D_{\rm IT}$  using Eq. (2) and the corresponding distributions are shown in Fig. 4e, f for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. Median  $D_{\rm IT}$  of  $6.2 \times 10^{12} \, {\rm eV^{-1} \, cm^{-2}}$  and  $8 \times 10^{12} \, {\rm eV^{-1} \, cm^{-2}}$ were obtained for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. The device-todevice variation in  $D_{IT}$  is shown in Supplementary Table 2. For fully depleted UTB Si MOSFETs with 35 nm thick Si and 110 nm gate length,  $SS = 80 \text{ mV.dec}^{-1}$  for an EOT = 4 nm, which corresponds to a  $D_{\text{IT}} = 1.5 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-236}$ . Note that, while the D<sub>IT</sub> values for our monolayer 2D FETs are comparable with stateof-the-art Si FETs, thicker EOT = 22 nm results in smaller  $C_{OX}$ and hence higher median values for the SS for MoS2 and WS2 FETs. For a fair comparison, we project the scaled-SS (SSS) for an EOT of 0.9 nm using the  $D_{\rm IT}$ . We found SSS to be 76 mV.dec<sup>-1</sup> and 80 mV.dec<sup>-1</sup> for MoS<sub>2</sub> and WS<sub>2</sub>, respectively, and 64 mV.dec<sup>-1</sup> for the UTB Si MOSFET in ref. 36. A similar exercise was performed for other reports on MoS<sub>2</sub> FETs from the literature and the results are summarized in Table 2. The impact of higher  $D_{\rm IT}$  at the TMD/Al<sub>2</sub>O<sub>3</sub> interface can be mitigated either by scaling the EOT (i.e., increasing  $C_{\rm OX}$ )<sup>37</sup> or by improving the interface (i.e., reducing  $D_{\rm TT}$ ). The presence of structural defects such as sulfur vacancies are known to introduce trap sites which contribute to  $D_{\rm TT}$ . It has been found that  $D_{\rm TT}$  can be reduced by various surface passivation techniques<sup>38,39</sup>. In addition, photoresist residue from the lithography and/or the wet transfer process can cause an increase in  $D_{\rm TT}$ . Therefore it is possible to reduce  $D_{\rm IT}$  through further optimization of growth, post-growth processing, and improvement in fabrication process flow.

Current ON/OFF ratio. Fig. 4g, h show the distribution of the ratio of maximum to minimum current (Imax/Imin) across all  $MoS_2$  and  $WS_2$  FETs, respectively. Here,  $I_{max}$  is the maximum current obtained from the transfer characteristics for  $V_{DS} = 1 \text{ V}$ and  $I_{\min}$  is the average noise floor. Note that the true device current in the OFF-state is beyond the measurement range of the instrument. See Supplementary Fig. 4a, b for the distribution of  $I_{\text{max}}$  and  $I_{\text{min}}$ , Supplementary Fig. 4c, d for the distribution of  $I_{\text{max}}/I_{\text{min}}$  for different  $L_{\text{CH}}$  for MoS<sub>2</sub> and WS<sub>2</sub> FETs, and Supplementary Table 3 for a summary of device-to-device variation in  $I_{\text{max}}/I_{\text{min}}$ . The median and standard deviation for  $I_{\text{max}}/I_{\text{min}}$ were found to be  $2.1 \times 10^7$  and  $5.5 \times 10^7$  for MoS<sub>2</sub> FETs and  $2.1 \times 10^7$  and  $2.6 \times 10^7$  for WS<sub>2</sub> FETs. These values are over an order of magnitude higher than the  $I_{\rm max}/I_{\rm min}$  of  $1.3 \times 10^6$  for UTB Si MOSFETs<sup>36</sup>.  $I_{max}/I_{min}$  is benchmarked against literature reports for  $L_{CH} = 100 \text{ nm}$  as shown in Supplementary Table 4. Note that the key OFF-state performance indicators, i.e., threshold voltage, SS,  $D_{\rm IT}$ , and  $I_{\rm max}/I_{\rm min}$ , are mostly found to be independent of  $L_{CH}$ . Even for  $L_{CH} = 100 \text{ nm}$ , no detrimental short-channel effects are observed, which is expected and can be ascribed to the atomically thin body nature of monolayer TMDs, as well as the use of thin and high-k Al<sub>2</sub>O<sub>3</sub> as the gate dielectric with EOT = 22 nm.

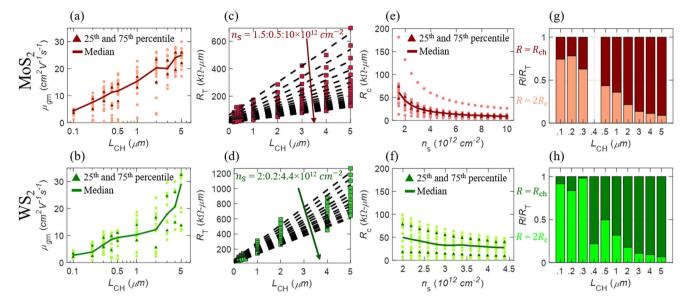

Field-effect mobility and contact resistance. Field-effect mobility  $(\mu_{\rm FE})$  is an important device parameter that strongly influences the ON-state performance of a FET. While intrinsic mobility is a material related parameter,  $\mu_{\rm FE}$  is determined by extrinsic effects, such as contact resistance  $(R_c)$ , and often depends on how it is extracted from the device characteristics. Three popular methods for extracting  $\mu_{FE}$  are peak transconductance ( $\mu_{g_m}$ ), Y-function  $(\mu_Y)^{40}$ , and TLM  $(\mu_{TLM})$  as described in Supplementary Note 3. Figure 5a, b, show the distribution and the corresponding median values for  $\mu_{g_m}$  as a function of  $L_{\rm CH}$  for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. Additionally, 25th and 75th percentile values of the distribution are also marked. Clearly,  $\mu_{q_m}$  shows a strong  $L_{CH}$  dependence, with the median value varying from 23.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> to 3.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for MoS<sub>2</sub> and 29 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> to 2.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for WS<sub>2</sub> as the devices are scaled from  $L_{CH} =$ 5  $\mu$ m down to  $L_{CH} = 100$  nm. Supplementary Fig. 5a, b shows a similar analysis of  $\mu_Y$  for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively and Table 2 Benchmarking median subthreshold slope for  $L_{cu} = 100$  nm.

|                                | SS (mV.dec <sup>-1</sup> ) | EOT (nm) | Gate dielectric                      | $D_{\rm IT}~(10^{12}{ m eV}^{-1}{ m cm}^{-2})$ | SSS (mV.dec $^{-1}$ ) at SEOT = 0.9 nm |  |  |

|--------------------------------|----------------------------|----------|--------------------------------------|------------------------------------------------|----------------------------------------|--|--|

| <sup>7</sup> —MoS <sub>2</sub> | 80                         | 1.9      | 4 nm HfO <sub>2</sub>                | 3.7 × 10 <sup>12</sup>                         | 70                                     |  |  |

| <sup>7</sup> —MoS <sub>2</sub> | 160                        | 2.7      | 8 nm HfO <sub>2</sub>                | 1.3 × 10 <sup>13</sup>                         | 93                                     |  |  |

| <sup>7</sup> —MoS <sub>2</sub> | 200                        | 3.8      | 12 nm HfO <sub>2</sub>               | 1.3 × 10 <sup>13</sup>                         | 93                                     |  |  |

| <sup>7</sup> —MoS <sub>2</sub> | 1350                       | 50       | 50 nm SiO <sub>2</sub>               | 9.2 × 10 <sup>12</sup>                         | 83                                     |  |  |

| Our work-MoS <sub>2</sub>      | 450                        | 22       | 50 nm Al <sub>2</sub> O <sub>3</sub> | 6.3 × 10 <sup>12</sup>                         | 76                                     |  |  |

| Our Work-WS <sub>2</sub>       | 550                        | 22       | 50 nm Al <sub>2</sub> O <sub>3</sub> | 8 × 10 <sup>12</sup>                           | 80                                     |  |  |

| <sup>36</sup> —UTB SOI         | 80                         | 4        | 4 nm SiO <sub>2</sub>                | 1.8 × 10 <sup>12</sup>                         | 64                                     |  |  |

**Fig. 5 Device-to-device variation in field-effect mobility and contact resistance.** Distribution of mobility extracted using peak transconductance ( $\mu_{g_m}$ ) for different channel lengths for **a** MoS<sub>2</sub> and **b** WS<sub>2</sub> FETs. Median, 25th percentile, and 75th percentile is also denoted. Total resistance ( $R_T$ ) versus  $L_{CH}$  for **c** MoS<sub>2</sub> and **d** WS<sub>2</sub> for different carrier concentrations ( $n_s$ ) extracted using a representative TLM structure. The distribution of contact resistance ( $R_c$ ) across multiple TLM structures, extracted from the y-intercepts in **c** and **d**, as a function of  $n_s$  for **e** MoS<sub>2</sub> and **f** WS<sub>2</sub>, respectively. The relative contribution of  $R_c$  and channel resistance ( $R_{ch}$ ) to the total resistance for **g** MoS<sub>2</sub> and **h** WS<sub>2</sub> for different  $L_{CH}$ . In scaled devices, as  $R_{ch}$  scales with the channel length, the contribution of  $R_c$  (note that  $R_c$  is independent of  $L_{CH}$ ), i.e.,  $2R_c/R_T$  is more significant compared to  $R_{ch}/R_T$ .

Supplementary Table 5 summarizes the device-to-device variation in  $\mu_{g_m}$  and  $\mu_Y$ . Both  $\mu_{g_m}$  and  $\mu_Y$  extracted from shorter-channel devices show significant reduction in their median values, indicating the dominant role of  $R_c$  in scaled 2D FETs<sup>6</sup>. The contact resistance is seen as a result of Fermi-level pinning at the metal/TMD contact interface, resulting in a finite SB height<sup>30</sup>. To investigate further, we used the TLM structure shown in Fig. 2c to extract  $R_c$  and evaluate its impact on  $L_{CH}$  scaling as shown in Fig. 5c–f. We used Eq. (3) to extract  $R_c$ .

$$R_{\rm T} = 2R_{\rm c} + R_{\rm ch}; R_{\rm ch} = \frac{L_{\rm CH}}{\mu_{\rm TLM}C_{\rm OX}(V_{\rm GS} - V_{\rm t_{\rm in}})} = \frac{L_{\rm CH}}{qn_{\rm S}\mu_{\rm TLM}};$$

$$n_{\rm S} = \frac{C_{\rm OX}(V_{\rm GS} - V_{\rm t_{\rm in}})}{q}$$

(3)

Here,  $R_{\rm T}$  is the total measured resistance of the FET, and  $R_{\rm ch}$  is the channel resistance, which is directly proportional to  $L_{\rm CH}$  and inversely proportional to the carrier density ( $n_{\rm S}$ ) when the FET is measured in the linear operation regime. However,  $R_{\rm c}$  is independent of  $L_{\rm CH}$  and hence can be extracted from the y-intercept of  $R_{\rm T}$  versus  $L_{\rm CH}$  plots, as shown in Fig. 5c, d for MoS<sub>2</sub> and WS<sub>2</sub>, respectively, for different  $n_{\rm S}^{\rm 41}$  (see Supplementary Note 4 for further discussion on the extraction of  $n_{\rm S}$ ). Figure 5e, f show the distribution of corresponding extracted  $R_{\rm c}$  as a function of  $n_{\rm S}$ . A steady decrease in  $R_{\rm c}$  with increasing  $n_{\rm S}$  is attributed to the phenomenon of contact-gating in global back-gated FET geometry, since the SB width at the metal/2D interface is modulated by the back-gate voltage<sup>30</sup>. Lower SB width allows for easier carrier tunneling, reducing  $R_c$ . For the MoS<sub>2</sub> FET, the median  $R_c$ value was found to be 9.2 k $\Omega$ -µm, corresponding to  $n_S = 1 \times$  $10^{13}$  cm<sup>-2</sup>. However, for WS<sub>2</sub>,  $n_S$  was limited to  $4.4 \times 10^{12}$  cm<sup>-2</sup>, owing to the more positive  $V_{t_{lin}}$ , resulting in a higher median  $R_c = 29.2$  k $\Omega$ -µm. For a case of identical carrier concentration,  $n_S = 2.7 \times 10^{12}$  cm<sup>-2</sup>, similar median  $R_c$  values of 33 k $\Omega$ -µm and 39.4 k $\Omega$ -µm are obtained for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. The difference in  $R_c$  between MoS<sub>2</sub> and WS<sub>2</sub> can be explained from the fact that the charge neutrality level is closer to the conduction band for MoS<sub>2</sub> than it is for WS<sub>2</sub>, resulting in a higher SB height at the Ni/WS<sub>2</sub> contact interface compared to the Ni/MoS<sub>2</sub> contact interface<sup>42</sup>.

The relative effect of  $R_c$  is assessed for different  $L_{CH}$ . Figure 5g, h show the contribution of  $R_c$  and  $R_{ch}$  to the total resistance  $R_T$ using stacked bar plots as a function of  $L_{CH}$  for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. It is clear that for  $L_{CH} \leq 1 \mu m$ , the contact effects are significant since  $2R_c > R_{ch}$ . This explains why the extracted  $\mu_{g_m}$  is  $L_{CH}$  dependent and is severely underestimated by more than 80% for both MoS<sub>2</sub> and WS<sub>2</sub> when extracted from scaled devices with  $L_{CH} = 100 \text{ nm}$ . Since  $\mu_{g_m}$  extraction is limited by  $R_c$ , extracting  $\mu_{TLM}$  following Eq. (3) is more appropriate for short channel devices. Supplementary Fig. 5c, d show the distribution of  $\mu_{TLM}$

| parentheses).                                     |                                                          |                              |                                                    |                                  |

|---------------------------------------------------|----------------------------------------------------------|------------------------------|----------------------------------------------------|----------------------------------|

|                                                   | $\mu$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | <b>R</b> c(k $\Omega-\mu$ m) | <i>Ι</i> οΝ(μΑ.μm <sup>−1</sup> )                  | <i>n</i> s(cm <sup>-2</sup> )    |

| <sup>25</sup> —MoS <sub>2</sub>                   | $\mu_{a_{-}} = 42 (34.2)$                                | 0.73 (1)                     | 22, $L_{CH} = 5.4 \mu m$                           | 1.3 × 10 <sup>13</sup>           |

| <sup>22</sup> —MoS <sub>2</sub>                   | $\mu_{\text{TLM}} = 20$                                  | 6.5                          | 270, <i>L</i> <sub>CH</sub> = 80 nm                | 1 × 10 <sup>13</sup>             |

| <sup>12</sup> —MoS <sub>2</sub>                   | $\mu_{q_m} = 80 \; (\approx 40)$                         | 2.4                          | 13, $L_{CH} = 4  \mu m$                            | 6.6 × 10 <sup>12</sup>           |

| <sup>65</sup> —MoS <sub>2</sub>                   | $\mu_{\text{TLM}} = 30$                                  | 1.7                          | 260, <i>L</i> <sub>CH</sub> = 10 nm                | 4.7 × 10 <sup>13</sup>           |

| <sup>7</sup> —MoS <sub>2</sub>                    | $\mu_{\text{TLM}} = 15$                                  | 1                            | 250, $L_{CH} = 29 \text{ nm}$                      | 1.5 × 10 <sup>13</sup>           |

| <sup>26</sup> —MoS <sub>2</sub>                   | $\mu_{4-\text{point}} \approx 75$ (70)                   | 14                           | -                                                  | -                                |

| Our work-MoS <sub>2</sub>                         | $\mu_{\rm TLM} = 47$ (27)                                | 3(9.2)                       | 73 (54), <i>L</i> <sub>CH</sub> = 100 nm           | 1 × 10 <sup>13</sup>             |

| <sup>64</sup> —WS <sub>2</sub>                    | $\mu_{g_{\mathrm{m}}} = 11$                              | -                            | 25, $L_{CH} = 4 \mu m$                             | 2.1 × 10 <sup>13</sup>           |

| 47—WS <sub>2</sub>                                | $\mu_{g_{\rm m}} = 20.4$                                 | -                            | 0.6, $L_{CH} = 1  \mu m$                           | 2.5 × 10 <sup>12</sup>           |

| <sup>50</sup> —WS <sub>2</sub>                    | $\mu_{q_m} = 5$                                          | -                            | $\approx$ 0.05, <i>L</i> <sub>CH</sub> = 10 µm     | $\approx$ 7.2 × 10 <sup>12</sup> |

| <sup>50</sup> —WS <sub>2</sub> (Graphene contact) | $\mu_{q_m} = 50$ (27)                                    | -                            | $\approx$ 1.1, <i>L</i> <sub>CH</sub> = 10 µm      | $\approx$ 7.2 × 10 <sup>12</sup> |

| Our work-WS <sub>2</sub>                          | $\mu_{TLM} = 33$ (16)                                    | 2.1 (29)                     | 26 (17), L <sub>CH</sub> = 100 nm                  | 4.4 × 10 <sup>12</sup>           |

| <sup>51</sup> —UTB SOI                            | $\mu_{4-\text{point}} = 6$                               | -                            | $\approx 35 \times 10^{-3}$ , $L_{CH} = 100 \mu m$ | ≈9×10 <sup>12</sup>              |

Table 3 Benchmarking ON-state performance at  $V_{DS} = 1 V$  (best values are compared with median/mean values shown within parentheses).

across MoS<sub>2</sub> and WS<sub>2</sub> TLM structures, respectively, and Supplementary Table 6 summarizes the variation across the different TLM structures. The extracted median value for  $\mu_{\text{TLM}}$ was found to be 27 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. Long channel devices are less vulnerable to  $R_c$  and corresponding  $\mu_{g_m}$  values are more accurate representations of intrinsic channel mobility, albeit with some challenges as described by Nasr et al.<sup>43</sup>. Nevertheless, our "champion" long-channel MoS<sub>2</sub> and WS<sub>2</sub> FETs with  $L_{\text{CH}} = 5 \,\mu\text{m}$ demonstrated  $\mu_{g_m} = 30 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$  and  $33 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$ , respectively. Similarly, "champion" MoS<sub>2</sub> and WS<sub>2</sub> TLM structures demonstrated  $\mu_{\text{TLM}} = 46 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$  and  $33 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$ , respectively.

Table 3 shows the benchmarking of our "champion" devices with the best reports from the literature using  $\mu_{\text{FE}}$  ( $\mu_{g_m}$  for longer channel devices and  $\mu_{TLM}$  for shorter channel devices) and  $R_c$  for both MoS<sub>2</sub> and WS<sub>2</sub>. We have also included median/mean values wherever applicable. Note that while higher  $\mu_{\rm FE}$  values have been reported based on "champion" exfoliated and CVD grown MoS<sub>2</sub> FETs<sup>7,12,24,25,44-46</sup>, our report is statistically more significant as it demonstrates variation across multiple TLM structures. For WS<sub>2</sub>,  $\mu_{\rm FE} = 33 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  is the highest reported, 1.5X better than the previous report on synthetic  $WS_2^{47}$ . Higher  $\mu_{FE}$  values reported for WS<sub>2</sub> are either for exfoliated materials at room temperature<sup>48</sup> and low temperatures<sup>49</sup>, or for CVD grown materials with contact engineering via the use of multilayer graphene as interlayers<sup>50</sup>. More interestingly, UTB Si MOSFETs with 0.9 nm thick Si show  $\mu_{FE} \approx 6 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-151}$ , which is more than 2 orders of magnitude smaller compared to bulk Si mobility and is primarily attributed to thickness fluctuation in UTB Si.

Metal/2D contact resistances are comparatively high even for the "champion" devices with  $R_c = 3 \text{ k}\Omega - \mu \text{m}$  and  $R_c =$ 2.1 k $\Omega - \mu \text{m}$  for MoS<sub>2</sub> and WS<sub>2</sub>, respectively, when compared to the  $R_c = 0.1 \text{ k}\Omega - \mu \text{m}$  typically reported for state-of-the-art Si FETs. However, various methods have been developed to reduce the effect of SB-limited carrier transport in 2D TMDs<sup>52</sup>, such as work function engineering to reduce the SB height<sup>30</sup>, introduction of interlayers such as graphene to decouple the metal/2D interface to alleviate Fermi-level pinning<sup>53,54</sup>, and achieving higher carrier concentration underneath or near the metal/2D contacts through substitutional or surface charge transfer doping to reduce the SB width<sup>42,55</sup>. Nevertheless, our MOCVD grown monolayer MoS<sub>2</sub> FETs demonstrate  $R_c$  similar to values reported in the literature<sup>7,22,25,56</sup>. The "champion" devices are benchmarked in Table 3. To the best of our knowledge, this is the first report of  $R_c$  for synthetic WS<sub>2</sub>. Additionally, our work marks the first study on the extraction of contact resistance from multiple TLM structures for both MoS<sub>2</sub> and WS<sub>2</sub>. Smithe et al.<sup>25</sup> have demonstrated a pseudo-TLM analysis where independent devices with different channel lengths and widths were used to extract the distribution of  $R_T$ . TLM analysis is done on the devices between 10th and 90th percentile<sup>25</sup>. Our demonstration involves the extraction of contact resistance from separate TLM structures and finding the variation across these TLM structures, and the analysis is not limited to a percentile limit.

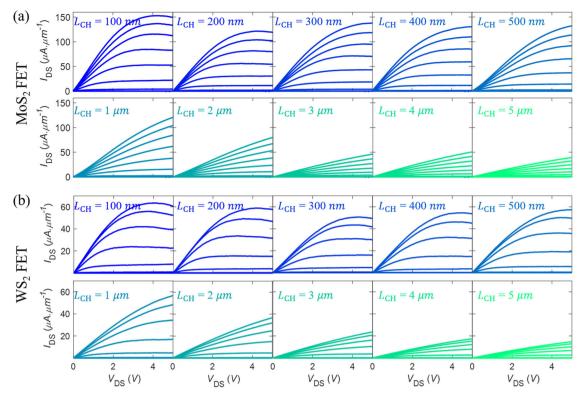

Drive-current and saturation velocity. Finally, high performance FETs are benchmarked using the drive current  $(I_{ON})$  that is achievable for a given supply voltage ( $V_{DS} = V_{DD}$ ). Higher values of  $I_{\rm ON}$  ensure faster circuit operation as the intrinsic delay of a FET is proportional to  $CV_{DD}/I_{ON}$ , where C is the load capacitance. In digital electronics, higher ION allows larger fan-out. Figure 6a, b display the output characteristics of MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively, for different channel lengths, which were used to assess the ON-state performance of the devices. At high biases, high current density leads to self-heating, resulting in negative differential resistance (NDR) behavior. This is a common phenomenon seen in ultra-thin body FETs, including SOI FETs<sup>57</sup>, nanowire FETs<sup>58</sup>, graphene FETs<sup>59</sup>, and, more recently, exfoliated multilayer MoS<sub>2</sub> FETs<sup>60</sup> and CVD grown monolayer MoS<sub>2</sub> FETs<sup>61</sup>. It is possible to reduce or eliminate the self-heating effect through pulsed measurements with pulse widths less than 100 μs<sup>60</sup>.

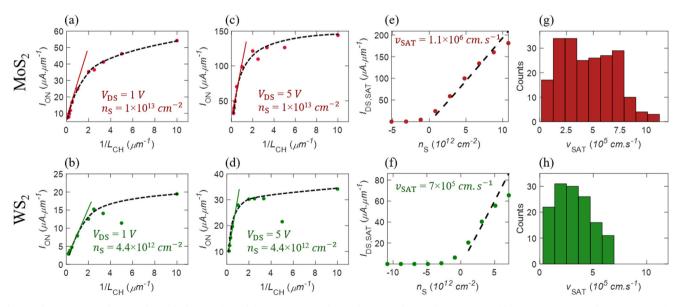

Figure 7a-d show the median for  $I_{\rm ON}$  as a function of  $L_{\rm CH}$  for  $V_{\rm DS} = 1$  V and  $V_{\rm DS} = 5$  V for MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively, extracted from their respective output characteristics. For both TMDs, at low  $V_{\rm DS} = 1$  V, i.e., in the linear region,  $I_{\rm ON}$  is expected to demonstrate an inverse channel length dependence following Eq. (4).

$$\frac{I_{\rm ON}}{W} = \frac{I_{\rm DS,LIN}}{W} = q n_{\rm S} \mu_{g_{\rm m}} \frac{V_{\rm DS}}{L_{\rm CH}} \tag{4}$$

This trend is observed for both MoS<sub>2</sub> and WS<sub>2</sub> FETs in Fig. 7a, b, respectively, for channel lengths  $L_{CH} \ge 1 \,\mu\text{m}$ . However, for devices with channel length  $L_{CH} < 1 \,\mu\text{m}$ , the inverse channel length dependence is obscured by  $R_c$ . Similar linear dependence is observed for  $I_{ON}$  in longer-channel devices ( $L_{CH} \ge 1 \,\mu\text{m}$ ) at

**Fig. 6 ON-state performance of monolayer MoS<sub>2</sub> and WS<sub>2</sub> FETs.** Output characteristics for channel lengths ranging from  $L_{CH} = 100$  nm to  $L_{CH} = 5 \mu$ m, obtained from a representative transmission-line measurement structure for **a** MoS<sub>2</sub> and **b** WS<sub>2</sub> FETs. Current saturation is achieved in shorter-channel devices for both MoS<sub>2</sub> and WS<sub>2</sub> FETs.

**Fig. 7 Drive current and saturation velocity.** Median of drive current ( $I_{ON}$ ) as a function of  $1/L_{CH}$  for **a** MoS<sub>2</sub> and **b** WS<sub>2</sub> FETs at  $V_{DS}$  of 1 V corresponding to the linear region of the FETs, and **c** MoS<sub>2</sub> and **d** WS<sub>2</sub> FETs at  $V_{DS}$  of 5 V corresponding to the saturation region of the FETs. These are extracted at carrier concentrations ( $n_S$ ) of 1 × 10<sup>13</sup> cm<sup>-2</sup> and 4.4 × 10<sup>12</sup> cm<sup>-2</sup> for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. The saturation current ( $I_{DS,SAT}$ ) for **e** MoS<sub>2</sub> and **f** WS<sub>2</sub>, extracted from their corresponding shorter-channel devices ( $L_{CH} < 1 \mu m$ ) as a function of  $n_S$ . The slope indicates the saturation velocity ( $v_{SAT}$ ). The distribution of  $v_{SAT}$  for **g** MoS<sub>2</sub> and **h** WS<sub>2</sub> shorter-channel FETs.

$V_{\rm DS} = 5$  V for both MoS<sub>2</sub> and WS<sub>2</sub> FETs in Fig. 7c, d, respectively, following Eq. (5).

$$\frac{I_{\rm ON}}{W} = \frac{I_{\rm DS,SAT}}{W} = \frac{C_{\rm OX}\mu_{g_{\rm m}}(V_{\rm GS} - V_{\rm t_{\rm in}})^2}{2L_{\rm CH}} = \frac{q^2\mu_{g_{\rm m}}}{C_{\rm OX}}\frac{n_{\rm S}^2}{2L_{\rm CH}}$$

(5)

These results are in accordance with classic long-channel FET characteristics (i.e., at low drain bias, the device operates in the

linear regime (Eq. (4)), whereas for  $V_{\rm DS} \ge V_{\rm GS} - V_{\rm t_{lin}}$ , the channel is pinched-off, resulting in current saturation). The saturation current follows a square-law dependence on the overdrive voltage and, therefore, on  $n_{\rm S}$  (Eq. (6))<sup>62</sup>. In shorter-channel devices  $(L_{\rm CH} < 1 \,\mu{\rm m})$ , as the lateral electric field ( $\xi \approx \frac{V_{\rm DS}}{L_{\rm CH}}$ ) becomes more than the critical electric field ( $E_{\rm C}$ ), the carrier velocity reaches saturation velocity ( $v_{\text{SAT}}$ ). This leads to current saturation, with the saturation current being independent of  $L_{\text{CH}}$  as described by Eq. (6)<sup>62</sup>.

$$\frac{I_{\rm ON}}{W} = \frac{I_{\rm DS,SAT}}{W} = C_{\rm OX} \nu_{\rm SAT} \left( V_{\rm GS} - V_{\rm t_{lin}} \right) = q n_{\rm S} \nu_{\rm SAT} \qquad (6)$$

However, in order to observe current saturation due to velocity saturation, the drain bias must meet the criterion given by Eq. (7).

$$L_{\rm CH} \frac{\nu_{\rm SAT}}{\mu_{g_{\rm m}}} < V_{\rm DS} < \left( V_{\rm GS} - V_{\rm t_{\rm lin}} = \frac{q n_{\rm S}}{C_{\rm OX}} \right)$$

(7)

For example, as seen in Fig. 6, current saturation is achieved at  $V_{\rm DS} = 4 \text{ V}$  for 100 nm MoS<sub>2</sub> FET and WS<sub>2</sub> FET, which is much lower than the corresponding  $V_{\rm GS} - V_{\rm t_{\rm lin}}$  of 11.6 V and 6.7 V, respectively. This explains why the drive current in shorterchannel MoS<sub>2</sub> and WS<sub>2</sub> FETs display little-to-no channel length dependence for high drain bias ( $V_{\rm DS} = 5$  V), as seen in Fig. 7c, d. Nevertheless, scaled MoS<sub>2</sub> and WS<sub>2</sub> FETs with channel lengths of 100 nm demonstrate high median drive currents of  $I_{ON} = 54 \,\mu\text{A}$ .  $\mu m^{-1}$  and  $I_{ON} = 17 \,\mu A.\mu m^{-1}$ , respectively, for  $V_{DS} = 1 \,\text{V}$  and  $I_{\rm ON} = 146 \,\mu A.\mu m^{-1}$  and  $I_{\rm ON} = 30 \,\mu A.\mu m^{-1}$ , respectively, for  $V_{\rm DS} = 5$  V. Furthermore,  $I_{\rm ON}$  at  $V_{\rm DS} = 5$  V can reach as high as 161  $\mu$ A. $\mu$ m<sup>-1</sup> and 53  $\mu$ A. $\mu$ m<sup>-1</sup> in "champion" MoS<sub>2</sub> and WS<sub>2</sub> FETs, respectively. The distribution of  $I_{ON}$  for  $V_{DS} = 1 \text{ V}$  and  $V_{\rm DS} = 5$  V as a function of  $L_{\rm CH}$  is shown in Supplementary Fig. 6 and the corresponding device-to-device variation is summarized in Supplementary Table 7 for MoS<sub>2</sub> and WS<sub>2</sub> FETs. The higher drive current seen for MoS<sub>2</sub> FETs compared to that of WS<sub>2</sub> FETs is a direct consequence of lower  $V_{t_{lin}}$ , which allows for higher  $n_S$ in MoS<sub>2</sub> channels. Further improvement in the drive current of scaled 2D FETs can be achieved by reducing  $R_c$ . Note that, while there are reports of higher ION in large-area grown MoS2 films, none of the earlier studies provide extensive device statistics<sup>22,63-65</sup>.  $I_{ON}$  for UTB Si MOSFET is 35 nA.µm<sup>-1</sup> for 0.9 nm thick Si<sup>51</sup>. The "champion" devices are benchmarked in Table 3. Supplementary Table 8 shows benchmarking of our statistical study on MoS<sub>2</sub> FETs using field-effect mobility and drive current (at  $V_{DS} = 2 \text{ V}$ ) with similar channel length dependent statistical studies from the literature. The mean and standard deviation is compared with the  $L_{CH}$  dependence and plotted in Supplementary Fig. 7. Better performance is seen for our channel length dependence study compared to ref. <sup>66</sup> for both the drive current and mobility.

Finally, saturation velocity ( $v_{SAT}$ ) is another key material parameter that determines I<sub>ON</sub> in scaled FETs. This is because at low lateral electric field ( $\xi$ ) the average electron drift velocity increases linearly through the mobility ( $v_d = \mu_{FE}\xi$ ), but at large electric fields, which are easily achievable in sub-micron FETs, the carrier velocity saturates. Thus, ION becomes less dependent on  $\mu_{\rm FE}$  and is instead proportional to  $v_{\rm SAT}$ , following Eq. (6). Additionally, high  $v_{SAT}$  is needed for faster switching<sup>11</sup>. Figure 7e-h show the extraction of  $v_{SAT}$  and the distribution of  $v_{\text{SAT}}$  for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. The linear dependence of the saturation current  $(I_{DS,SAT})$  on  $n_S$  following Eq. (6), is used to extract  $v_{\text{SAT}}$ . Median  $v_{\text{SAT}}$  values of  $6.4 \times 10^5$  cm.s<sup>-1</sup> and  $4 \times 10^5$ cm.s<sup>-1</sup> and "champion"  $v_{\rm SAT}$  values of  $1.1 \times 10^6$  cm.s<sup>-1</sup> and  $6.9 \times$  $10^5 \text{ cm.s}^{-1}$  are obtained for MoS<sub>2</sub> and WS<sub>2</sub>, respectively. The corresponding device-to-device variations are summarized in Supplementary Table 9. The  $v_{SAT}$  values are significantly lower compared to bulk Si with  $v_{SAT} \approx 10^7 \text{ cm.s}^{-167,68}$ . Nathawat et al. have reported higher  $v_{SAT} \approx 6 \times 10^6 \text{ cm.s}^{-1}$  in CVD grown monolayer MoS<sub>2</sub><sup>69</sup>. However, their measurements were done using nanosecond range pulses to reduce the impact of selfheating and hot carrier capture by deep oxide traps. For WS<sub>2</sub>, this is the first report of  $v_{\text{SAT}}$ .

#### Discussion

In conclusion, we have performed a detailed study of device-todevice variation and impact of channel length scaling on the electrical parameters, such as threshold voltage, subthreshold slope, density of interface trap states, ratio of minimum to maximum current, field-effect electron mobility, drive current, contact resistance, and saturation velocity, of MOCVD grown MoS<sub>2</sub> and WS<sub>2</sub> monolayer based FETs using statistical measures such as median, mean, standard deviation, and minimum/maximum values and have benchmarked our findings against other similar reports from 2D literature as well as UTB Si FETs. While in absolute terms the spatial variations in the respective benchmarking parameters appear to be large for MoS<sub>2</sub> and WS<sub>2</sub> FETs, when compared at scaled oxide thickness, our results are not significantly different from the projected variations for UTB Si FETs. Our "champion" long-channel MoS<sub>2</sub> and WS<sub>2</sub> FETs with  $L_{\rm CH} = 5 \,\mu {\rm m}$  demonstrated electron mobilities of  $30 \,{\rm cm}^2 \,{\rm V}^{-1} \,{\rm s}^{-1}$ and  $33 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , respectively, when extracted using peak transconductance and  $46 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $33 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , respectively, when extracted using TLM method. For synthetic monolayer WS<sub>2</sub> films, these are the highest reported room temperature electron mobilities, 1.5X better than the best report from the literature. Similarly, our "champion" shortest channel length MoS<sub>2</sub> and WS<sub>2</sub> FETs, with  $L_{CH} = 100$  nm, demonstrated drive currents as high as 161  $\mu$ A. $\mu$ m<sup>-1</sup> and 53  $\mu$ A. $\mu$ m<sup>-1</sup> for  $V_{DS} = 5$  V at carrier densities of  $n_{\rm S} = 1 \times 10^{13}$  cm<sup>-2</sup> and  $4.4 \times 10^{12}$  cm<sup>-2</sup>, respectively, in spite of the presence of high contact resistances. We attribute our accomplishments to the epitaxial growth of highly crystalline 2D monolayers on sapphire substrate via MOCVD at 1000 °C using chalcogen and sulfur precursors that minimize carbon contamination in the film, as well as to the clean transfer of the film from the growth substrate to the device fabrication substrate. Our findings suggest that 2D FETs are promising alternatives for future VLSI circuits.

#### Methods

**MOCVD growth**. Uniform monolayer deposition was achieved in a cold-wall horizontal reactor with an inductively heated graphite susceptor equipped with wafer rotation as previously described<sup>27</sup>. Molybdenum hexacarbonyl (Mo(CO)<sub>6</sub>) and tungsten hexacarbonyl (W(CO)<sub>6</sub>) were used as metal precursors while hydrogen sulfide (H<sub>2</sub>S) was the chalcogen source with H<sub>2</sub> as the carrier gas. Mo (CO)<sub>6</sub> maintained at 10 °C and 950 Torr in a stainless-steel bubbler was used to deliver 0.036 *sccm*. W(CO)<sub>6</sub> maintained in a bubbler at 10 °C and 760 Torr delivered  $6.4 \times 10^{-4}$  sccm. The flow rate of H<sub>2</sub>S was 400 sccm and the reactor pressure was 50 Torr for both sulfides. MoS<sub>2</sub> was deposited in a single step process at 1000 °C where coalesced monolayer growth across the 2″ wafer was achieved in 18 min. WS<sub>2</sub> was deposited using a multi-step process with nucleation at 850 °C and lateral growth at 1000 °C, which resulted in coalesced monolayer growth across the 2″ wafer in 10 min<sup>28</sup>. In both cases, after growth, the substrate was cooled in H<sub>2</sub>S to 300 °C to inhibit decomposition of the MoS<sub>2</sub> and WS<sub>2</sub> films.

**Material characterization**. A Bruker Icon atomic force microscope was used to measure surface morphology and film thickness. Scanasyst AFM tips with a nominal tip radius of  $\approx 2$  nm and spring constant of  $0.4 \text{ Nm}^{-1}$  were used in the peak-force tapping mode for the measurements. Photoluminescence (PL) maps were acquired over a  $5 \times 5 \,\mu\text{m}^2$  area with a laser wavelength of 532 nm and 300 grooves per mm grating in a WITec apyron Confocal Raman Microscope. A PANalytical MRD diffractometer with a 5-axis cradle was used for in-plane X-ray diffraction characterization of the sulfide films<sup>70</sup>. A Cu anode X-ray tube operated at 40 kV accelerating voltage and 45 mA filament current was used as the X-ray source. On the primary beam side, a mirror with  $\frac{1}{9}^{\circ}$  slit and Ni filter were used to filter the Cu Ka line. On the diffracted beam side, an  $0.27^{\circ}$  parallel plate collimator with 0.04 rad Soller slits with PIXcell detector in open detector mode were employed. To determine the in-plane epitaxial relation of the film with respect to a substrate, sample surface was  $\approx 2-4^{\circ}$  away from the X-ray incidence plane.

**Transfer of monolayer films.** Both the  $MoS_2$  and  $WS_2$  films were grown on 2" sapphire wafers. The 2" sapphire wafers were then cut into  $1 \times 1$  cm<sup>2</sup> pieces. For each material, two (2)  $1 \times 1$  cm<sup>2</sup> sapphire substrates were chosen, one corresponding to the center and another one corresponding to the edge of the 2-inch wafer. To fabricate the FETs, monolayer  $MoS_2$  and  $WS_2$  films grown on sapphire

substrates were transferred onto  $1\times1\,{\rm cm}^2$  device fabrication substrates, i.e., 50 nm Al\_2O\_3 on Pt/TiN/p^++-Si, using a PMMA (polymethyl-methacrylate) -assisted wet transfer process. First, the sapphire substrate with the monolayer film was spin coated with PMMA and then baked at 180 °C for 90 s. The corners of the spin coated films were scratched using a razor blade and immersed inside a 1 M NaOH solution kept at 90 °C. Capillary action drew NaOH into the substrate/film interface, separating the PMMA/monolayer film stack from the sapphire substrate. The separated film was then rinsed multiple times inside a water bath and finally transferred onto the 50 nm alumina substrate and baked at 50 °C and 70 °C for 10 min each to remove moisture and residual PMMA, ensuring a pristine interface.

**Gate dielectric fabrication**. Direct replacement of thermally oxidized SiO<sub>2</sub> with a high- $\kappa$  dielectric such as Al<sub>2</sub>O<sub>3</sub> grown *via* atomic layer deposition (ALD) is a logical choice to scale the EOT. However, we found that a Al<sub>2</sub>O<sub>3</sub>/p<sup>++</sup>-Si interface is not ideal for back gated FET fabrication owing to higher gate leakage current, more interface trap states, and large hysteresis, all of which negatively impact the performance of the device. Replacing Si with Pt, a large work function metal (5.6 eV) allows for minimal hysteresis and trap state effects<sup>71</sup>. Since Pt readily forms a Pt silicide at temperatures as low as 300 °C, a 20 nm TiN diffusion barrier deposited by reactive sputtering was placed between the p<sup>++</sup> Si and the Pt, permitting subsequent high temperature processing<sup>72</sup>. This conductive TiN diffusion barrier allows the back-gate voltage to be applied to the substrate, thus simplifying the fabrication and measurement procedures. The polycrystalline Pt introduces very little surface roughness to the final Al<sub>2</sub>O<sub>3</sub> surface, with a rms roughness of 0.7 nm.

**Device fabrication**. Back gated field-effect transistors (FET) are fabricated using ebeam lithography. To define the channel region the substrate is spin coated with PMMA and baked at 180 °C for 90 s. The photoresist is then exposed to e-beam and developed using 1:1 mixture of 4-methyl-2-pentanone (MIBK) and 2 propanol (IPA). The monolayer MoS<sub>2</sub> film is subsequently etched using sulfur hexafluoride (SF<sub>6</sub>) at 5 °C for 30 s. Next the sample is rinsed in acetone and IPA to remove the photoresist. In order to fabricate the source/drain contacts the substrate is again spin coated with MMA and PMMA followed by the e-beam lithography, developed using MIBK and IPA, and e-beam evaporation of 40 nm Ni/30 nm Au stack. Finally, the photoresist is rinsed away by lift off process using acetone and IPA.

**Electrical characterization**. Lake Shore CRX-VF probe station and Keysight B1500A parameter analyzer were used to perform the electrical characterization at room temperature in high vacuum ( $\approx 10^{-6}$  Torr). Standard DC sweeps are used for the measurements of transfer and output characteristics of all devices. To ensure that the FETs are stabilized, they are conditioned by multiple repetitions of the same measurement. The transfer characteristics are measured three times to condition each FET and the fourth measurement is used for the analysis. The output characteristics are measured twice following the transfer characteristics and the second measurement is used for the analysis. We have found that no burn-in procedure is needed to ensure proper contact formation. Both MoS<sub>2</sub> and WS<sub>2</sub> FETs were measured.

**Reporting summary**. Further information on research design is available in the Nature Research Reporting Summary linked to this article.

#### Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding authors on reasonable request.

#### Code availability

The codes used for plotting the data are available from the corresponding authors on reasonable request.

Received: 27 July 2020; Accepted: 17 December 2020; Published online: 29 January 2021

#### References

- 1. Bhimanapati, G. R. et al. Recent advances in two-dimensional materials beyond graphene. *ACS Nano* **9**, 11509–11539 (2015).

- Das, S., Robinson, J. A., Dubey, M., Terrones, H. & Terrones, M. Beyond graphene: progress in novel two-dimensional materials and van der Waals solids. *Annu. Rev. Mater. Res.* 45, 1–27 (2015).

- Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS<sub>2</sub> transistors be? *Nano Lett.* 11, 3768–3773 (2011).

- Majumdar, K., Hobbs, C. & Kirsch, P. D. Benchmarking transition metal dichalcogenide MOSFET in the ultimate physical scaling limit. *IEEE Electron Device Lett.* 35, 402–404 (2014).

- 5. Alam, K. & Lake, R. K. Monolayer MoS<sub>2</sub> transistors beyond the technology road map. *IEEE Trans. Electron Devices* **59**, 3250–3254 (2012).

- English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. *Nano Lett.* 16, 3824–3830 (2016).

- Smets, Q. et al. Ultra-scaled MOCVD MoS<sub>2</sub> MOSFETs with 42 nm contact pitch and 250 μA/μm drain current. *IEEE International Electron Devices Meeting* 23.2.1–23.2.4 (2019).

- Tosun, M. et al. High-gain inverters based on WSe<sub>2</sub> complementary fieldeffect transistors. ACS Nano 8, 4948–4953 (2014).

- Yu, L. et al. High-performance WSe<sub>2</sub> complementary metal oxide semiconductor technology and integrated circuits. *Nano Lett.* 15, 4928–4934 (2015).

- Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS<sub>2</sub>. ACS Nano 5, 9934–9938 (2011).

- Sanne, A. et al. Radio frequency transistors and circuits based on CVD MoS<sub>2</sub>. Nano Lett. 15, 5039-5045 (2015).

- Yu, L. et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS<sub>2</sub> circuits with E-mode FETs for large-area electronics. *Nano Lett.* 16, 6349–6356 (2016).

- Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. *Nat. Commun.* 8, 14948 (2017).

- Sebastian, A., Pannone, A., Radhakrishnan, S. S. & Das, S. Gaussian synapses for probabilistic neural networks. *Nat. Commun.* 10, 4199 (2019).

- Das, S. Two dimensional electrostrictive field effect transistor (2D-EFET): A sub-60 mV/decade Steep slope device with high ON current. *Sci. Rep.* 6, 34811 (2016).

- Schaibley, J. R. et al. Valleytronics in 2D materials. Nat. Rev. Mater. 1, 16055 (2016).

- 17. Das, S., Dodda, A. & Das, S. A biomimetic 2D transistor for audiomorphic computing. *Nat. Commun.* **10**, 3450 (2019).

- Lee, C. W., Suh, J. M. & Jang, H. W. Chemical sensors based on twodimensional (2D) materials for selective detection of ions and molecules in LIQuid. *Front. Chem.* 7, 708 (2019).

- Dodda, A. et al. Stochastic resonance in MoS<sub>2</sub> photodetector. *Nat. Commun.* 11, 4406 (2020).

- Jayachandran, D. et al. A low-power biomimetic collision detector based on an in-memory molybdenum disulfide photodetector. *Nat. Electron.* 3, 646–655 (2020).

- Nasr, J. R. et al. Low-power and ultra-thin MoS<sub>2</sub> photodetectors on glass. ACS Nano 14, 15440–15449 (2020).

- Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS<sub>2</sub> devices. 2D Mater. 4, 011009 (2016).

- Dumcenco, D. et al. Large-area epitaxial monolayer MoS<sub>2</sub>. ACS Nano 9, 4611–4620 (2015).

- 24. Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* **520**, 656–660 (2015).

- Smithe, K. K. H., Suryavanshi, S. V., Munoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS<sub>2</sub> devices. ACS Nano 11, 8456–8463 (2017).

- Xu, H. et al. High-performance wafer-scale MoS<sub>2</sub> transistors toward practical application. Small 14, e1803465 (2018).

- Xuan, Y. et al. Multi-scale modeling of gas-phase reactions in metal-organic chemical vapor deposition growth of WSe<sub>2</sub>. J. Cryst. Growth 527, 125247 (2019).

- Chubarov, M. et al. Wafer-scale epitaxial growth of single orientation WS<sub>2</sub> monolayers on sapphire. arXiv e-prints, arXiv:2006.10952. Preprint at https:// ui.adsabs.harvard.edu/abs/2020arXiv200610952C (2020)

- Zhang, F., Erb, C., Runkle, L., Zhang, X. & Alem, N. Etchant-free transfer of 2D nanostructures. *Nanotechnology* 29, 025602 (2018).

- Das, S., Chen, H. Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- Leonhardt, A. et al. Material-selective doping of 2D TMDC through AlxOy encapsulation. ACS Appl. Mater. Interfaces 11, 42697–42707 (2019).

- 32. Bhoir, M. S. et al. Variability sources in nanoscale bulk FinFETs and TiTaN- a promising low variability WFM for 7/5 nm CMOS nodes. In 2019 IEEE International Electron Devices Meeting (IEDM), 36.2.1–36.2.4 (2019).

- Weber, O. et al. High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding. In 2008 IEEE International Electron Devices Meeting, 1–4 (2008).

- Tsutsui, G., Saitoh, M., Nagumo, T. & Hiramoto, T. Impact of SOI thickness fluctuation on threshold voltage variation in ultra-thin body SOI MOSFETs. *IEEE Trans. Nanotechnol.* 4, 369–373 (2005).

- Samsudin, K., Adamu-Lema, F., Brown, A. R., Roy, S. & Asenov, A. Combined sources of intrinsic parameter fluctuations in sub-25nm generation UTB-SOI

MOSFETs: A statistical simulation study. *Solid-State Electron*. **51**, 611–616 (2007).

- Min, C., Kamins, T., Voorde, P. V., Diaz, C. & Greene, W. 0.18-μm fullydepleted silicon-on-insulator MOSFET's. *IEEE Electron Device Lett.* 18, 251–253 (1997).

- Liu, H. & Ye, P. D. MoS<sub>2</sub> Dual-Gate MOSFET with atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> as top-gate dielectric. *IEEE Electron Device Lett.* 33, 546–548 (2012).

- Guo, J., Yang, B., Zheng, Z. & Jiang, J. Observation of abnormal mobility enhancement in multilayer MoS<sub>2</sub> transistor by synergy of ultraviolet illumination and ozone plasma treatment. *Phys. E: Low.-Dimensional Syst. Nanostruct.* 87, 150–154 (2017).

- Yu, Z. et al. Towards intrinsic charge transport in monolayer molybdenum disulfide by defect and interface engineering. *Nat. Commun.* 5, 5290 (2014).

- Chang, H.-Y., Zhu, W. & Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. *Appl. Phys. Lett.* **104**, 113504 (2014).

- Das, S. & Appenzeller, J. Where does the current flow in two-dimensional layered systems? *Nano Lett.* 13, 3396–3402 (2013).

- Yang, L. et al. Chloride molecular doping technique on 2D materials: WS<sub>2</sub> and MoS<sub>2</sub>. Nano Lett. 14, 6275–6280 (2014).

- Nasr, J. R., Schulman, D. S., Sebastian, A., Horn, M. W. & Das, S. Mobility deception in nanoscale transistors: an untold contact story. *Adv. Mater.* 31, 1806020 (2019).

- 44. Rai, A. et al. Air stable doping and intrinsic mobility enhancement in monolayer molybdenum disulfide by amorphous titanium suboxide encapsulation. *Nano Lett.* **15**, 4329–4336 (2015).

- Schulman, D. S. et al. Facile electrochemical synthesis of 2D monolayers for high-performance thin-film transistors. ACS Appl Mater. Interfaces 9, 44617–44624 (2017).

- Sebastian, A. et al. Electrochemical polishing of two-dimensional materials. ACS Nano 13, 78–86 (2019).

- Yun, S. J. et al. Synthesis of centimeter-scale monolayer tungsten disulfide film on gold foils. ACS Nano 9, 5510–5519 (2015).

- Cui, Y. et al. High-performance monolayer WS<sub>2</sub> field-effect transistors on high-kappa dielectrics. *Adv. Mater.* 27, 5230–5234 (2015).

- Ovchinnikov, D., Allain, A., Huang, Y. S., Dumcenco, D. & Kis, A. Electrical transport properties of single-layer WS<sub>2</sub>. ACS Nano 8, 8174–8181 (2014).

- Aji, A. S., Solis-Fernández, P., Ji, H. G., Fukuda, K. & Ago, H. High mobility WS<sub>2</sub> transistors realized by multilayer graphene electrodes and application to high responsivity flexible photodetectors. *Adv. Funct. Mater.* 27, 1703448 (2017).

- 51. Schmidt, M. et al. Mobility extraction in SOI MOSFETs with sub 1nm body thickness. *Solid-State Electron.* **53**, 1246–1251 (2009).

- Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. *Chem. Soc. Rev.* 47, 3037–3058 (2018).

- Lee, S., Tang, A., Aloni, S. & Wong, H. S. Statistical study on the schottky barrier reduction of tunneling contacts to CVD synthesized MoS<sub>2</sub>. *Nano Lett.* 16, 276–281 (2016).

- 54. Liu, Y. et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. *Nano Lett.* 16, 6337–6342 (2016).

- Luo, P. et al. Doping engineering and functionalization of two-dimensional metal chalcogenides. *Nanoscale Horiz.* 4, 26–51 (2019).

- Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atomthick gates. *Nano Lett.* 18, 3807–3813 (2018).

- Anghel, C. Ionescu, A., Hefyene, N. & Gillon, R. Self-heating characterization and extraction method for thermal resistance and capacitance in high voltage MOSFETs. In ESSDERC'03. 33rd Conference on European Solid-State Device Research, 2003. 449–452 (2003).

- Shin, S. et al. Impact of nanowire variability on performance and reliability of gate-all-around III-V MOSFETs. In 2013 IEEE International Electron Devices Meeting, 7.5. 1–7.5. 4 (2013).

- Islam, S., Li, Z., Dorgan, V. E., Bae, M.-H. & Pop, E. Role of Joule heating on current saturation and transient behavior of graphene transistors. *IEEE electron device Lett.* 34, 166–168 (2013).

- Li, X. et al. Performance potential and limit of MoS<sub>2</sub> transistors. *Adv Mater*. 27, 1547–1552 (2015).

- Yalon, E. et al. Energy dissipation in monolayer MoS<sub>2</sub> electronics. *Nano Lett.* 17, 3429–3433 (2017).

- 62. Taur, Y. & Ning, T. *Fundamentals of Modern VLSI Devices* 2nd ed. (Cambridge, Cambridge University Press, 2009).

- Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS<sub>2</sub>. *Nano Lett.* 18, 4516–4522 (2018).

- Gong, Y., Carozo, V., Li, H., Terrones, M. & Jackson, T. N. High flex cycle testing of CVD monolayer WS<sub>2</sub> TFTs on thin flexible polyimide. 2D Mater. 3, 021008 (2016).

- English, C. D., Smithe, K. K. H., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS<sub>2</sub> transistors with self-aligned 10 nm top gates. 5.6.1–5.6.4 (2016).

- Liu, H. et al. Statistical study of deep submicron dual-gated field-effect transistors on monolayer chemical vapor deposition molybdenum disulfide films. *Nano Lett.* 13, 2640–2646 (2013).

- 67. Lundstrom, M. Fundamentals of Carrier Transport, 2nd edn (Cambridge University Press, 2000).

- Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices, 3rd edn (John Wiley & Sons, 2007).

- 69. Nathawat, J. et al. Transient hot-carrier dynamics and intrinsic velocity saturation in monolayer MoS<sub>2</sub>. *Phys. Rev. Mater.* **4**, 014002 (2020).

- Chubarov, M., Choudhury, T. H., Zhang, X. & Redwing, J. M. In-plane x-ray diffraction for characterization of monolayer and few-layer transition metal dichalcogenide films. *Nanotechnology* 29, 055706 (2018).

- CRC Handbook of Chemistry and Physics, 98th edn (Internet Version 2018) ed. (CRC Press/Taylor & Francis, Boca Raton, FL, 2018).

- Crider, C. A., Poate, J. M., Rowe, J. E. & Sheng, T. T. Platinum silicide formation under ultrahigh-vacuum and controlled impurity ambients. *J. Appl. Phys.* 52, 2860–2868 (1981).

#### Acknowledgements

The work was partially supported by Army Research Office (ARO) through Contract Number W911NF1920338. Authors also acknowledge the support from the National Science Foundation (NSF) through the Pennsylvania State University 2D Crystal Consortium–Materials Innovation Platform (2DCCMIP) under NSF cooperative agreement DMR-1539916.

#### **Author contributions**

S.D. conceived the idea. S.D. and A.S. designed the experiments and wrote the manuscript. A.S. and R.P. performed the measurements, S.D., A.S., and R.P. analyzed the data, discussed the results, and agreed on their implications. T.H.C, and J.M.R synthesized and characterized MoS<sub>2</sub> and WS<sub>2</sub> monolayers. All authors contributed to the preparation of the manuscript.

#### **Competing interests**

The authors declare no competing interests.

#### Additional information

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-020-20732-w.

Correspondence and requests for materials should be addressed to S.D.