## **Supporting information**

## Ultralow-power in-memory computing based on ferroelectric memcapacitor network

Bobo Tian<sup>1,2</sup>, Zhuozhuang Xie<sup>1,3</sup>, Luqiu Chen<sup>1</sup>, Shenglan Hao<sup>1,4</sup>, Yifei Liu<sup>1</sup>, Guangdi Feng<sup>1</sup>, Xuefeng Liu<sup>1</sup>, Hongbo Liu<sup>3</sup>, Jing Yang<sup>1</sup>, Yuanyuan Zhang<sup>1</sup>, Wei Bai<sup>1</sup>, Tie Lin<sup>5</sup>, Hong Shen<sup>5</sup>, Xiangjian Meng<sup>5</sup>, Ni Zhong<sup>1</sup>, Hui Peng<sup>1</sup>, Fangyu Yue<sup>1</sup>, Xiaodong Tang<sup>1</sup>, Jianlu Wang<sup>6</sup>, Qiuxiang Zhu<sup>1,2,8</sup>, Yachin Ivry<sup>9</sup>, Brahim Dkhil<sup>4</sup>, Junhao Chu<sup>1,5,7</sup> and Chungang Duan<sup>1,10</sup>

- 1 Key Laboratory of Polar Materials and Devices, Ministry of Education, Shanghai Center of Brain-inspired Intelligent Materials and Devices, East China Normal University, Shanghai 200241, China

- 2 Zhejiang Lab, Hangzhou 310000, China.

- 3 School of Materials Engineering, Shanghai University of Engineering Science, Shanghai, 201620, China

- 4 Université Paris-Saclay, CentraleSupélec, CNRS-UMR8580, Laboratoire SPMS, 91190 Gif-sur-Yvette, France.

- 5 State Key Laboratory of Infrared Physics, Shanghai Institute of Technical Physics, Chinese Academy of Sciences, 500 Yu Tian Road, Shanghai 200083, China.

- 6 Frontier Institute of Chip and System, Fudan University, 220 Handan Road, Shanghai, 200433, China.

- 7 Institute of Optoelectronics, Fudan University, 220 Handan Road, Shanghai, 200433, China.

- 8 Guangdong Provisional Key Laboratory of Functional Oxide Materials and Devices, Southern University of Science and Technology, Shenzhen 518055, China.

- 9 Department of Materials Science and Engineering, Solid-State Institute, Technion-Israel Institute of Technology, Haifa, 3200003 Israel.

- 10 Collaborative Innovation Center of Extreme Optics, Shanxi University, Shanxi 030006, China.

## Correspondence

Bobo tian and Qiuxiang Zhu, Key Laboratory of Polar Materials and Devices, Ministry of Education, Shanghai Center of Brain-inspired Intelligent Materials and Devices, East China Normal University, Shanghai 200241, China.

Email: bbtian@ee.ecnu.edu.cn and qxzhu@clpm.ecnu.edu.cn

Hongbo Liu, School of Materials Engineering, Shanghai University of Engineering Science, Shanghai, 201620, China.

Email: liuhongbo@sues.edu.cn

Bobo Tian, Zhuozhuang Xie, and Luqiu Chen contributed equally to this work.

## **FIGURES**

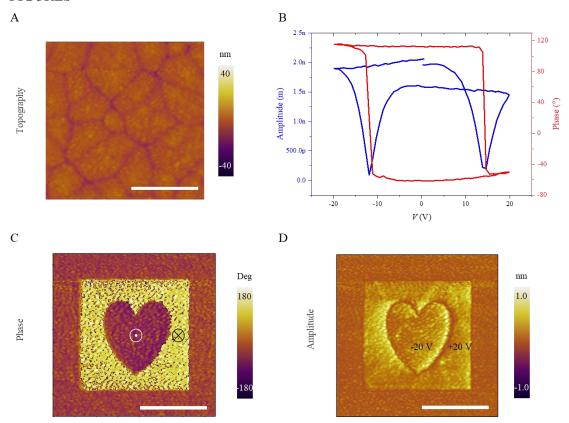

FIGURE S1 A) AFM topography image of P(VDF-TrFE) thin films. B) PFM Piezoelectric hysteresis loops of P(VDF-TrFE) thin films: phase (red) and amplitude (lue). C) PFM phase and D) amplitude image of P(VDF-TrFE) films after writing a square area on film surface with a positive voltage (+20 V) followed by a smaller "heart" with a negative voltage (-20 V) by a biased conductive tip. The scale bar is 6  $\mu$ m.

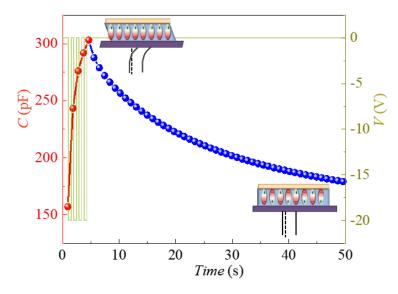

FIGURE S2 Retention of the programmed high capacitance state in the MFIS memcapacitor with 60 nm-thick P(VDF-TrFE) and 25 nm-thick SiO<sub>2</sub>.

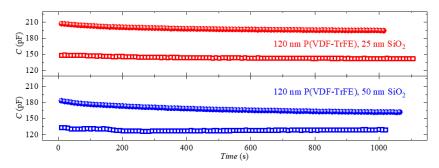

FIGURE S3 Retention of the highest capacitance state and the lowest capacitance state in a MFMIS memcapacitor with 120 nm-thick P(VDF-TrFE) and 25 nm-thick (red) or 50 nm-thick (blue) SiO<sub>2</sub>.

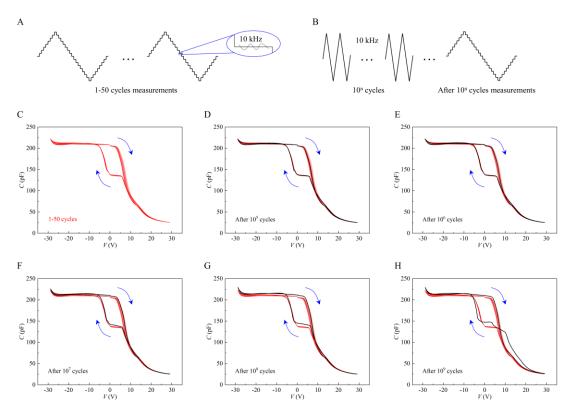

**FIGURE S4** Evolution of *C-V* hysteresis loops under endurance cycles in a MFMIS memcapacitor with 120 nm-thick P(VDF-TrFE) and 25 nm-thick SiO<sub>2</sub>. The amplitude of triangular wave cycles in (D-H) is 30 V, which is larger than the coercive voltage in the MFMIS memcapacitor.

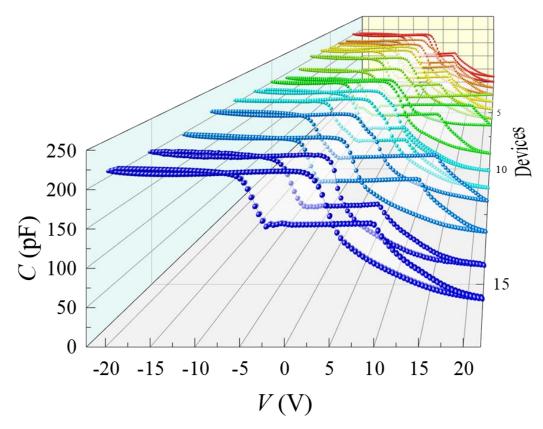

**FIGURE S5** *C-V* hysteresis loops for 16 different MFMIS memcapacitors with 120 nm-thick P(VDF-TrFE) and 25 nm-thick SiO<sub>2</sub>.