# Artificial Synapse Consisted of TiSbTe/SiC<sub>x</sub>:H Memristor with Ultra-high Uniformity for Neuromorphic Computing

Liangliang Chen <sup>1,2,3</sup>, Zhongyuan Ma <sup>1,2,3,\*</sup>, Kangmin Leng <sup>1,2,3</sup>, Tong Chen <sup>1,2,3</sup>, Hongsheng Hu <sup>1,2,3</sup>, Yang Yang <sup>1,2,3</sup>, Wei Li <sup>1,2,3</sup>, Jun Xu <sup>1,2,3</sup>, Ling Xu <sup>1,2,3</sup> and Kunji Chen <sup>1,2,3</sup>

- <sup>1</sup> School of Electronic Science and Engineering, Nanjing University, Nanjing 210093, China; puppymoon@163.com (L.C.); lengkangmin@foxmail.com (K.L.); chentong1110@foxmail.com (T.C.); xiaohuyz@163.com (H.H.); 2185223301@qq.com (Y.Y.); weili@nju.edu.cn (W.L.); junxu@nju.edu.cn (J.X.); lingxu@nju.edu.cn (L.X.); kjchen@nju.edu.cn (K.C.)

- <sup>2</sup> Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing 210093, China

- <sup>3</sup> Jiangsu Provincial Key Laboratory of Photonic and Electronic Materials Sciences and Technology,

- Nanjing University, Nanjing 210093, China

- \* Correspondence: zyma@nju.edu.cn

Abstract: To enable a-SiC<sub>x</sub>:H-based memristors to be integrated into brain-inspired chips, and to efficiently deal with the massive and diverse data, high switching uniformity of the a-SiC<sub>0.11</sub>:H memristor is urgently needed. In this study, we introduced a TiSbTe layer into an a-SiC<sub>0.11</sub>:H memristor, and successfully observed the ultra-high uniformity of the TiSbTe/a-SiC<sub>0.11</sub>:H memristor device. Compared with the a-SiC<sub>0.11</sub>:H memristor, the cycle-to-cycle coefficient of variation in the high resistance state and the low resistance state of TiSbTe/a-SiC<sub>0.11</sub>:H memristors was reduced by 92.5% and 66.4%, respectively. Moreover, the device-to-device coefficient of variation in the high resistance state and the low resistance state of TiSbTe/a-SiC<sub>0.11</sub>:H memristors decreased by 93.6% and 86.3%, respectively. A high-resolution transmission electron microscope revealed that a permanent TiSbTe nanocrystalline conductive nanofilament was formed in the TiSbTe layer during the DC sweeping process. The localized electric field of the TiSbTe nanocrystalline was beneficial for confining the position of the conductive filaments in the a-SiC<sub>0.11</sub>:H film, which contributed to improving the uniformity of the device. The temperature-dependent I-V characteristic further confirmed that the bridge and rupture of the Si dangling bond nanopathway was responsible for the resistive switching of the TiSbTe/a-SiC<sub>0.11</sub>:H device. The ultra-high uniformity of the TiSbTe/a-SiC<sub>0.11</sub>:H device ensured the successful implementation of biosynaptic functions such as spike-duration-dependent plasticity, long-term potentiation, long-term depression, and spike-timing-dependent plasticity. Furthermore, visual learning capability could be simulated through changing the conductance of the TiSbTe/a- $SiC_{0,11}$ :H device. Our discovery of the ultra-high uniformity of TiSbTe/a-SiC\_{0,11}:H memristor devices provides an avenue for their integration into the next generation of AI chips.

Keywords: memristor; uniformity; stabilization

## 1. Introduction

Brain-inspired neuromorphic computing is attracting more and more attention as a new computing system that has the potential to overcome the limitations of traditional von Neumann computational architecture [1,2]. Therefore, artificial synaptic devices for brain-inspired neuromorphic computing have been increasingly studied in recent years. As with the two-terminal structure of the biological synapse, resistive random-access memory (RRAM), also a two-terminal device, is considered to be the most promising candidate for electronic synaptic devices, due to its similarity to a characteristic of the biological synapse [2,3], whose conductance can be modified dynamically by changes in both ion and electron current flow [4]. A large amount of fascinating work has been performed to develop oxide-based RRAMs for neuromorphic systems, with promising results, such as

Citation: Chen, L.; Ma, Z.; Leng, K.; Chen, T.; Hu, H.; Yang, Y.; Li, W.; Xu, J.; Xu, L.; Chen, K. Artificial Synapse Consisted of TiSbTe/SiC<sub>x</sub>:H Memristor with Ultra-high Uniformity for Neuromorphic Computing. *Nanomaterials* **2022**, *12*, 2110. https://doi.org/10.3390/ nano12122110

Academic Editors: Claudia Barile and Gilda Renna

Received: 7 May 2022 Accepted: 14 June 2022 Published: 19 June 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). HfOx-based synaptic devices [5], TiO<sub>x</sub>-based synaptic devices [6], Ag/STO:Ag/SiO<sub>2</sub>/p++-Si structure [1], and TiN/SiO<sub>x</sub>/TiN [4] structure. Among these, silicon-based materials are highly valued, due to their compelling advantage of being fully CMOS-compatible [7], which can greatly simplify the circuit. Zarudnyi et al. [4] demonstrated the spike-timingdependent plasticity of silicon-rich silicon oxide (SiO<sub>x</sub>), which confirmed that SiOx-based RRAM is a good biological synapse device. Furthermore, SiO<sub>x</sub> switching layers ensure full compatibility with complementary metal-oxide semiconductor (CMOS) technology, leading to a reduction in circuit complexity. However, the set voltage of SiO<sub>x</sub>-based devices fluctuates in the range of 3.5 V to 4 V, and the reset voltage is around 2.5 V, showing relatively high power consumption. Furthermore, the endurance test of 150 cycles showed a large fluctuation in the LRS, which indicates that the uniformity of the Si-based device still needs to be improved.

With the approaching era of big data and artificial intelligence, a next-generation memristor with high uniformity, high density, and low consumption is urgently needed, to construct the artificial synapse, which is the key to ensuring the realization of the brain-inspired chip [8–11]. Compared with SiO<sub>x</sub>-based RRAM, SiC-based resistive switching memory has recently attracted great interest due to its promising advantages, such as tunable conductance, which is beneficial for obtaining controllable synaptic weight. In particular, SiC-based resistive memory with a forming-free characteristic can be easily integrated into the neuromorphic computing chip, with a simple peripheral circuit at a low cost [12–14]. To enable the SiC-based memristor to integrate into the brain-inspired chip and efficiently deal with the massive and diverse data, the uniformity of the switching parameters such as R<sub>ON</sub>, R<sub>OFF</sub>, V<sub>SET</sub>, and V<sub>RESET</sub> need to be improved in the successive switching cycles. Exploring effective ways to improve the switching uniformity of the SiC memristor is highly demanded [15–24].

In this study, we report an efficient way to obtain the ultra-high uniformity of switching parameters by introducing a TiSbTe (TST) layer into the top electrode and the a-SiC<sub>0.11</sub>:H. In our previous work [25], we obtained three kinds of  $a-SiC_x$ :H-based devices, with C/Si ratios of 0.11, 0.25, and 0.49, by tuning SiH4/CH4 flow ratios of 5/1, 6.25/1, and 10/1, respectively. We found that the memory window increased from 10 to  $10^3$ , with the C/Si ratio decreasing from 0.49 to 0.11. The Al/a-SiC $_{0.11}$ :H/Si device had the smallest set voltage and the best stability among the three devices. Thus, we chose to conduct further research on the Al/a-SiC<sub>0.11</sub>:H/Si device. We found that, compared to the Al/a-SiC<sub>0.11</sub>:H/Si<sup>+</sup> (ASS) memristor, the cycle-to-cycle coefficient of variation in the high resistance state and the low resistance state of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/Si<sup>+</sup> (ATSS) memristor could be reduced by 92.5% and 66.4%. Moreover, the device-to-device coefficient of variation in the high resistance state and the low resistance state of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/Si<sup>+</sup> memristor could be reduced by 93.6% and 86.3%. HRTEM revealed that the significantly improved uniformity could be attributed to the confinement role of the TST crystalline nanopathway, which combined with the Si dangling bond to form a stable, conductive pathway. The conduction mechanism of the Al/TST/a-SiC<sub>0.11</sub>:H/Si<sup>+</sup> devices in both the LRS and the HRS was further analyzed through temperature-dependent current analyses.

#### 2. Materials and Methods

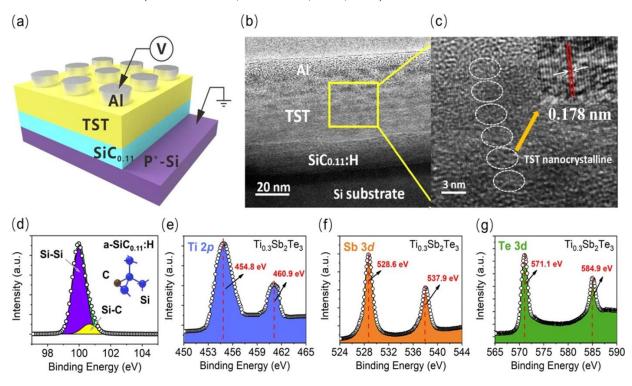

Figure 1a,b show the structural diagrams of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si memory device. An a-SiC<sub>0.11</sub>:H film of 30 nm thickness was deposited on the P<sup>+</sup>-Si substrate by a plasma-enhanced chemical vapor deposition system at 250 °C. The gas precursors consisted of SiH<sub>4</sub> and CH<sub>4</sub>, with a volume ratio of 5:1. Then, a 30 nm-thick TST layer was grown on the surface of the a-SiC<sub>0.11</sub>:H films, using an ACS-4000-cs magnetron sputtering system at room temperature. The power of the magnetron sputtering was 50 W. For comparison, a reference device of 30 nm thickness, without a TST layer, was also fabricated in parallel. Finally, aluminum top electrodes, with differing diameters, were deposited via thermal evaporation. The top electrodes of our device were circular aluminum, with diameters of 1000 nm, 800 nm, and 500 nm. The corresponding device area was 0.79 um<sup>2</sup>, 0.50 um<sup>2</sup>, and

0.20 um<sup>2</sup>. Aluminum was also deposited at the backside of the Si substrate as the back electrode, for better contact. The atomic concentration ratios of the a-SiC<sub>0.11</sub>:H films and the TST films were obtained from the surface of the corresponding films by an XPS test, using the PHI 5000 Versa Probe (Ulvac-Phi Inc., Chigasaki, Japan). The microstructures of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si memory device after electric measurement were analyzed using high-resolution cross-section transmission electron microscopy (HRTEM) (JEOL Inc., Tokyo, Japan), with a JEOL 2100F electron microscope operated at 200 kV. Electrical characterizations of the memory devices were performed using an Agilent B1500A semiconductor analyzer (Agilent Inc., Santa Clara, CA, USA). The CRX-4K Lake Shore system was adopted to analyze the temperature-dependent *I-V* characteristic under a vacuum of  $5 \times 10^{-5}$  Torr (Lake Shore Inc., Westerville, Ohio, USA).

**Figure 1.** (a) The schematic diagram of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si memory device after the DC sweeping electrical measurement; (b) Cross-section TEM of Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si RRAM device after the first setting process; (c) High-resolution cross-section TEM of TST nanocrystalline formed in the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si RRAM device after electric measurement; The TST nanocrystalline dot is marked by the circles. And the inset shows the interplanar spacing of TST nanocrystalline is 0.178 nm, which is marked by the distance of two red lines. (d–g) XPS spectra of a-SiC<sub>0.11</sub>:H and Ti 2*p*, Sb 3*d*, Te 3*d* in Ti<sub>0.3</sub>Sb<sub>2</sub>Te<sub>3</sub>.

### 3. Results and Discussion

A cross-sectional TEM image of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si RRAM device after electric measurement is displayed in Figure 1b. Clear interface of TST and a-SiC<sub>0.11</sub>:H was identified, revealing that the thicknesses of the TST layer and the a-SiC<sub>0.11</sub>:H layer were 40 and 30 nm, respectively. As shown in Figure 1c, the TST nanocrystalline could be seen clearly to be distributed in the TST layer, which formed a continuous nanopathway in the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si RRAM device. Interestingly, the TST nanocrystalline could not switch from its crystalline state to an amorphous state in the following negative or positive DC sweeping. Usually, to obtain phase changing of TST materials, a short electrical pulse is used to achieve the amorphous state (the high resistance RESET state); a lower, but slightly longer current pulse, is needed to convert it to the polycrystalline state (the lower resistance SET state) [26]. Here, the duration of the DC voltage in our set, and the reset progress, was ms, which could produce enough Joul heat to make the TST films transform

from the amorphous state to the crystalline state. Therefore, the TST dot remained in the crystalline state, which ensured that the TST nanopathway could not be ruptured in the following cycles. The composition analysis of the TST/a-SiC<sub>0.11</sub>:H films was conducted by using X-ray photoelectron spectroscopy. Figure 1d shows the Si 2p spectrum of the a-SiC<sub>0.11</sub>:H, which was deconvoluted into two Gaussian peaks related to Si–Si (99.2 eV) and Si–C (100.8 eV). Figure 1e–g display the Ti 2p, Sb 3d, and Te 3d peaks from the surface of the Ti<sub>0.3</sub>Sb<sub>2</sub>Te<sub>3</sub> film. The peaks corresponding to Sb 3d are located at 528.6 eV and 537.9 eV, while the peaks related to Te 3d are centered at 571.1 eV and 584.9 eV. Compared to Sb<sub>2</sub>Te<sub>3</sub>, the peaks of Te-3d and Sb-3d have lower energy with Ti doping, which indicates that the original bonding structure changed. The doped Ti atoms likely replaced the Sb, and formed Ti-Te bonds, and a stable structure of TST was thereby formed.

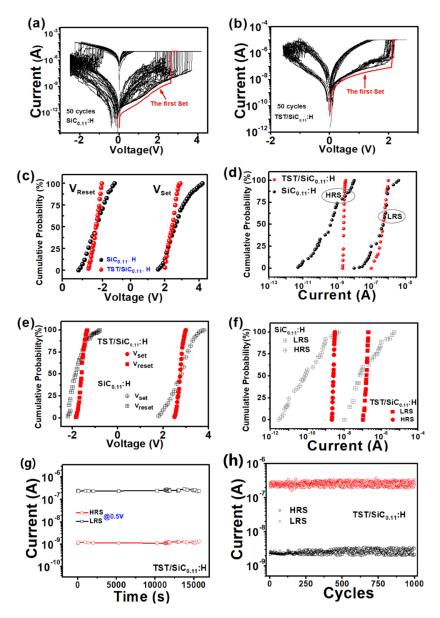

To compare the performances of the ASS and the ATSS memristor devices, current voltage (I–V) curves of 50 consecutive cycles are shown in Figure 2a,b, respectively. During the electrical measurement, a 10-uA compliance current was used to protect the devices from permanent breakdown. The red lines in the inset represent their first sweep. It is worth noting that both samples exhibited forming-free behavior, as the first sweeping voltage was within the range of the following set voltages. An interesting finding was that the first sweeping voltage of the ATSS devices was 2.2 V, which was lower than the 2.7 V of the ASS device. This means that the conductivity of the nanopathway was enhanced after the introduction of the TST layer on to the ASS device, which was related to the appearance of the TST nanocrystalline. Meanwhile, the ATSS devices exhibited highly improved uniformity compared with that of the ASS devices. During the 50 cycles, the  $V_{set}$  and  $V_{reset}$  range of the ASS were 1.8~3.8 V and  $-0.8 \sim -2.3$  V, while those of the ATSS were  $1.9 \sim 2.25$  V and  $-1.0 \sim -1.5$  V, respectively. Evidently, the dispersion of the switching curves was greatly minimized in the ATSS structure. Figure 2c,d shows the accumulative probability of V<sub>set</sub> and V<sub>reset</sub>, Ron, and Roff, during the 50 set/reset switching cycles under DC voltage. It was evident that the fluctuation of the  $V_{set}/V_{reset}$ , and the HRS/LRS of the ATSS devices, were sharply reduced, in contrast to that of the ASS device. Compared with that of the a-SiC<sub>0.11</sub>:H memristor, the cycle-to-cycle coefficient of variation in the high resistance state and the low resistance state of the TiSbTe/a-SiC<sub>0.11</sub>:H memristor was reduced by 92.5% and 66.4%, respectively. In addition, the variation of device-to-device parameters in these two types of device is displayed in Figure 2e,f: they were detected in 30 random devices after 30 cycles. The accumulative probability of the V<sub>set</sub>/V<sub>reset</sub> and the HRS/LRS values showed that the ATSS device had a narrower distribution of device-to-device parameters, further confirming the remarkable uniformity. Compared to that of the a-SiC $_{0.11}$ :H memristor, the device-to-device coefficient of variation in the high resistance state and the low resistance state of the 30 randomly selected TiSbTe/a-SiC<sub>0.11</sub>:H memristors was reduced by 93.6% and 86.3%. The retention and the endurance characteristics of the TiSbTe/a-SiC<sub>0.11</sub>:H memristor are presented in Figure 2g,h, respectively. No degradation was observed from the two resistance states at 80  $^{\circ}$ C after 10<sup>4</sup> s (read at 0.5 V), as shown in Figure 2g. The memory window of  $10^2$  also remained stable. In addition, the reproducibility of the device was also displayed by the repetition of the RS behavior for 1000 cycles, as shown in Figure 2h. The ATSS device clearly maintained high stability, with no misreading of resistance states or switching failure during the measurement, which demonstrated high resistive switching reliability.

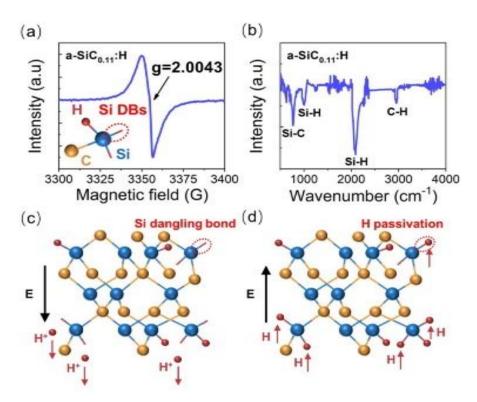

In order to understand the correlation between resistive switching and the atomic configurations of a-SiC<sub>0.11</sub>H films, the corresponding Fourier transform infrared (FTIR) spectroscopy and electron spin resonance (ESR) spectra were analyzed, as shown in Figure 3a,b. A resonance peak with a g value of 2.0043 can be observed for the a-SiC<sub>0.11</sub>:H films, which was induced by the Si dangling bonds (Si DBs) in the a-SiC<sub>x</sub>. This indicates that Si DBs were formed in the a-SiC<sub>0.11</sub>:H films during the chemical vapor deposition. As shown in Figure 3b, FTIR peaks related to the Si-H wagging vibrations, the Si-H stretching vibrations, the Si-C stretching vibrations, and the C-H stretching modes, could be detected in absorption bands of 1000 cm<sup>-1</sup>, 2000 cm<sup>-1</sup>, 780 cm<sup>-1</sup>, and 2900 cm<sup>-1</sup>, respectively. The C-H bonds and Si-H bonds were derived from the hydrogenation of the silicon carbon. The higher intensity of both the Si-H wagging mode and the Si-H stretching mode indicated that there were a number of Si-H bonds in the as-deposited films. The above results indicated that there were Si DBs and Si-H bonds in the a-SiC<sub>0.11</sub>:H films in their initial state. As the Si-C bond energy (3.7 eV) and the C-H bond energy (4.2 eV) was higher than that of the Si-H bond (3.0 eV), the Si-H bonds were easier to break, which generated Si dangling bonds under the electric field. As displayed in Figure 3c, Si DBs were produced, as the Si-H bonds could be broken under the positive electric field, and hydrogen ions migrated towards the negative cathode. When the number of Si DBs reached a high level, a filament of Si dangling bonds was formed, causing the device to switch from an HRS to an LRS. Under negative bias, the migration of H<sup>+</sup> ions was able to passivate some Si DBs, causing the Si dangling bond conductive pathway to be disconnected. Thus, the device could be switched back to an HRS.

**Figure 2.** (**a**,**b**) Resistive switching I–V curves of ASS device and ATSS device during the SET and RESET process after 50 cycles as marked by black lines and the first set is marked by red lines. (**c**,**d**) Accumulative probability of Vset, Vreset, Ron, and Roff after 50 cycles; (**e**,**f**) Variation distribution of device-to-device Vset, Vreset, and LRS/HRS values. Data were obtained from 30 ASS and ATSS memristor devices; (**g**) Retention characteristics of the ATSS memristor device at 80 °C; (**h**) The endurance characteristic of the ATSS memristor.

**Figure 3.** (**a**,**b**) ESR and FTIR spectra of as-deposited a-SiC<sub>0.11</sub>H films; (**c**) Under a positive bias, Si dangling bonds were formed, due to the broken Si-H bonds; (**d**) Under a negative bias, Si dangling bonds were passivated by H<sup>+</sup>.

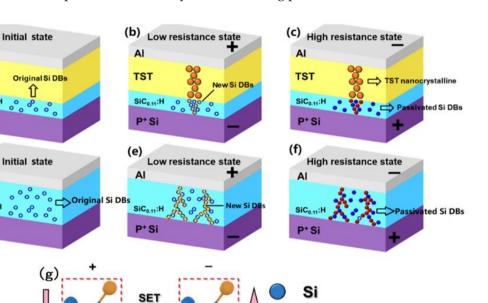

To explore the reason for the suppression of the dispersion of the switching parameters after the introduction of the TST layer into the ASS device, a confined resistive switching nanopathway model of the ATSS device is illustrated in Figure 4. In the initial state  $(I_S)$ , a number of Si DBs pre-existed randomly in the a-SiC<sub>0.11</sub>:H layer, as shown in Figure 4a. Under a positive voltage, the TST layer transformed from an amorphous state to a crystalline state, due to the heat of the increased current, generating a permanent TST nanofilament in the TST film, which was confirmed by the HRTEM photograph in Figure 1c. Meanwhile, more Si-H bonds were able to aggregate near the tip of the TST nanopathway, causing it to break, generating new Si dangling bonds in the a-SiC<sub>0.11</sub>:H layer under the localized electric field [15,27,28]. When the number of Si DBs increased to a certain extent, they formed a conductive pathway and were connected with the TST nanopathway, switching the device to an LRS, as illustrated in Figure 4b. When negative voltage was applied, those Si DBs in the original nanopathway were accurately passivated by H<sup>+</sup>, due to the role of the localized electric field induced by the TST nanocrystalline. The passivation of the Si dangling bonds resulted in the rupture of the conductive nanopathway, as displayed in Figure 4c. Therefore, the device was able to return to an HRS. Here, the TST nanopathway supplied a "fixed position" to confine the growth and rupture of the Si dangling bonds during the RS process. In contrast to the AST device, the distribution of the Si DB nanopathway under a positive bias was random in the ASS device, without the confinement of the TST nanopathway as shown in Figure 4e. Under a negative bias, not all Si dangling bonds in the original nanopathway were accurately passivated by H<sup>+</sup>, which resulted in the fluctuation of the switching parameters during the successive cycles [29]. It was evident that the TST nanocrystalline was beneficial for improving the uniformity of the conductive nanopathway guidance, while the formation and passivation of the Si dangling bond were responsible for the bridge and rupture of the conductive nanopathway. As displayed in Figure 4g, new Si DBs were produced from the broken Si-H bonds under the positive electric field. When the bias changed to negative, the Si DBs were passivated by H<sup>+</sup>. (a)

AI

TST

SIC. .... H

P\* Si

(d)

AI

SIC0.11:H

P<sup>+</sup>Si

С

н

Therefore, it can be seen that a combined conductive nanopathway of TST nanocrystalline and Si DBs can improve the uniformity of the switching parameters of the ATSS device.

**Figure 4.** The resistive switching model of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device: (**a**) In the initial state, the Si dangling bonds distribute in the a-SiC<sub>0.11</sub>:H layer, which are represented by the blue circle; (**b**) In the LRS, TST nanocrystalline was produced under the DC positive voltage. The localized electric field of the TST nanocrystalline induced more Si DBs to aggregate under the TST nanocrystalline, forming an Si DB-conductive nanopathway; (**c**) In the HRS, H<sup>+</sup> moved back to accurately passivate the original Si dangling bonds under negative voltage, resulting in the rupture of the conductive nanopathway; (**d**) The resistive switching model of the Al/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device. In the initial state, the Si dangling bonds were distributed in the a-SiC<sub>0.11</sub>:H layer, and are represented by the blue circles; (**e**) In the LRS, new Si DBs were formed from broken Si-H bond under a positive bias, forming a conductive nanopathway; (**f**) In the HRS, H<sup>+</sup> moved back to passivate some Si dangling bonds under a negative voltage, resulting in the rupture of the conductive forming a conductive nanopathway; (**f**) In the HRS, H<sup>+</sup> moved back to passivate some Si dangling bonds under a negative voltage, resulting in the rupture of the conductive nanopathway; (**g**) The breakage of the Si-H bonds and the passivation of the Si dangling bonds by H<sup>+</sup> under the electric field direction of forward and reverse direction made the pathway be broken up and connected.

RESET

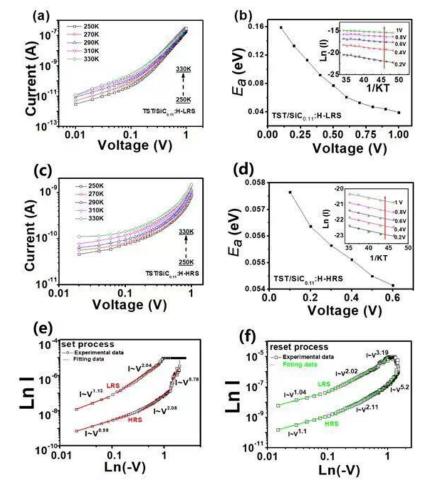

To further illustrate the role of the Si dangling bond conductive nanopathway on the resistive switching process of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si RRAM, the temperature dependence of the HRS and the LRS currents is shown in Figure 5a–c. It can be seen that the current values of the LRS and the HRS increased as the temperature increased from 250 to 330 K, indicating a semiconductor-like conduction behavior [28-30]. According to the slopes of Arrhenius-type plots, the activation energy of the HRS and the LRS was obtained in Figure 5b,d. In the LRS, the  $E_{\alpha}$  was reduced from 0.15 eV to 0.04 eV, with the voltage increasing from 0.125 to 1 V. The same changing trend of Ea was observed in the HRS, which decreased from 0.058 to 054 eV, with the voltage increasing from 0.1 to 0.6 V. Both showed characteristic SCLC conduction behavior [31]. The I-V characteristic curves of the HRS and the LRS were replotted in double logarithmic scales for illustrating the set process and reset process in the  $Al/TST/a-SiC_{0.11}$ :H/P<sup>+</sup>-Si device. As shown in Figure 5e, hot mobile electrons made the contribution to the carrier transformation via thermal excitation in the conduction band, and followed the Ohmic conduction rule, with an I–V slope of 0.98 under low voltage during the set process. With the bias increasing, the Si-H bond was broken, to form Si DBs under the electric field, with H<sup>+</sup> ions migrating towards the

negative cathode. With the number of the Si DBs increasing, a conductive nanopathway was formed, causing the current to deviate from Ohm's law to Child's law, with an I-Vslope of 2.08. When the voltage (Vset) was increased to a higher level, the number of Si DBs reached maximum. A remarkable enhancement of the current was observed, with the slope increasing from 2.08 to 5.78, switching the memory device from an HRS to an LRS. In the initial low resistance region, with a slope of 2.04, when the device was still in the LRS state, all Si DBs remained filled. However, the number of the carrier injection reduced with the decreased voltage. Therefore, the slope decreased from 2.04 to 1.13 in the low-voltage region, revealing that current conduction behavior in the LRS was consistent with the SCLC mechanism. The Ln (I) versus Ln (-V) curves of the reset process are also shown in Figure 5f. Before the voltage reached the Vreset, the occupied Si DBs made the device keep to an LRS. Once the bias increased to Vreset, the Si DBs began to discharge electrons in the high-voltage region. Meanwhile, more and more Si DBs were passivated by H<sup>+</sup> ions under negative voltage. Thus, electrons were released from most of the occupied Si DBs, accompanied by the rupture of the Si DB conductive pathway, switching the memory device from an LRS to an HRS. Therefore, both the LRS and the HRS could be dominated by the Si DBs-controlled SCLC mechanism, which was consistent with the results of the temperature-dependence analysis.

**Figure 5.** (**a**–**c**) Temperature-dependent current of the ATSS device in the HRS and the LRS at temperatures from 250 K to 330 K; (**b**–**d**) The activation energy of the ATSS device in the HRS and LRS, which is decreased with the voltage increasing. The inset shows an Arrhenius plot of the temperature-dependent current of the HRS and the LRS. The current intensity is enhanced with the voltage increasing as marked by the red arrows; (**e**,**f**) The experimental and theoretical fitting curves of the set and reset process of the Al/a-SiC<sub>0.11</sub>:H/p<sup>+</sup>Si device.

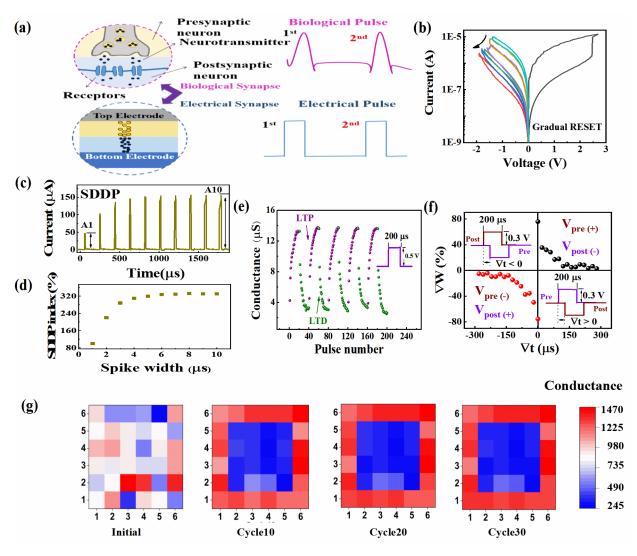

To enable the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device to be used as an artificial synapse for integration into a brain-inspired chip, we studied the long-term memory and the shortterm memory characteristics of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si artificial synapse. As shown in Figure 6a, the structure of the biological synapse was similar to that of the prepared Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device. The pre-synaptic and post-synaptic neurons could be regarded as the top electrode and the bottom electrode, respectively. To make the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device emulate the function of the biosynapse, the multilevel resistive switching characteristics of the Al/TiSbTe/SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device were measured by controlling the reset stop voltages, as shown in Figure 6b. The current decreased gradually with the increasing of negative voltage, which was similar to the tunable synaptic weight. We studied the short-term characteristic of the TiSbTe/SiC<sub>0.11</sub>:H artificial synapse, which was spike-duration-dependent plasticistic (SDDP). The synaptic weight of the TiSbTe/SiC<sub>0.11</sub>:H synapse was effectively amplified by prolonging the duration of the synaptic spike. Continuous pre-synaptic spikes were applied to the top electrode, which were insufficient to set the TiSbTe/SiC $_{0.11}$ :H artificial synapse for long-term memory retention; however, they were able to produce an excitatory post-synaptic current. As shown in Figure 6d, the strength of the artificial synapses was characterized by the SDDP index  $(An/A1 \times 100\%; n = 1, 2, 3..., 10)$ . The increased duration of the spike was from 1 µs to 10  $\mu$ s ( $\Delta$ t = 1  $\mu$ s), and the amplitude of the spike was fixed at 1.2 V. In Figure 6d, A1 and A10 represent the currents of the device after the first and tenth spike, respectively. As shown in Figure 6c,d, the continuously increased spike duration caused a brief increase in synaptic weight. Unlike the short-term memory, the long-term memory (LTM) was able to change the synaptic weight permanently, which was the key element of the learning behavior. The analogue LTM of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device was evaluated by applying 20 positive pulses, followed by 20 negative pulses. As shown in Figure 6e, the conductance of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device increased/decreased when the continued positive/negative spikes were applied. The conductance updating was continued for five sweeping circles, exhibiting stable analogue switching behavior. As the representative characteristic of long-term memory, spike-timing-dependent plasticity (STDP) obeys the asymmetric Hebbian learning rule, which can reflect the connection between two neurons by modulating the relative timing ( $\Delta t$ ) of activations from the pre-synapse and post-synapse. As shown in Figure 6a, the top electrode acted as the pre-synaptic terminal, and the bottom electrode was the post-synaptic terminal. The designed spike conditions are displayed in the inset of Figure 6f. The pre-synaptic spike (+) preceded the post-synaptic spike (-)when  $\Delta t > 0$ . The pre-synaptic spike (–) lagged behind the post-synaptic spike (+) when  $\Delta t < 0$ . The relationship between the synaptic strength and the time difference is shown in Figure 6f. In accordance with the learning rule, when the pre-spike preceded/lagged behind the post-spike, the connection strength of the synapse between the two neurons was reinforced/weakened. It can be seen that a larger conductance change was caused by a closer spike timing, which was consistent with the Hebbian learning rule. In order to visualize the information handling in the TiSbTe/a-SiC<sub>0.11</sub>:H neural network, the 6  $\times$  6 synaptic arrays based on the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si memory were applied to image memorization by simulation, as shown in Figure 6g. The conductance was represented by the color level. In the initial state, the conductance of all synapses was distributed randomly. After the stimulation of 10 continuous pulses with a duration of 1  $\mu$ s and an amplitude of 1 V, the conductance of the devices around the outside of the synaptic arrays was enhanced. As the number of pulses increased to 30, the clearness of the simulated image reached a high level.

**Figure 6.** (a) A schematic diagram of biological synapse and electrical synapse; (b) Multilevel resistive switching characteristics of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device, with different reset stop voltage; (c) The SDDP characteristics of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device; (d) The SDDP index (An/A1·100%; n = 1, 2, 3, ..., 10) of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device; (e) Incremental conductance changes through 20 positive pulses (0.5 V, 200 µs) followed by 20 negative pulses (-0.5 V, 200 µs); (f) Spike-timing-dependent plasticity (STDP) of the Al/TiSbTe/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device; through the overlapping of the pre-synaptic spike and the post-synaptic spike; (g) The simulation of image memorization under consecutive electrical pulses.

#### 4. Conclusions

In summary, ultra-high uniformity was obtained from the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si memristor by introducing a TST layer between the a-SiC<sub>0.11</sub>:H and the top electrode. Compared with that of the a-SiC<sub>0.11</sub>:H memristor, the cycle-to-cycle coefficient of variation in the high resistance state and the low resistance state of the TiSbTe/a-SiC<sub>0.11</sub>:H memristor was reduced by 92.5% and 66.4%. Moreover, the device-to-device coefficient of variation in the high resistance state and the low resistance state of the TiSbTe/a-SiC<sub>0.11</sub>:H memristor was decreased by 93.6% and 86.3%. HRTEM revealed that the TST nanocrystalline was formed in the TST layer during the first DC sweeping process, and remained in a crystalline state permanently in the following switching process. The localized electric field of the TST nanocrystalline was beneficial to confining the position of the Si dangling bond filaments in the a-SiC<sub>0.11</sub>:H film, which contributed to improving the uniformity of the device. The temperature-dependent I-V characteristic further confirmed that the

bridge and rupture of the Si dangling bond nanopathway was responsible for the resistive switching of the Al/TST/a-SiC<sub>0.11</sub>:H/P<sup>+</sup>-Si device, which combined with the TST nanocrystalline to form the conductive pathway. The ultra-high uniformity of the TiSbTe/a-SiC<sub>0.11</sub>:H device ensured the successful implementation of biosynaptic functions such as spike-duration-dependent plasticity, long-term potentiation, long-term depression, and spike-timing-dependent plasticity. Furthermore, it proved possible to simulate visual learning capability by changing the conductance of the TiSbTe/a-SiC<sub>0.11</sub>:H device. Our discovery of the ultra-high uniformity of TiSbTe/a-SiC<sub>0.11</sub>:H memristor devices provides an avenue for their integration into the next generation of AI chips.

**Author Contributions:** Conceptualization, Z.M. and L.C.; formal analysis, Z.M., K.L., H.H. and Y.Y.; writing—original draft preparation, K.L., T.C. and L.C.; writing—review and editing, Z.M., K.C. and W.L.; supervision, Z.M., J.X. and L.X.; project administration, Z.M. and J.X.; funding acquisition, Z.M. All authors have read and agreed to the published version of the manuscript.

**Funding:** This study was supported by the National Nature Science Foundation of China (Grant Nos. 61634003, 61571221, 11774155, 61921005 and 61735008), and the National Key R&D program of China (2018YFB2200101). A portion of this work was performed on the Steady High Magnetic Field Facilities, High Magnetic Field Laboratory, CAS.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Data can be available upon request from the authors.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Ilyas, N.; Wang, J.Y.; Li, C.M.; Fu, H.; Li, D.Y.; Jiang, X.D.; Gu, D.; Jiang, Y.D.; Li, W. Controllable resistive switching of STO:Ag/SiO<sub>2</sub> -based memristor synapse for neuromorphic computing. *J. Mater. Sci. Technol.* **2022**, *97*, 254–263. [CrossRef]

- Liu, J.; Yang, H.F.; Ji, Y.; Ma, Z.Y.; Chen, K.J.; Zhang, X.X.; Zhang, H.; Sun, Y.; Huang, X.F.; Oda, S. An electronic synaptic device based on HfO<sub>2</sub>/TiO<sub>x</sub> bilayer structure memristor with self-compliance and deep-RESET characteristics. *Nanotechnology* 2018, 29, 415205–415215. [CrossRef] [PubMed]

- 3. Woo, J.; Moon, K.; Song, J.; Lee, S.; Kwak, M.; Park, J.; Hwang, H. Improved synaptic behavior under identical pulses using AlO<sub>x</sub>/HfO<sub>2</sub> bilayer RRAM array for neuromorphic systems. *IEEE Electron. Device Lett.* **2016**, *37*, 994–997. [CrossRef]

- Zarudnyi, K.; Mehonic, A.; Montesi, L.; Buckwell, M.; Hudziak, S.J.; Kenyon, A. Spike-Timing Dependent Plasticity in Unipolar Silicon Oxide RRAM Devices. Front. Neurosci. 2018, 12, 57. [CrossRef]

- Yu, S.M.; Wu, Y.; Jeyasingh, R.; Kuzum, D.G.; Wong, H.S.P. An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation. *IEEE Trans. Electron. Dev.* 2011, *58*, 2729–2737. [CrossRef]

- Park, J.; Kwak, M.; Moon, K.; Woo, J.; Lee, D.; Hwang, H. TiO<sub>x</sub>-based RRAM synapse with 64-levels of conductance and symmetric conductance change by adopting a hybrid pulse scheme for neuromorphic computing. *IEEE Electron. Device Lett.* 2016, 37, 1559–1562. [CrossRef]

- Mehonic, A.; Buckwell, M.; Montesi, L.; Garnett, L.; Hudziak, S.; Fearn, S.; Chater, R.; McPhail, D.J.; Kenyon, A. Structural changes and conductance thresholds in metal-free intrinsic SiO<sub>x</sub> resistive random access memory. *J. Appl. Phys.* 2015, 117, 124505. [CrossRef]

- 8. Ren, Y.; Milo, V.; Wang, Z.; Xu, H.; Ielmini, D.; Zhao, X.; Liu, Y. Analytical Modeling of Organic-Inorganic CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> Perovskite Resistive Switching and its Application for Neuromorphic Recognition. *Adv. Theor. Simul.* **2018**, *1*, 4.

- Chen, Y.; Li, H.H.; Bayram, I.; Eken, E. Recent Technology Advances of Emerging Memories. *IEEE Des. Test* 2017, 34, 8–22. [CrossRef]

- Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-Based Resistive Switching Memories—Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* 2009, 21, 25–26. [CrossRef]

- 11. Yang, Y.; Huang, R. Probing memristive switching in nanoionic devices. Nat. Electron. 2018, 1, 274–287. [CrossRef]

- 12. Morgan, K.A.; Fan, J.; Huang, R.; Zhong, L.; Gowers, R.; Ou, J.Y.; Jiang, L.; De Groot, C.H. Active counter electrode in a-SiC electrochemical metallization memory. *J. Phys. D. Appl. Phys.* **2017**, *50*, 32. [CrossRef]

- 13. Zhong, L.; Reed, P.A.; Huang, R.; De Groot, C.H.; Jiang, L. Amorphous SiC based non-volatile resistive memories with ultrahigh ON/OFF ratios. *Microelectron. Eng.* **2014**, *119*, 61–64. [CrossRef]

- 14. Morgan, K.A.; Fan, J.; Huang, R.; Zhong, L.; Gowers, R.P.; Jiang, L.; De Groot, C.H. Switching kinetics of SiC resistive memory for harsh environments. *AIP Adv.* 2015, *5*, 7. [CrossRef]

- 15. Kageyama, S.; Matsuki, N.; Fujiwara, H. Local network structure of a-SiC:H and its correlation with dielectric function. *J. Appl. Phys.* **2013**, *114*, 233513. [CrossRef]

- 16. Liu, Y.; Gao, P.; Jiang, X.; Li, L.; Zhang, J.; Peng, W. Percolation mechanism through trapping/de-trapping process at defect states for resistive switching devices with structure of Ag/Si<sub>x</sub>C<sub>1-x</sub>/p-Si. *J. Appl. Phys.* **2014**, *116*, 6. [CrossRef]

- 17. Raeis, H.N.; Lim, S.; Hwang, H.; Rho, J. Reliable Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>-Integrated High-Density Nanoscale Conductive Bridge Random Access Memory using Facile Nitrogen-Doping Strategy. *Adv. Electron. Mater.* **2018**, *4*, 11.

- Chang, W.Y.; Cheng, K.J.; Tsai, J.M.; Chen, H.J.; Chen, F.; Tsai, M.J.; Wu, T.B. Improvement of resistive switching characteristics in TiO<sub>2</sub> thin films with embedded Pt nanocrystals. *Appl. Phys. Lett.* 2009, 95, 4.

- Qin, S.C.; Dong, R.X.; Yan, X.L. Memristive behavior of Al<sub>2</sub>O<sub>3</sub> film with bottom electrode surface modified by Ag nanoparticles. *Appl. Phys. A* 2014, 118, 605–612. [CrossRef]

- Liu, P.T.; Fan, Y.S.; Chen, C.C. Improvement of Resistive Switching Uniformity for Al–Zn–Sn–O-Based Memory Device With Inserting HfO<sub>2</sub> Layer. *IEEE Electron. Device Lett.* 2014, 35, 1233–1235. [CrossRef]

- 21. Lv, H.; Wan, H.; Tang, T. Improvement of Resistive Switching Uniformity by Introducing a Thin GST Interface Layer. *IEEE Electron. Device Lett.* 2010, *31*, 978–980. [CrossRef]

- 22. Kang, X.; Guo, J.; Gao, Y.; Ren, S.; Chen, W.; Zhao, X. NiO-based resistive memory devices with highly improved uniformity boosted by ionic liquid pre-treatment. *Appl. Surf. Sci.* 2019, 480, 57–62. [CrossRef]

- Pang, H.; Deng, N. A Forming-Free Bipolar Resistive Switching in HfO<sub>x</sub>-Based Memory with a Thin Ti Cap. *Chin. Phys. Lett.* 2014, *31*, 10. [CrossRef]

- Chen, Y.S.; Lee, H.Y.; Chen, P.S.; Wu, T.Y.; Wang, C.C.; Tzeng, P.J.; Chen, F.; Tsai, M.J.; Lien, C. An Ultrathin Forming-Free HfO<sub>x</sub> Resistance Memory With Excellent Electrical Performance. *IEEE Electron. Device Lett.* 2010, *31*, 1473–1475. [CrossRef]

- Chen, L.L.; Len, K.M.; Ma, Z.Y.; Yu, X.Y.; Shen, Z.X.; You, J.Y.; Li, W.; Xu, J.; Xu, L.; Chen, K.J.; et al. Tunable Si Dangling Bond Pathway Induced Forming-Free Hydrogenated Silicon Carbide Resistive Switching Memory Device. J. Phys. Chem. Lett. 2020, 11, 8451–8458. [CrossRef]

- 26. Gill, M.; Lowrey, T.; Park, J. A high-performance nonvolatile memory technology for stand-alone memory and embedded applications. *IEEE Int. Solid-State Circuits Conf.* 2002, 12, 4.

- Jiang, X.; Ma, Z.; Xu, J.; Chen, K.; Xu, L.; Li, W.; Huang, X.; Feng, D. a-SiN<sub>x</sub>:H-based ultra-low power resistive random access memory with tunable Si dangling bond conduction paths. *Sci. Rep.* 2015, *5*, 15762. [CrossRef]

- Zhang, X.; Ma, Z.; Zhang, H.; Liu, J.; Yang, H.; Sun, Y.; Tan, D.; Li, W.; Xu, L.; Chen, K.; et al. Forming-free performance of a-SiN<sub>x</sub>:H-based resistive switching memory obtained by oxygen plasma treatment. *Nanotechnology* **2018**, *29*, 24.

- 29. Wang, Z.Q.; Xu, H.Y.; Zhang, L.; Li, X.H.; Ma, J.G.; Zhang, X.T.; Liu, Y.C. Performance improvement of resistive switching memory achieved by enhancing local-electric-field near electromigrated Ag-nanoclusters. *Nanoscale* **2013**, *5*, 10. [CrossRef]

- Gao, L.; Li, Y.; Li, Q.; Song, Z.; Ma, F. Enhanced resistive switching characteristics in Al2O3 memory devices by embedded Ag nanoparticles. *Nanotechnology* 2017, 28, 21. [CrossRef]

- Shao, X.L.; Zhou, L.W.; Yoon, K.J.; Jiang, H.; Zhao, J.S.; Zhang, K.L.; Yoo, S.; Hwang, C.S. Electronic resistance switching in the Al/TiOx/Al structure for forming-free and area-scalable memory. *Nanoscale* 2015, 7, 11063–11074. [CrossRef] [PubMed]