# SCIENTIFIC REPORTS

Received: 29 October 2014 Accepted: 03 November 2015 Published: 04 December 2015

## **OPEN** Graphene Distributed Amplifiers: **Generating Desirable Gain for Graphene Field-Effect Transistors**

Hongming Lyu<sup>1,3</sup>, Qi Lu<sup>1</sup>, Yilin Huang<sup>1</sup>, Teng Ma<sup>4</sup>, Jinyu Zhang<sup>1</sup>, Xiaoming Wu<sup>1</sup>, Zhiping Yu<sup>1</sup>, Wencai Ren<sup>4</sup>, Hui-Ming Cheng<sup>4</sup>, Huaqiang Wu<sup>1,2</sup> & He Qian<sup>1,2</sup>

Ever since its discovery, graphene bears great expectations in high frequency electronics due to its irreplaceably high carrier mobility. However, it has long been blamed for the weakness in generating gains, which seriously limits its pace of development. Distributed amplification, on the other hand, has successfully been used in conventional semiconductors to increase the amplifiers' gain-bandwidth product. In this paper, distributed amplification is first applied to graphene. Transmission lines phasesynchronize paralleled graphene field-effect transistors (GFETs), combining the gain of each stage in an additive manner. Simulations were based on fabricated GFETs whose  $f_{\tau}$  ranged from 8.5GHz to 10.5GHz and  $f_{max}$  from 12GHz to 14GHz. A simulated four-stage graphene distributed amplifier achieved up to 4dB gain and 3.5GHz bandwidth, which could be realized with future IC processes. A PCB level graphene distributed amplifier was fabricated as a proof of circuit concept.

The irreplacably high carrier mobility of graphene has been of great interests to the elctronics community and motivated researcher to endeavor on graphene radio frequency (RF) electronic devices<sup>1-3</sup>. Graphene field-effect transistors are widely studied and many research groups have generated cutoff frequencies  $(f_T)$  of hundreds of GHz<sup>4-9</sup>, with the record-high value of 427 GHz<sup>9</sup>.

Poincering works on graphene circuits have led to the demonstration of frequency doublers<sup>10-12</sup>, ambipolor mixers<sup>13</sup> and modulators<sup>14,15</sup>, in which graphene's unique property of electron and hole symmetry is utilized. By superimposing an sinusoidal signal on the minimum conductance point (Dirac point), the electron or the hole branches, the frequency and phase of the output signal could be modulated. Another appliction, the graphene passive circuits (e.g. graphene resistive mixers)<sup>16-19</sup>, attracts more attentions and already shows potential to compete with conventional semiconductor technologies. The authors' group has combined CMOS back-end-of-line (BEOL) processes and graphene to realize a two-layer-routing four-GFET double-balanced mixer IC, which generated IIP3 up to 21 dBm<sup>19</sup>.

However, the overall progress in electronics is greatly hindered by graphene's gapless band structure<sup>1,2</sup>. Obviously, the lack of drain current saturation is detrimental to amplifiers. In particular, even though the  $f_T$  in various groups has reached hundreds GHz, the  $f_{max}$  of GFETs, representing the ability to generate power and voltage amplification, has halted at only 70 GHz<sup>5</sup>. Graphene researchers have tried conventional amplifier architectures. Andersson et al. utilized a matching surface mount inductor on the input gate to yield a return loss of 20 dB. Their work achieved S<sub>21</sub> of 10 at 1 GHz<sup>20</sup>. Guerriero et al. fabricated graphene voltage amplifiers in complementary push-pull configuration, which generated a voltage gain of 11.4 dB and a -3 dB bandwidth of only 70 kHz<sup>21</sup>. In a recent work, a three stage cascade amplifier

<sup>1</sup>Institute of Microelectronics, Tsinghua University, Beijing, 100084, China. <sup>2</sup>Tsinghua National Laboratory for Information Science and Technology (TNList), Beijing, 100084, China. <sup>3</sup>Department of Electrical & Computer Engineering, University of California, San Diego, La Jolla, CA 92093, USA9. <sup>4</sup>Shenyang National Laboratory for Materials Science, Institute of Metal Research, Chinese Academy of Sciences, Shenyang, 110016, China. Correspondence and requests for materials should be addressed to H.L. (email: holyu@ucsd.edu) or H.W. (email: wuhq@tsinghua.edu.cn)

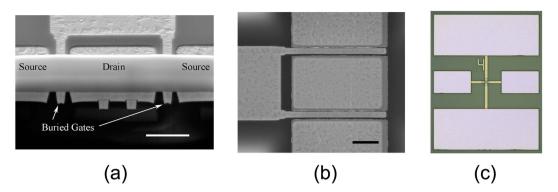

Figure 1. SEM and optical microscope images of the GFET. Cross section (a) and top (b) views of the GFET by SEM. Scale bars: 2  $\mu$ m. (c) Optical microscope image of the GFET with probing pads.

.....

IC achieved a gain of 4 dB at  $4.8 \text{ GHz}^{22}$ . Despite these works, graphene's application in amplifiers with conventional topologies are mostly disappointing.

On the other hand, graphene's IC process has witnessed substantial improvements<sup>12,19,22</sup>. Both Han *et al.* and the authors' group have proposed the multi-layer-routing inverted process for graphene integration, which serves as the foundation for future novel graphene circuit architectures<sup>12,19,22</sup>. The inverted process utilizes CMOS BEOL processes to fabricate circuit and device structures, followed by CVD graphene transfer at the back end of the flow. This process utilizes existing CMOS technologies to the maximum extend and greatly reduces contaminations and potential damages to graphene.

In this paper, the graphene distributed amplifer is proposed to solve its long-standing weakness in amplification. Engineers have successfully applied distributed amplication to conventional semiconductor technologies to increase the amplifiers' gain-bandwidth-product<sup>23-26</sup>, which could not be increased simply by parallelizing transistors, because the increase in the transconductance is compensated for the corresponding increase in the input and output capacitances. The distributed amplifiers place transistors along artificial transmission lines, adding the  $g_m$  of each transistor in a phase-synchronized manner. Therefore, the bandwidth-gain-product could be increased. While the gain of a conventional cascade amplifier is the product of the gain of each stage, distributed amplifiers' gain is directly proprotional to the number of stages. This trait makes distributed amplification scheme especially suitable for graphene, as each GFET stage generates very modest or less-than-unity gains. The otherwise product of the gain of each stage would be mediocre.

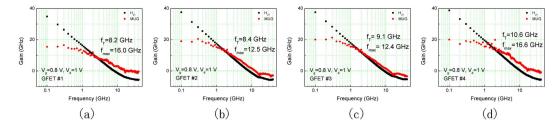

Four GFETs with gate lengths of 300 nm through 500 nm have been fabricated, which generated  $f_T$  ranging from 8.2 GHz to 10.6 GHz and  $f_{max}$  12.4 GHz to 16.6 GHz without de-embedding (Misallignment existed in this batch of devices, breaking the relationship between the  $f_T$  and  $f_{max}$  metrics and the gate length). The  $f_{max}$  exceeded  $f_T$  in these works due the low resistance of the buried gates<sup>5</sup>. Measured S-parameters of the GFETs were used in graphene distributed amplifier simulations. The circuit schematic employed artificial transmission lines formed by lumped inductors and capacitors to phase-syncronized each GFET stage. Simulations generated up to 4 dB gain and and 3.5 GHz bandwidth, which is the first graphene wide-band amplification dicussed in literature. These designs could be realized by IC technologies with precise models. However, at the present stage, a PCB-level distributed amplifer was fabricated. As individual GFETs and bonding wires were not precisely modeled, the passive components of any small values were avoided. Redesign of the passive components sacrificed the gain, while the bandwidth was maintained. The measured performance was in agreement with circuit simulations.

#### **Results and Discussion**

**Graphene Field-Effect Transistors.** GFETs in buried-gate structure have been fabricated. Crosssection and top views of a 400 nm-gate-length GFET structure are shown in Fig. 1a,b, respectively. Chemical-mechanical-planarization (CMP) process flattened the wafer surface, which guarrenteed the successfulness of the following graphene transfer process. Cross section made by focused-ion-beam (FIB) indicated the thickness of the gate of 600 nm. Such thickness effectively lowers the gate series resistance, which is favourable from  $f_{max}$  point of view. The GFETs employed a two-finger structure with each finger  $6\mu m$  wide. The gate dielectric employed HfO<sub>2</sub> with equivalent oxide thickness (EOT) of 2 nm formed directly on the buried gate. Graphene was synthensized by CVD method and transferred by "bubbling" method as previously reported (details in Method)<sup>27,28</sup>. The channel of the GFETs was defined by contact photolithography and contacts by electron beam photolithography (EBL). The contacts were 40 nm Pt (details in Method).

The probing pads were  $80\mu m \times 80\mu m$  with  $100\mu m$  pitch in ground-signal-ground (GSG) layout, as shown in Fig. 1c. All devices have not gone through passivation step for convenience. Several reports have shown various dielectrics, such as Si<sub>3</sub>N<sub>4</sub><sup>29</sup>, BN<sup>30</sup>, Al<sub>2</sub>O<sub>3</sub><sup>31</sup>, etc., could effectively protect graphene devices. Future works should consider passivation to increase the stability and reliability of graphene

**Figure 2. RF Performance of the GFETs.**  $f_T$  and  $f_{max}$  of GFET #1 (**a**), GFET #2 (**b**), GFET #3 (**c**) and GFET #4 (**d**).

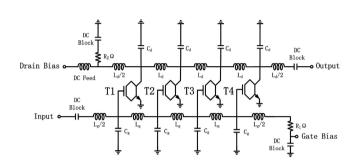

Figure 3. Schematic of a four-stage graphene distributed amplifier.

devices. S-parameters have been measured on chip up to 40 GHz under ambient atmosphere using Agilent N8230C network analyzer. Four GFETs labeled as GFET #1~4 featured gate lengths of 300 nm, 500 nm, 500 nm and 400 nm, respectively, and demonstrated  $f_T/f_{max}$  of 8.2 GHz/16 GHz, 8.4 GHz/12.5 GHz, 9.1 GHz/12.4 GHz, 10.6 GHz/16.6 GHz, respectively, as shown in Fig. 2. These results were without de-embedding. The devices were then cut out of the chip with the probing pads which enabled wire bonding in following works.

**Distributed Amplifiers.** Figure 3 shows the schematic of a four-stage graphene distributed amplifier. Artificial transmission lines formed by lumped elements are periodically loaded with the gate and drain terminals of the GFETs, forming the so-called gate and drain transmission lines. An RF signal applied at the input end of the gate line travels down to the other end, where it is absorbed by the terminating impedance. The signals sampled by the gate of a GFET at a different location with different phases is transferred to the drain line. The two gate and drain transmission lines pocess the same phase velocity. Therefore, the gains of each stage are combined in the forward-travelling direction. The backward-traveling signal on the drain line is absorbed at the frontier end. As long as the gain per section is greater than the corresponding loss, the overall gain of a distributed amplifier can be increased even without limit. While the gain of conventional cascade amplifiers are the product of each stage, distributed amplifiers increases the gain proportional to the number of stages, which is especially attractive to graphene, since the otherwise multiplication could not generate satisfying gains. The four GFETs in the schematic are labeled as T1~4. Passive components,  $C_d$ ,  $C_g$ ,  $L_d$  and  $L_g$ , constitute the gate and drain artificial lines.  $R_1$  and  $R_2$  form the two terminating resistances.

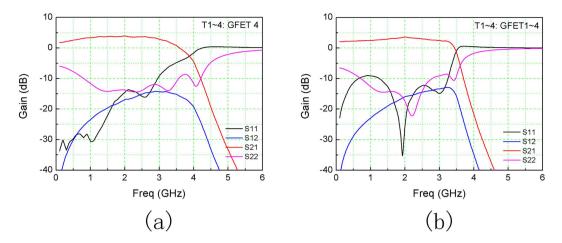

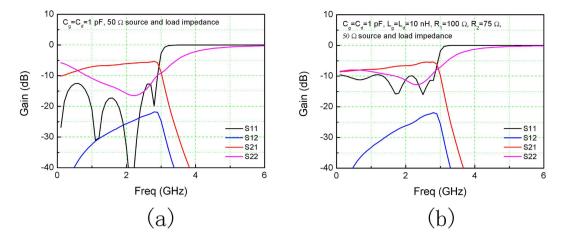

Circuit simulation based on measured S-parameters of the GFETs was performed in a standard circuit simulator, Agilent Advanced Design System (ADS). In Simulation #1, T1 through T4 all employed GFET #4, respresenting ideal situations when GFETs are exactly identical. The optimization was performed with three goals: 1) S21 > 5 dB; 2) S11 < -10 dB; 3) S22 < -10 dB. Variables were the terminating resistances, R<sub>1</sub>, R<sub>2</sub>, and the lumped passive components, C<sub>g</sub>, C<sub>d</sub>, L<sub>g</sub>, L<sub>d</sub> (details in Method). Source and load impedances were set as R<sub>1</sub> and R<sub>2</sub>, respectively. Simulation #1 achieved S21 of roughly 4 dB and 3.5 GHz bandwidth, as shown in Fig. 4a. Varibles of the passive components are shown in Table 1. R<sub>1</sub>, R<sub>2</sub>, C<sub>g</sub>, C<sub>d</sub>, L<sub>g</sub> and L<sub>d</sub> resulted in 1.28 k $\Omega$ , 78.5  $\Omega$ , 0.01 pF, 0.7 pF, 105 nH and 7.6 nH, respectively. Simultion #1 represents situations when GFETs are exactly identical (T1~4: GFET #4). After the demonstration of high-performance individual GFETs in many lab works, efforts in graphene electronics society should now emphasize reproducibility and reliability to support the potential mass production.

Another simulation, Simulation #2, was launched closer to real circumstances. GFET #1 through #4 were assigned to T1 through T4, respectively. The setup was the same with Simulation #1, which generated S21 of 3 dB and 3.5 GHz bandwidth, as shown in Fig. 4b. The variables,  $R_1$ ,  $R_2$ ,  $C_g$ ,  $C_d$ ,  $L_g$  and  $L_d$  resulted in 1.28 k $\Omega$ , 58  $\Omega$ , 0.01 pF, 1.2 pF, 86 nH and 7.2 nH, respectively, as shown in Table 2, being very close to Simulation #1.

Figure 4. Simulation results. Magnitude of the S-parameters of Simulation #1 (a) and #2 (b).

|               | T1             | T2             | T3               | T4             | Cg      | C <sub>d</sub> | $L_{g}$ | L <sub>d</sub> |

|---------------|----------------|----------------|------------------|----------------|---------|----------------|---------|----------------|

| Simulation #1 | GFET #4        | GFET #4        | GFET #4          | GFET #4        | 0.01 pF | 0.7 pF         | 105 nH  | 7.6 nH         |

| Simulation #2 | GFET #1        | GFET #2        | GFET #3          | GFET #4        | 0.01 pF | 1.2 pF         | 86 nH   | 7.2 nH         |

|               | R <sub>1</sub> | R <sub>2</sub> | Source Impedance | Load Impedance |         |                |         |                |

| Simulation #1 | 1280 Ω         | 78.5 Ω         | $1280\Omega$     | 78.5 Ω         |         |                |         |                |

| Simulation #2 | 1280 Ω         | 58 Ω           | $1280\Omega$     | 58 Ω           |         |                |         |                |

#### Table 1. Variables in Simulation #1 and #2.

|               | T1             | T2             | T3               | T4             | Cg   | C <sub>d</sub> | $L_{g}$ | L <sub>d</sub> |

|---------------|----------------|----------------|------------------|----------------|------|----------------|---------|----------------|

| Simulation #3 | GFET #1        | GFET #2        | GFET #3          | GFET #4        | 1 pF | 1 pF           | 9.8 nH  | 8.5 nH         |

| Simulation #4 | GFET #1        | GFET #2        | GFET #3          | GFET #4        | 1 pF | 1 pF           | 10 nH   | 10 nH          |

|               | R <sub>1</sub> | R <sub>2</sub> | Source Impedance | Load Impedance |      |                |         |                |

| Simulation #3 | 73.1 Ω         | 68.5 Ω         | $50\Omega$       | 50 Ω           |      |                |         |                |

| Simulation #4 | 100 Ω          | $75 \Omega$    | 50 Ω             | 50 Ω           |      |                |         |                |

#### Table 2. Variables in Simulation #3 and #4.

Simulation #1 and #2 for the first time demonstrated wide-band graphene amplifiers in literature. Both simulations were based on measured S-parameters of the GFETs, illustrating the feasibility of wide-band graphene amplifiers with present averge-performance GFETs. The passive component were subjected to the following equation that guarantees the phase-synchronization requirement:

$$\mathbf{C} \cdot \mathbf{L} = (C_g + C_{gate}) \cdot L_g = (C_d + C_{drain}) \cdot L_d \tag{1}$$

where C and L represents the capacitance and inductance at each node. For Simulation #1,  $C_g$ ,  $C_d$ ,  $L_g$  and  $L_d$  were 0.01 pF, 0.7 pF, 105 nH and 7.6 nH, respectively. Miller effects obscured  $C_{drain}$  and the gate oxide capacitance was roughly 0.08 pF, caculated according to the dimension and gate dielectric of the 400 nm GFET.  $C_{gate}$  was further decreased due to quantum capacitance effect<sup>32,33</sup>, therefore qualifying equation (1). These simulations assumed that wideband matching sections were used: the source and load impedences were set as  $R_1$  and  $R_2$ , which roughly equaled characteristic impedences of the gate and drain transmission lines, respectively, caculated as  $\sqrt{\frac{L}{C}}$ . The bandwidth of a distributed amplifier is determined by the cutoff frequency of the artificial transmission line,  $f_c = 1/\pi \sqrt{LC}^{26}$ . Following works should realize these designs by IC technology, which has a precise control of the parasitics and models of the active and passive components.

On the other hand, efforts have been made in this work to realize a PCB-level graphene distributed amplifier, which meets problems such as precise GFET models, the choice of discrete lumped passive components, and bonding wires. Any variations are likely to destroy the phase-synchronization between

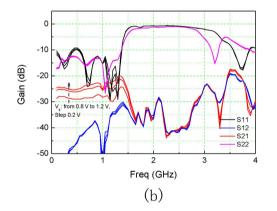

Figure 5. Simulation results. Magnitude of the S-parameters of Simulation #3 (a) and #4 (b).

(a)

the gate and drain transmission lines, especially when any of the passive components values are too small, e.g.,  $C_g$  in Simulation #1 and #2.

Firstly, small values for any of  $C_g$ ,  $C_d$ ,  $L_g$ ,  $L_d$  are avoided in the simulations, Simulation #3 and #4. In particular,  $C_g$  was fixed at 1 pF (i.e., minimum value for dicrete capacitances in 0805 package). The terminating impedances were both set at 50  $\Omega$ . Simulation #3 used  $C_g = C_d = 1$  pF and  $R_1 = R_2 = 50 \Omega$ . The simulation result is shown in Fig. 5a, and values of the variables in Table 2. Due the large  $C_g$ , the gain decreased to -10~-5 dB and the bandwidth remained at 3 GHz. Simulation #4 further avoided matching sections at the input and output terminals by employing 50  $\Omega$  source and load impedence.  $C_g$  and  $C_d$  were 1 pF, and  $L_g$  and  $L_d$  10 nH, which are common discrete devices. The simulation result is demonstrated in Fig. 5b. Extraordinarily large capacitances were used in these simulations, because otherwise any variations could easily break the phase-synchronization requirement. In turn, it sacrificed the gain.

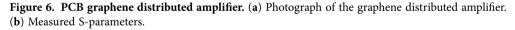

A PCB-level graphene distributed amplifier was fabricated according to Simulation #4, which featured approximately  $5 \text{ cm} \times 3 \text{ cm}$  dimension, as shown in Fig. 6a. It used FR4 laminate. The capacitors and inductors were in 0805 package. Indidivual GFETs were cut out of the chip and bonded to the PCB board. The bonding wires were limited to about 2 mm, which introduced about 1 nH/mm parasitic effects. After calibration with the short-open-load-through (SOLT) process to eliminate the parasitic effects of the wiring, Agilent N8230C network analyzer were used to characterize the distributed amplifier sample up to 10 GHz. The drain line was biased at 1 V and gate voltage varied from 0.8 V to 1.2 V. The DC biases were induced through AC block inductors.

Test results are shown in Fig. 6b. Maximum gain of -20 dB and bandwidth of 1.5 GHz were obtained. Even though large discrepencies exist, measurement results reassemble the simulation #4. The S21 is dependent on the gate bias V<sub>g</sub>. It increases with each GFET's transconductance. The charateristic impedences of the artificial transmission lines are approximated as  $\sqrt{\frac{L_g}{C_g}} = \sqrt{\frac{L_d}{C_d}} = 100\Omega$ , which are close to 50  $\Omega$  and therefore reduce return loss at the source and drain terminals. Several reasons deteri-

close to  $50\Omega$  and therefore reduce return loss at the source and drain terminals. Several reasons deteriorates the performance as compared to simulation results. Distribution effect took place at GHz frequencies, considering the PCB laminate's size comparable to the corresponding wavelength. Besides, the bonding wires have not yet been considered in the simulations.

Even though the fabricated work somewhat reassembles a real amplifier, future graphene distributed amplifers should be realized in IC technologies, where precise models of GFETs and passive components should be addressed. Besides, on-chip waveguides could be considered to replace artifical transmission lines. They might further reduces losses.

Distributed amplifiers over the past decades have successfully been applied in compound semiconductor and CMOS technologies<sup>23-26</sup>. Their application in graphene, a candidate for next-generation semiconductor technology, is especially promising. It conquers graphene's longstanding problem of being hard to generate gains. In this work, simulations of graphene distributed amplifiers were first performed. A four-stage graphene distributed amplifer based on measured S-parameter of GFETs achieved 4dB gain and 3.5 GHz bandwidth. We predict that these simulations could be realized by future graphene IC techonologies with precise models. A PCB graphene distributed amplifier was fabricated with large passive components as a proof of concept. Test results of the sample reassembled the corresponding simulation, in which the bandwidth maintained and the gain was sacrificed. The domonstrated works illustrate the principle of graphene distributed amplifiers and proves their feasiblity in future mature IC processes. It is of signicance to the graphene electronics community.

### Methods

**Graphene Synthesis.** Graphene in this work was synthesized by CVD method on Pt foils as previously reported. Large scale monolayer graphene films were grown on  $180 \mu$ m thick Pt foils (99.9 wt % metal basis,  $10 \text{ mm} \times 10 \text{ mm}$ ) by ambient-pressure chemical vapor deposition (APCVD) method. The growth temperature was  $1000 \,^{\circ}$ C and CH<sub>4</sub>/H<sub>2</sub> flow rates were set at 4.5/500 sccm. After growth, Pt foils were quickly pulled out of the high temperature area<sup>27,28</sup>. Electrochemical delamination in NaOH solution, the so called "bubbling" method<sup>28</sup>, was used to transfer graphene on a die-by-die basis, limited by the maximum size of the Pt foil.

**GFET Fabrication.** The fabrication was based on 200 mm CMOS platform. Conventional BEOL processes fabricated buried gate/source/drain structures made of W.  $HfO_2$  with equivalent oxide thickness (EOT) of 2 nm was deposited as the gate oxide by atomic layer deposition (ALD) method. After graphene transfer, the channel of the GFETs was defined by contact photolithography and the residual graphene was removed by oxygen plasma etching. The source/drain contact was defined by electron-beam-lithography (EBL). Due to misalignment, certain source-gate and drain-gate overlaps existed in this patch of fabrication. The contacts were formed by lift-off process. The source/drain regions underwent 5 min UVO treatment before the sputtering of 40 nm Pt. The high work function of W induced more doping to graphene and UVO treatment enhanced the metal-graphene's binding to each other. TML pattern characterization showed the lowest contact resistance of 500  $\Omega\mu$ m.

**Circuit Simulation in Agilent ADS.** The Advanced Design System software was version 2012.08. In optimization toolset, the simulated anealing algorithm was used. Three goals were typically used: 1)  $S_{21} > 5 dB$ ; 2)  $S_{11} < -10 dB$ ; 3)  $S_{22} < -10 dB$ , in the frequency span from 500 MHz to 3 GHz. The weight of the each goals could be independently swiched.

#### References

- 1. Wu, Y., Farmer, D. B., Xia, F. & Avouris, P. Graphene electronics: Materials, devices, and circuits. *Proceedings of the IEEE* 101, 1620–1637 (2013).

- 2. Fiori, G. et al. Electronics based on two-dimensional materials. Nature nanotechnology 9, 768-779 (2014).

- 3. Schwierz, F. Graphene transistors. Nature nanotechnology 5, 487-496 (2010).

- 4. Wu, Y. et al. State-of-the-art graphene high-frequency electronics. Nano Letters 12, 3062-3067 (2012).

- 5. Guo, Z. et al. Record maximum oscillation frequency in C-face epitaxial graphene transistors. Nano letters 13, 942–947 (2013).

- 6. Wu, Y. et al. High-frequency scaled graphene transistors on diamond-like carbon. Nature 472, 74–78 (2011).

- 7. Liao, L. et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 467, 305-308 (2010).

- 8. Lin, Y. M. et al. 100-GHz transistors from wafer-scale epitaxial graphene. Science 327, 662–662 (2010).

- 9. Cheng, R. et al. High-frequency self-aligned graphene transistors with transferred gate stacks. Proceedings of the National Academy of Sciences 109, 11588-11592 (2012).

- 10. Wang, H., Nezich, D., Kong, J. & Palacios, T. Graphene frequency multipliers. Electron Device Letters 30, 547-549 (2009).

- 11. Parrish, K. N. & Akinwande, D. Even-odd symmetry and the conversion efficiency of ideal and practical graphene transistor frequency multipliers. *Applied Physics Letters* **99**, 223512 (2011).

- 12. Lv, H. et al. Inverted process for graphene integrated circuits fabrication. Nanoscale 6, 5826-5830 (2014).

- 13. Wang, H., Hsu, A., Wu, J., Kong, J. & Palacios, T. Graphene-based ambipolar RF mixers. *Electron Device Letters* 31, 906–908 (2010).

- 14. Yang, X., Liu, G., Balandin, A. A. & Mohanram, K. Triple-mode single-transistor graphene amplifier and its applications. ACS Nano 4, 5532–5538 (2010).

- 15. Lee, S., Lee, K., Liu, C. H., Kulkarni, G. S. & Zhong, Z. Flexible and transparent all-graphene circuits for quaternary digital modulations. *Nature communications* **3**, 1018 (2012).

- Habibpour, O., Vukusic, J. & Stake, J. A 30-GHz integrated subharmonic mixer based on a multichannel graphene FET. *IEEE Transactions on Microwave Theory and Techniques* 61, 841–847 (2013).

- 17. Lin, Y. M. et al. Wafer-scale graphene integrated circuit. Science 332, 1294-1297 (2011).

- 18. Moon, J. S. et al. Graphene FETs for zero-bias linear resistive FET mixers. IEEE Electron Device Letters 34, 465-467 (2013).

- 19. Lyu, H. et al. Double-Balanced Graphene Integrated Mixer with Outstanding Linearity. Nano letters. doi: 10.1021/acs. nanolett.5b02503 (2015).

- 20. Andersson, M. A., Habibpour, O., Vukusic, J. & Stake, J. 10 dB small-signal graphene FET amplifier. *Electronics letters* 48, 861–863 (2012).

- 21. Guerriero, E. et al. Graphene audio voltage amplifier. Small 8, 357-361 (2012).

- 22. Han, S. J., Garcia, A. V., Oida, S., Jenkins, K. A. & Haensch, W. Graphene radio frequency receiver integrated circuit. Nature communications 5 (2014).

- 23. Ayasli, Y. et al. A monolithic GaAs 1-13-GHz traveling-wave amplifier. *IEEE Transactions on Microwave Theory and Techniques* 30, 976–981 (1982).

- 24. Niclas, K. B. et al. On theory and performance of solid-state microwave distributed amplifiers. *IEEE Transactions on Microwave Theory and Techniques* 31, 447–456 (1983).

- Majidi-Ahy, R. et al. 5–100 GHz InP coplanar waveguide MMIC distributed amplifier. IEEE Transactions on Microwave Theory and Techniques 38, 1986–1993 (1990).

- 26. Ballweber, B. M., Ravi G. & David J. A. A fully integrated 0.5–5.5 GHz CMOS distributed amplifier. *IEEE J. Solid-St. Circ.* 35, 231–239 (2000).

- 27. Xiao, K., Wu, H., Lv, H., Wu, X. & Qian, H. The study of the effects of cooling conditions on high quality graphene growth by the APCVD method. *Nanoscale* **5**, 5524–5529 (2013).

- 28. Gao, L. *et al.* Repeated growth and bubbling transfer of graphene with millimetre-size single-crystal grains using platinum. *Nature communications* **3**, 699 (2012).

- 29. Lee, J. et al. Multi-finger flexible graphene field effect transistors with high bendability. Applied Physics Letters 101, 252109 (2012).

- 30. Wang, L. *et al.* Negligible environmental sensitivity of graphene in a hexagonal boron nitride/graphene/h-BN sandwich structure. *ACS Nano* **6**, 9314–9319 (2012).

- 31. ZurutuzaáElorza, A. Highly air stable passivation of graphene based field effect devices. Nanoscale 7, 3558–3564 (2015).

- 32. Dröscher, S. et al. Quantum capacitance and density of states of graphene. Applied Physics Letters 96, 152104 (2010).

- 33. Xu, H. et al. Quantum capacitance limited vertical scaling of graphene field-effect transistor. ACS Nano 5, 2340-2347 (2011).

#### Acknowledgements

This research was supported by the National Science and Technology Major Project (2011ZX02707), the National Basic Research Program (2011CBA00600, 2013CBA01604), and the National Natural Science Foundation (61474072).

#### **Author Contributions**

H.M.L. and Z.P.Y. conveiced the project. H.M.L., X.M.W., H.Q.W. and H.Q. designed the fabrication process. H.M.L. and Q.L. fabricated the GFET and performed the electrical measurement. H.M.L., Q.L., Y.L.H. and J.Y.Z. performed the simulation. T.M., W.C.R. and H.M.C. synthesized the graphene. H.M.L. wrote the manuscript.

#### Additional Information

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Lyu, H. *et al.* Graphene Distributed Amplifiers: Generating Desirable Gain for Graphene Field-Effect Transistors. *Sci. Rep.* **5**, 17649; doi: 10.1038/srep17649 (2015).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/