# **ARTICLE**

1

https://doi.org/10.1038/s41467-022-31849-5

OPEN

# Dirac-source diode with sub-unity ideality factor

Gyuho Myeong <sup>1,6</sup>, Wongil Shin<sup>1,6</sup>, Kyunghwan Sung<sup>1</sup>, Seungho Kim<sup>1</sup>, Hongsik Lim<sup>1</sup>, Boram Kim<sup>1</sup>, Taehyeok Jin<sup>1</sup>, Jihoon Park<sup>1</sup>, Taehun Lee<sup>1</sup>, Michael S. Fuhrer <sup>2</sup>, Kenji Watanabe <sup>3</sup>, Takashi Taniguchi <sup>3</sup>, Fei Liu <sup>4,5 ≥</sup> & Sungjae Cho <sup>1≥</sup>

An increase in power consumption necessitates a low-power circuit technology to extend Moore's law. Low-power transistors, such as tunnel field-effect transistors (TFETs), negative-capacitance field-effect transistors (NC-FETs), and Dirac-source field-effect transistors (DS-FETs), have been realised to break the thermionic limit of the subthreshold swing (SS). However, a low-power rectifier, able to overcome the thermionic limit of an ideality factor ( $\eta$ ) of 1 at room temperature, has not been proposed yet. In this study, we have realised a DS diode based on graphene/MoS<sub>2</sub>/graphite van der Waals heterostructures, which exhibits a steep-slope characteristic curve, by exploiting the linear density of states (DOSs) of graphene. For the developed DS diode, we obtained  $\eta$  <1 for more than four decades of drain current ( $\eta_{ave\_4dec}$  <1) with a minimum value of 0.8, and a rectifying ratio exceeding 10<sup>8</sup>. The realisation of a DS diode represents an additional step towards the development of low-power electronic circuits.

<sup>&</sup>lt;sup>1</sup> Department of Physics, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea. <sup>2</sup> ARC Centre of Excellence in Future Low-Energy Electronics Technologies, and School of Physics and Astronomy, Monash University, Clayton, Victoria 3800, Australia. <sup>3</sup> National Institute for Materials Science, Namiki, Tsukuba, Ibaraki 305-0044, Japan. <sup>4</sup> School of Integrated Circuits, Peking University, Beijing 100871, China. <sup>5</sup> Beijing Advanced Innovation Center for Integrated Circuits, Beijing 100871, China. <sup>6</sup> These authors contributed equally: Gyuho Myeong, Wongil Shin, Kyunghwan Sung. <sup>∞</sup> email: feiliu@pku.edu.cn; sungjae.cho@kaist.ac.kr

ower consumption of integrated digital devices sets the ultimate limit to downscaling and Moore's Law<sup>1</sup>. Reducing power consumption has been thwarted by fundamental limits on the operating voltage set by thermionic emission<sup>2</sup>. For an ideal thermionic device, the dependence of current I on voltage V is expressed through the subthreshold swing  $SS = [dlog10(I)/dV]^{-1} = (k_BT/q) log(10) \approx 60 \text{ mV/dec}$  at room temperature, where  $k_BT$  is the thermal energy and q is the elemental charge.

Two-dimensional (2D) van der Waals (vdW) materials<sup>3,4</sup> have been proposed for various schemes to overcome the thermionic limit (SS = 60 mV/dec) of metal-oxide-semiconductor field-effect transistors (MOSFETs) in nonconventional transistors such as TFETs, NC-FETs, and DS-FETs<sup>5-14</sup>. In particular, DS-FETs use the linear energy dispersion relationship of graphene, producing a super-exponential change in the DOS with energy<sup>15</sup>. As a result, DS-FETs have achieved a smaller SS than that of a MOSFET, with a large drive current<sup>11-14</sup>.

Integration of heterogeneous electronic components on a single low-power-consumption platform is highly desirable to enable applications such as the Internet of Things (IoT). Schottky diodes are important electronic components with low operation voltage and high current 16, and have many useful applications such as rectifiers, mixers, selectors, switches, photodetectors and solar cells<sup>16</sup>. Although there has been considerable development of low-power transistors, steep-slope diode (or triode) rectifiers that overcome the thermionic limit  $(\eta < 1)$  of conventional diodes have not been proposed yet, but will be necessary for device integration with low-power transistors. Herein, we propose a DS diode as an essential element for low-power circuits. The DS injects cold electrons without a long thermal tail above the potential barrier in the channel (Supplementary Figure 1). Our DS diode consists of a graphene/MoS<sub>2</sub>/graphite heterojunction, where graphene acts as a cold electron injector, whereas the graphite/MoS<sub>2</sub> interface provides a Schottky barrier for rectification. The MoS<sub>2</sub> channel was chosen because of its high-gate tunability and mobility<sup>17</sup>. The minimum and average values of η for the DS diode are 0.78 and less than 1 over more than four decades of current at room temperature (nave 4dec < 1), respectively, with a high rectifying ratio (>108).

# **Results**

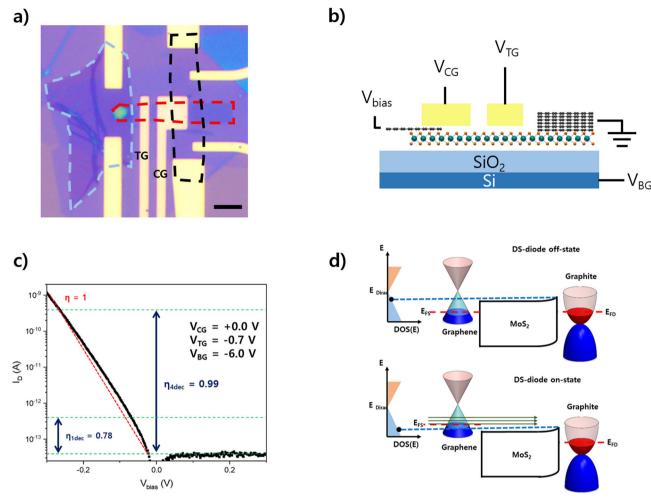

Characteristics of Dirac-source diode. The DS diode device (Fig. 1a, b) consists of four components: (i) an n-type monolayer MoS<sub>2</sub> channel (Supplementary Fig. 3), (ii) a graphene DS neutral at a zero gate voltage, (iii) a graphite drain-contact to form a Schottky barrier between the graphite and monolayer MoS<sub>2</sub> for electrical rectification with a bias voltage, and (iv) metal (back, top, and control) gate electrodes to tune the Fermi levels of 2D materials. Two-dimensional van der Waals epitaxy was performed inside an Ar-filled glovebox until the heterostructure was encapsulated by hexagonal boron nitride (hBN) to avoid any contamination through air exposure or chemicals (Supplementary Fig. 2). Unlike a metal contact, a graphite contact with the monolayer MoS<sub>2</sub> forms a non-reactive clean interface<sup>18</sup> (Supplementary Fig. 4). Cr/Au electrodes were placed only in the region where graphite or graphene encapsulated by hBN exists.

The diode has a local top-gate, control-gate and a global back-gate. The top gate only modulates the channel of the monolayer  $MoS_2$  band while the control-gate tunes the regions of the monolayer  $MoS_2$  channel and part of graphene overlapped with  $MoS_2$ , respectively. The global back-gate affects the graphene/ $MoS_2$ /graphite heterostructure. The gate-dependent electrical measurements (Supplementary Fig. 5) indicate that the Dirac point of hBN-encapsulated graphene is located at  $V_{BG} = +1.9 \ V$ .

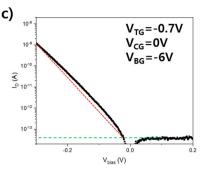

Figure 1c presents the characteristic drain current ( $I_D$ ) versus bias voltage ( $V_{bias}$ ) curve for the DS diode at  $V_{BG}=-6\,V$ ,  $V_{CG}=0\,V$  and  $V_{TG}=-0.7\,V$ . At  $V_{BG}=-6\,V$ , graphene is p-type. When a bias voltage is applied to the graphene, electrons are injected from the p-type graphene source into the graphite drain. Note the electrons in the graphene source contributing to the current injection should have energy above the green dotted line (Fig. 1d) which is determined by the top of the  $MoS_2$  conduction band edge while not all the electrons above  $E_F$  in graphene contribute to the current. The injected current density from graphene is given by:

$$J(E) \propto M_0 |E - E_D| f(E - E_{ES})$$

Where  $E_D$  is the Dirac point and  $E_{FS}$  is the Fermi level of graphene. So, as the channel barrier gets lower than the Dirac point, available density of states from graphene around  $E = E_{top}$  $(E_{top})$  is the top of channel barrier) increases due to  $M_0|E-E_D|$ . So, injected current increased super-exponentially and the device works as a DS-FET. The electrical measurements reveal a nearly Ohmic graphene/MoS<sub>2</sub> contact and a Schottky barrier of the graphite/MoS<sub>2</sub> contact (Supplementary Fig. 6). When a negative back-gate voltage is applied, the Schottky barrier height increases and the device current is mainly modulated by the Schottky barrier at the interface between the graphite and monolayer MoS<sub>2</sub>. Although the Ohmic contact behaviour between graphene and monolayer MoS2 was observed in electrical measurements, to fully understand the band diagram at the graphene/monolayer MoS<sub>2</sub> interface and its gate dependence, further studies are needed.

The performance of a Schottky diode is mainly characterised by two figures of merit. One is the rectifying ratio, which refers to the ratio between the on and off currents ( $R = \frac{I_{on}}{I_{off}}$ ), whereas the other is  $\eta$ , which is the slope representing the change in drain current with a bias voltage and can be obtained from the following Schottky diode equation:

$$I_{\rm D} = I_{\rm S} \left( 1 - e^{qV_{\rm bias}/\eta k_{\rm B}T} \right),\tag{1}$$

where q is the elementary charge,  $V_{\rm bias}$  is the applied bias voltage,  $\eta$  is the ideality factor,  $k_{\rm B}$  is the Boltzmann constant, T is the temperature, and  $I_{\rm D}$  and  $I_{\rm S}$  are the drain and leakage currents, respectively. Equation (1) corresponds to  $SS = (\eta k_{\rm B}T/e)\log(10)$  hence values  $\eta < 1$  correspond to SS below the thermionic limit. The characteristic curve at a negative gate voltage in Fig. 1b exhibits rectification behaviour with  $\eta < 1$  observed over more than four decades of drain current, a minimum  $\eta$  of 0.78, and a large rectifying ratio (>10<sup>8</sup>).

Steep-slope switching mechanism of Dirac-source diode. To explore the switching mechanism of the DS diode, we developed an analytical formula for the ideality factor and performed numerical device simulations (Supplementary Note 6). Both the two methods show that the ideality factor less than 1 is obtained in the DS diode due to the linear density of states of graphene. The switching slope of a diode is determined by the energydependent current density injected from an electrode, which is related to DOS and the distribution function. Graphene has a linear energy-dependent electronic DOS near the Dirac point, which is different from conventional metals with a constant DOS around the Fermi level. Therefore, the thermal tail of the Boltzmann distribution function is suppressed by the Dirac point tuned to the off-state region by doping. Namely, as the bias voltage is decreased on the graphene electrode as shown in Fig. 1d, the part of current density related to the distribution function is increased exponentially similar to conventional

**Fig. 1 Device structure, characteristic curve, and band diagram of DS diode. a** Optical image of graphene/MoS<sub>2</sub>/graphite heterojunction diode. Grey, red, and black dashed lines indicate graphite, monolayer MoS<sub>2</sub>, and graphene, respectively. We used graphene as a source and graphite as a drain. The top-gate(TG) and control-gate(CG) were placed for gate modulation of the MoS<sub>2</sub> channel and graphene/MoS<sub>2</sub> overlapped region, respectively. Scale bar, 5 um. **b** Schematic image of graphene/MoS<sub>2</sub>/graphite heterojunction diode. **c** Characteristic drain current( $I_D$ )-bias voltage( $V_{bias}$ ) curve in our device, which exhibits ideality factor( $\eta$ ) = 0.78 in 1 decade of current and an average  $\eta$  < 1 in more than four decades of current, i.e.,  $\eta_{ave\_4dec}$  < 1. The rectifying ratio of our device is larger than 10<sup>8</sup>. **d** Band diagram of DS Schottky diode, which explains the working principle of cold electron injection from graphene. E<sub>Dirac</sub>, DOS, E<sub>FS</sub>, and E<sub>FD</sub> indicate Energy at the Dirac point, the density of states, Fermi level at the source side, and Fermi level at the drain side, respectively. Blue dashed line and green arrows indicate MoS<sub>2</sub> energy window level and expression of rapid increment of current flow.

metals, which results in the ideal factor limit of 1. While, the injected DOS over the top of the channel barrier is also increased linearly from off-state to on-state, as shown in Fig. 1d. Therefore, the current is increased super-exponentially and the ideal factor below 1 is obtained in the diode with graphene electrode as the injection source.

Therefore, the switching slope of a diode, i.e.  $\eta < 1$ , is obtained in the diode with a graphene electrode as the cold electron injection source because of the linear DOS of the DS. Detailed simulation results are presented in Supplementary Fig. 7. Quantum transport simulations show that the DS diode has promising device performance. The ideality factor as small as 0.69 is obtained in the simulated DS diode and is less than 1 in more than five decades of current at room temperature.

The on-state current is larger than  $10^3 \,\mu\text{A}/\mu\text{m}$  and the rectifying ratio is over  $10^7$ .

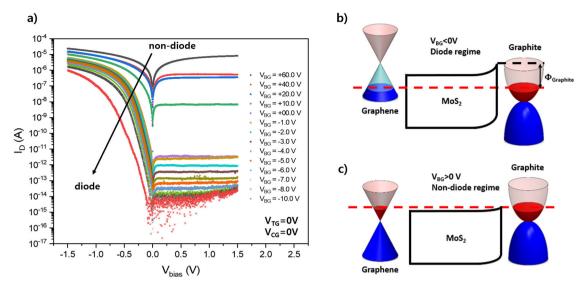

Properties of asymmetric graphene/MoS $_2$  and graphite/MoS $_2$  contacts. Figure 2a presents the  $\rm I_D\text{-}V_{bias}$  characteristic curve of the DS diode at different back-gate voltages. For the DS diode to work

as a diode, an asymmetric Schottky barrier height between the source and drain is necessary 19-22. To satisfy this condition, we placed asymmetric graphene and graphite contacts with the monolayer MoS<sub>2</sub> channel with gates. Without gate modulation, graphene has a work function of 4.3-4.7 eV from a monolayer to a few layers<sup>23–25</sup>. Because the work function of graphene (~4.3 eV) does not differ significantly from the electron affinity of MoS2 (~4.2 eV)<sup>26-29</sup>, the Schottky barrier height at the graphene/MoS<sub>2</sub> interface is negligible, compared to the Schottky barrier height at the graphite/MoS<sub>2</sub> interface. This also indicates that the Dirac point of pristine graphene is located near the conduction band edge of MoS<sub>2</sub>. As shown in Supplementary Fig. 10, in case of the metal/ntype semiconductor junction, the positive voltage on metal became forward bias. In our case, we applied bias voltage on the graphene side, and negative bias became forward bias, i.e., positive bias on the graphite side is forward bias, which indicates the Schottky barrier between the graphite/MoS<sub>2</sub> junction is dominated in our device. Supplementary Fig. 6 indicates that the graphene/MoS<sub>2</sub> device shows an almost Ohmic IV curve, whereas graphite/MoS2 does not show an Ohmic IV curve at room temperature. Figure 2a shows that as the gate voltage decreases, the rectification behaviour

Fig. 2 Characteristic  $I_D$ - $V_{bias}$  curve for various  $V_{BG}$  and its band diagram. a Characteristic  $I_D$ - $V_{bias}$  curve in the range of  $V_{BG} = -10$  to +60 V. As  $V_{BG}$  decreases, change from non-diode to diode behaviour is observed. **b** Band diagram when  $V_{BG} < 0$  (diode regime). Owing to the larger work function of graphite than that of graphene, the device becomes a graphite/MoS<sub>2</sub>-interface Schottky barrier-dominant Schottky diode. **c** Band diagram when  $V_{BG} > 0$  (non-diode regime). As  $V_{BG}$  increases, the work function of graphite decreases, and the Schottky barrier height of the graphite/MoS<sub>2</sub> interface decreases.

becomes dominant at negative gate voltages. As the back-gate voltage exceeds  $V_{BG} > 0$ , non-diode  $I_D$ - $V_{bias}$  characteristic curves appear.

To clarify the origin of the gate-dependent modulation of the  $I_D$ - $V_{bias}$  characteristic curves, we measured the modulation of the Schottky barrier height with back-gate voltages from the activation energy in the reverse bias regime. The Schottky diode equation (Eq. 1) can be rewritten as

$$I_D = AA^* T^{\alpha} e^{-q\Phi_B/k_B T} \left( 1 - e^{\frac{qV_{bias}}{\eta k_B T}} \right), \tag{2}$$

where A is the area of the Schottky junction,  $A^*$  is the Richardson constant,  $\alpha=3/2$  is an exponent for a two-dimensional semiconducting system<sup>30</sup>,  $k_{\rm B}$  is the Boltzmann constant, q is the elementary charge, T is the temperature and  $\Phi_{\rm B}$  is the Schottky barrier height. When a large negative bias in absolute value is applied, i.e.  $e^{qV_{\rm bias}/k_{\rm B}T}\approx$ 0, the saturated drain current is proportional to  $T^{3/2}e^{-q\Phi_{\rm B}/k_{\rm B}T}$ . The inset of Supplementary Fig. 11a shows a plot of  $\ln(I_{\rm sat}/T^{3/2})$  versus  $1/k_{\rm B}T$  in the reverse bias saturation regime ( $V_{\rm bias}=+1$  V). We extract  $\Phi_{\rm B}$  for a given  $V_{\rm BG}$  from the slope of each curve. Supplementary Fig. 11a shows the Schottky barrier height obtained from the slope of each curve in the inset of Supplementary Fig. 11a. As shown in Supplementary Fig. 11b, in the highly positive  $V_{\rm BG}$  regime, the device shows an almost linear  $I_{\rm D}$ - $V_{\rm bias}$  curve, exhibiting nearly Ohmic contact behaviour (negligible Schottky barriers on both sides of the contacts, graphene and graphite with MoS<sub>2</sub>).

Dirac-source field-effect transistor measurement. To prove that the proposed diode is operated via cold carrier injection from a graphene DS at negative back-gate voltages, we measured the SS to determine if it showed sub-thermionic values. Supplementary Fig. 12b shows the characteristic  $I_{\rm D}$  versus control-gate voltage ( $V_{\rm CG}$ ) transfer curve under the working conditions of the DS-FET, i.e.  $V_{\rm BG} < 0$  V, where the graphene is p-type. When we apply  $V_{\rm BG} = -3$  V, graphene slightly p-type. When the control-gate is placed on the MoS $_2$  channel and the graphene/MoS $_2$  overlapped region is swept from the off-state to the on-state, the DOS of the graphene increases according to the band diagram presented in Supplementary Fig. 12a, thereby operating as a DS-FET. As shown in Supplementary Fig. 12b, the SS $_{\rm ave\_1dec}$  and SS $_{\rm ave\_3dec}$  exhibits

53.6 and 58.75 mV/dec, respectively, which indicates that the proposed diode acts as a DS-FET owing to the linear energy dispersion relationship of the graphene-source electrode, resulting in a super-exponential change in the DOS. Both DS-FET and DS diode have the same origin for SS < 60 mV/dec and  $\eta$  < 1.

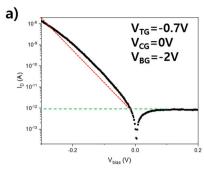

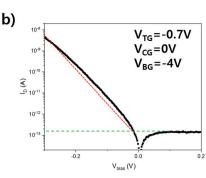

Steep-slope diode curves in the p-doped graphene region. Figure 3 shows the  $I_D$ - $V_{bias}$  characteristic curve in the steep-slope diode regime at  $V_{BG} = -6$  to -2 V in 2 V step with fixed top- and control- gate voltages ( $V_{TG} = -0.7 \text{ V}$  and  $V_{CG} = 0 \text{ V}$ ), where the graphene is p-doped. In the measured regime, where the top of the Schottky barrier is located below the Dirac point of graphene, η of the device is less than 1 in more than four decades of current owing to the cold charge injection from the DS at a forward bias  $(V_{bias} < 0)$ . The minimum  $\eta$  that we measured in one decade of current is 0.78. The red dotted line in Fig. 3 is an ideal diode curve  $(\eta = 1)$  in the forward bias direction. The DS diodes in these gate voltage regions show rectification ratios exceeding 108 at  $V_{BG} = -6 \text{ V}$  (>106 when  $V_{BG} = -2 \text{ V}$  and >107 when  $V_{BG} = -4 \text{ V}$ ). We note that the device leakage current level is limited by the leakage currents (~10 fA) from the measurement equipment. Therefore, the reverse bias leakage current level from the diode should be lower than the measured values.

# **Discussion**

In conclusion, we successfully demonstrated the DS diode that operates based on cold charge injection from a graphene source owing to the linear DOS and a Schottky barrier at the interface between graphite and monolayer MoS<sub>2</sub>. As the linear DOS of the injected charges from p-type graphene over the top of the Schottky barrier between graphite and n-type monolayer MoS2 increases linearly from reverse to forward bias, an ideal factor below 1 is obtained in the diode with a graphene electrode as the injection source. Using gate modulation of the Schottky barrier height of the graphite/MoS<sub>2</sub> junction, gradual switching between the diode and non-diode behaviours was also observed. The fabricated DS diode presents a minimum η as low as 0.78 in one decade of current, and it remains less than 1 for more than four decades of current at room temperature ( $\eta_{ave\_4dec}$  < 1), with a high rectifying ratio exceeding 10<sup>8</sup>. Additionally, the device shows SS < 60 mV/dec for the same origin as that for  $\eta$  < 1. By using CVD-grown MoS<sub>2</sub>, graphene and graphite,

Fig. 3 Slopes of DS Schottky diode versus ideal diode and recorded ideality factor in 2D vdW material-based diode. Comparison of slopes between the DS Schottky diode and an ideal diode, Black and red dotted data represent those of the DS Schottky diode and an ideal diode, respectively. The Green dashed line indicates off-state current in the reverse bias regime. a DS Schottky diode curve at  $V_{BG} = -2$  V. b DS Schottky diode curve at  $V_{BG} = -4$  V. c DS Schottky diode curve at  $V_{BG} = -6$  V. The DS Schottky diode exhibits a  $\eta_{ave\_3dec}$  of 0.98, 0.95, 0.94 when  $V_{BG} = -2$ , -4, and -6 V, respectively with fixed top- and control- gate voltage of  $V_{TG} = -0.7$  V and  $V_{CG} = 0$  V.

integrated circuits using steep-slope DS-FETs and DS diodes can be fabricated in a large scale and pave the way for energy-efficient circuit technology.

# Methods

Device fabrication. Supplementary Fig. 2 illustrates the fabrication of the Diracsource (DS) Schottky diode. As can be seen, the first step involves the preparation of a polydimethylsiloxane (PDMS) stamp covered with a polycarbonate (PC) film on a glass slide. Subsequently, MoS2 flakes are mechanically exfoliated on a Si/SiO2 wafer. In this study, the MoS<sub>2</sub> exfoliation was performed in an Ar-filled glovebox to prevent contamination. Using the standard dry-transfer method, each flake is picked up in the order—top hexagonal boron nitride (hBN), graphite, graphene, MoS<sub>2</sub>, and bottom hBN. After fabrication of the PC film and confirming sufficient adherence of the prepared flakes, the wafer was slowly heated to 90 °C, during which time, the sliding glass is slowly raised. During the pick-up process, owing to the large area of the top hBN, graphene, graphite, and MoS2 do not directly touch the PC film. After fabrication of the heterostructure on the PC film, the latter is slowly placed onto a prepared 285-nm-thick Si/SiO2 wafer. Subsequently, the wafer is heated to 180 °C, thereby melting the PC film. Thereafter, the PC film is successively washed using chloroform, acetone, and isopropyl alcohol (IPA). After transfer of the heterojunction to a new wafer, the device is exposed to chemicals to erase the released PC film. However, graphene, graphite, and MoS2 layers are encapsulated within large areas of the top and bottom hBN layers, which the chemicals cannot percolate. After fabricating the heterostructure on a 285-nm Si/ SiO<sub>2</sub> wafer, the standard e-beam lithography and plasma etching procedures are performed via e-beam deposition (Cr/Au = 5/60 nm) to place electrical contacts in the graphene and graphite layers. One-dimensional edge contact on graphene was formed in this process<sup>31</sup>. The hBN and graphite layers are etched using CF<sub>4</sub>/O<sub>2</sub> and Ar/O2, respectively. Additional e-beam lithography and deposition processes are performed to facilitate top- and control-gate placement.

**Measurement.** Supplementary Fig. 13 depicts the measurement protocol of the DS diode. Using the Keithley 6430, bias voltage was applied to the graphene electrode and measured the drain current from the graphite electrode. Keithley 2400 was used to apply a gate voltage to the Si back-gate electrode ( $V_{BG}$ ) and two Yokogawa 7651 were used to apply gate voltages to the top- and control-gate electrodes ( $V_{TG}$  and  $V_{CG}$ , respectively). Measurements were performed in a vacuum probe station with tri-axial cables to reduce leakage current from the measurement setup.

#### Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request. Source data are provided with this paper.

Received: 22 October 2021; Accepted: 5 July 2022; Published online: 26 July 2022

#### References

Mack, C. A. Fifty years of Moore's law. IEEE Trans. Semicond. Manuf. 24, 202–207 (2011).

- Szkopek, T. et al. Suspended graphene electromechanical switches for energy efficient electronics. Prog. Quantum Electron. 76, 100315 (2021).

- Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

- Fiori, G. et al. Electronic based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

- Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

- Kim, S. et al. Thickness-controlled black phosphorus tunnel field-effect transistor for low power switches. Nat. Nanotechnol. 15, 203–206 (2020).

- Kim, S. et al. Monolayer hexagonal boron nitride tunnel barrier contact for high performance heterojunction tunnel field-effect transistors. *Nano Lett.* 20, 3963–3969 (2020).

- Vandenberghe, W. G. et al. Figure of merit for and identification of sub-60mV/decade devices. Appl. Phys. Lett. 102, 013510 (2013).

- Ionescu, A. M. et al. Tunnel field-effect transistors as energy-efficient electronic switches. *Nature* 479, 329–337 (2011).

- Wang, X. et al. Van der Waals negative capacitance transistors. *Nat. Commun.* 10, 3037 (2019).

- Qiu, C. et al. Dirac-source field-effect transistors as energy-efficient, highperformance electronic switches. Science 361, 387–392 (2018).

- Xiao, M. et al. n-type Dirac-source field-effect transistors based on a graphene/ carbon nanotube heterojunction. Adv. Electron. Mater. 6, 2000258 (2020).

- Tang, Z. et al. A steep-slope MoS<sub>2</sub>/graphene Dirac-source field-effect transistor with a large drive current. Nano Lett. 21, 1758–1764 (2021).

- Liu, M. et al. Two-dimensional cold electron transport for steep-slope transistors. ACS Nano 15, 5762–5772 (2021).

- 15. Wallace, P. R. The band theory of graphite. *Phys. Rev.* **71**, 622–634 (1947).

- Di Bartolomeo, A. Graphene Schottky diodes: an experimental review of the rectifying graphene/semiconductor heterojunction. Phys. Rep. 606, 1 (2016).

- Radisavljevic, B. et al. Single-layer MoS<sub>2</sub> transistors. Nat. Nanotechnol. 6, 147–150 (2011).

- Liu, Y. et al. Approaching the Schottky-Mott limit in van der Waals metalsemiconductor junctions. Nature 557, 696–700 (2018).

- LaGasse, S. W. et al. Gate-tunable graphene-WSe<sub>2</sub> heterojunctions at the Schottky-Mott limit. Adv. Mater. 31, 1901392 (2019).

- Chiquito, A. J. et al. Back-to-back Schottky diodes: the generalization of the diode theory in analysis and extraction of electrical parameters of nanodevices. J. Phys. Condens. Matter 24, 225303 (2012).

- Jaiswal, H. N. et al. Diode-like selective enhancement of carrier transport through a metal-semiconductor interface decorated by monolayer boron nitride. Adv. Mater. 32, 2002716 (2020).

- Wang, Z. et al. Extraction and analysis of the characteristic parameters in back-to-back connected asymmetric Schottky diode. *Phys. Status Solidi A* 217, 1901018 (2020).

- Rut'kov, E. V., Afanas'eva, E. Y. & Gall, N. R. Graphene and graphite work function depending on layer number on Re. *Diam. Relat. Mater.* 101, 107576 (2020).

- Yan, R. et al. Determination of graphene work function and grapheneinsulator-semiconductor band alignment by internal photoemission spectroscopy. Appl. Phys. Lett. 101, 022105 (2012).

- Yu, Y. J. et al. Tuning the graphene work function by electric field effect. Nano Lett. 9, 3430–3434 (2009).

- Kang, J., Tongay, S., Zhou, J., Li, J. B. & Wu, J. Q. Band offsets and heterostructures of two-dimensional semiconductors. *Appl. Phys. Lett.* 102, 012111 (2013).

- Liang, Y., Huang, S., Soklaski, R. & Yang, L. Quasiparticle band-edge energy and band offsets of monolayer of molybdenum and tungsten chalcogenides. *Appl. Phys. Lett.* 103, 042106 (2013).

- Hughes, H. P. & Starnberg, H. I. Electron Spectroscopies Applied to Low-Dimensional Materials (Springer, 2000).

- Gong, C. et al. Band alignment of two-dimensional transition metal dichalcogenides: application in tunnel field effect transistors. *Appl. Phys. Lett.* 103, 053513 (2013).

- Chen, J. R. et al. Control of Schottky barriers in single layer MoS<sub>2</sub> transistors with ferromagnetic contacts. Nano Lett. 13, 3106–3110 (2013).

- Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

#### Acknowledgements

We thank J. Lee for the helpful discussions. S.C. acknowledges support from Korea NRF (Grant Nos. 2020M3F3A2A01081899, and 2020R1A2C2100258). F.L. acknowledges support from NSFC (Grant No. 61974003) and the 111 Project (Grant No. B18001). M.S.F. acknowledge support from the ARC (CE17010039).

# **Author contributions**

S.C. conceived and supervised the project. G.M., W.S. and K.S. fabricated devices and performed measurements. K.W., and T.T. grew high-quality hBN single crystals. S.K., J.P., K.S., H.L., B.K., T.J., and T.L. assisted high-temperature transport measurements. F.L. developed the theoretical model and performed device simulations. S.C., G.M., W.S., M.S.F., and F.L. analyzed the data. S.C., and G.M. wrote the manuscript. All the authors contribute to editing the manuscript.

#### **Competing interests**

The authors declare no competing interests.

# **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-022-31849-5.

Correspondence and requests for materials should be addressed to Fei Liu or Sungjae Cho

**Peer review information** *Nature Communications* thanks Xinran Wang and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Reprints and permission information is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2022