MDPI

Review

# Development of GaN HEMTs Fabricated on Silicon, Silicon-on-Insulator, and Engineered Substrates and the Heterogeneous Integration

Lung-Hsing Hsu <sup>1,2</sup>, Yung-Yu Lai <sup>3</sup>, Po-Tsung Tu <sup>1,2</sup>, Catherine Langpoklakpam <sup>1</sup>, Ya-Ting Chang <sup>1</sup>, Yu-Wen Huang <sup>1</sup>, Wen-Chung Lee <sup>1,2</sup>, An-Jye Tzou <sup>4</sup>, Yuh-Jen Cheng <sup>3</sup>, Chun-Hsiung Lin <sup>5,\*</sup>, Hao-Chung Kuo <sup>1,6,\*</sup> and Edward Yi Chang <sup>5</sup>

- Department of Photonics and Institute of Electro-Optical Engineering, College of Electrical and Computer Engineering, National Chiao Tung University, Hsinchu 30010, Taiwan; alger.99g@g2.nctu.edu.tw (L.-H.H.); itriA30378@itri.org.tw (P.-T.T.); cath01.ee09@nycu.edu.tw (C.L.); s922085493@gmail.com (Y.-T.C.); huangwendy227@gmail.com (Y.-W.H.); vincent.lee67@gmail.com (W.-C.L.)

- Industrial Technology Research Institute, Hsinchu 31040, Taiwan

- Research Center for Applied Sciences, Academia Sinica, Taipei 114699, Taiwan; loveriver031@gmail.com (Y.-Y.L.); yjcheng@sinica.edu.tw (Y.-J.C.)

- <sup>4</sup> Taiwan Semiconductor Research Institute, Hsinchu 30078, Taiwan; jerrytzou.ep00g@gmail.com

- International College of Semiconductor Technology, National Yang Ming Chiao Tung University, Hsinchu 30010, Taiwan; edc@mail.nctu.edu.tw

- <sup>6</sup> Semiconductor Research Center, Hon Hai Research Institute, Taipei 114699, Taiwan

- \* Correspondence: chun\_lin@nctu.edu.tw (C.-H.L.); hckuo@faculty.nctu.edu.tw (H.-C.K.); Tel.: +886-3-571-2121 (ext. 31986) (H.-C.K.)

**Abstract:** GaN HEMT has attracted a lot of attention in recent years owing to its wide applications from the high-frequency power amplifier to the high voltage devices used in power electronic systems. Development of GaN HEMT on Si-based substrate is currently the main focus of the industry to reduce the cost as well as to integrate GaN with Si-based components. However, the direct growth of GaN on Si has the challenge of high defect density that compromises the performance, reliability, and yield. Defects are typically nucleated at the GaN/Si heterointerface due to both lattice and thermal mismatches between GaN and Si. In this article, we will review the current status of GaN on Si in terms of epitaxy and device performances in high frequency and high-power applications. Recently, different substrate structures including silicon-on-insulator (SOI) and engineered poly-AlN (QST®) are introduced to enhance the epitaxy quality by reducing the mismatches. We will discuss the development and potential benefit of these novel substrates. Moreover, SOI may provide a path to enable the integration of GaN with Si CMOS. Finally, the recent development of 3D hetero-integration technology to combine GaN technology and CMOS is also illustrated.

Keywords: gallium nitride; high-electron mobility transistor; heterogeneous integration; SOI; QST

Citation: Hsu, L.-H.; Lai, Y.-Y.; Tu, P.-T.; Langpoklakpam, C.; Chang, Y.-T.; Huang, Y.-W.; Lee, W.-C.; Tzou, A.-J.; Cheng, Y.-J.; Lin, C.-H.; et al. Development of GaN HEMTs Fabricated on Silicon, Silicon-on-Insulator, and Engineered Substrates and the Heterogeneous Integration. *Micromachines* 2021, 12, 1159. https://doi.org/10.3390/mi12101159

Academic Editor: Giovanni Verzellesi

Received: 3 August 2021 Accepted: 11 September 2021 Published: 27 September 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

1.1. History and Applications of GaN HEMT

In the past decades, the wide bandgap GaN semiconductor materials and its alloys (AlGaN and InGaN) are emerging as one of the most promising materials for a variety of applications. Due to its robust thermal stability and electronic properties such as radiative hardness, it is an ideal candidate for working in a harsh and aggressive environment [1,2]. The development of AlGaN/GaN high electron mobility transistors (HEMT) is mainly due to both military and commercial interests in high-temperature, high-frequency, and high-power device applications [2–4]. AlGaN/GaN HEMT has been extensively developed for radio frequency (RF) high power amplifiers with high output power and high efficiency [3,5–7]. GaN's high breakdown electric field (~3.3 MV/cm) and high mobility

*Micromachines* **2021**, *12*, *1159*

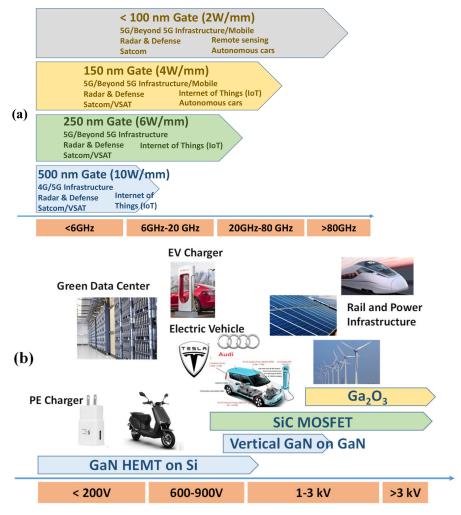

(>900 cm² Vs) [8] makes GaN-based devices attractive to work in very high powers and microwave frequencies since it can handle high current (~ 10 A) and high voltage (~ 100 V) with high transit speed [9,10]. The first GaN RF device product was presented in 2005 [11] but the insertion of the technology was limited in the military and some high-end RF infra-structure applications due to high cost. Later on, the first commercial product of GaN HEMT for power electronic application was presented in 2009 [12]. Owing to its superior performance and manufacturability on Si, GaN HEMT enters the stage of rapid growth. More recently, GaN HEMT has been rapidly developed for high-performance RF power amplifiers (PAs), such as mmW PA for 5G and beyond applications, owing to the requirement of wide-bandwidth and data rate for future mobile communication systems [13]. The roadmap in GaN HEMTs applications is illustrated in Figure 1.

**Figure 1.** (a) A roadmap of RF GaN HEMTs technology. (b) A roadmap of Power GaN HEMTs technology.

#### 1.2. The Influence of Different Substrates on GaN HEMT Device

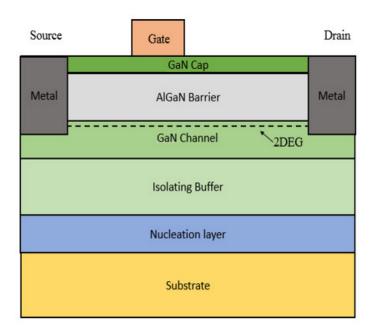

In the earlier stage of its development, the progress of GaN/AlGaN HEMT was focused on improving the quality of epitaxial material for RF applications, the major efforts include the selection of the best substrate as well as developing unique processes [14]. GaN HEMTs can be grown on different substrates, including sapphire, silicon (Si) silicon carbide (SiC), or diamond due to the lack of GaN bulk substrate [15,16]. The basic structure of GaN HEMT is shown in Figure 2. For RF GaN HEMT, it was expected to provide a very high output RF power for a single die up to several hundred watts over a wide frequency range [17,18]. The high-power density requires efficient power dissi-

Micromachines **2021**, 12, 1159 3 of 32

pation on transistors as well as on substrate [19], thus, the performance and reliability of the high-power RF transistor can be seriously affected by the thermal conductivity of the substrate. The thermal properties of the different substrates are shown in Table 1. By using a substrate with high thermal conductivity, like SiC, the high heat generated can be effectively dissipated. AlGaN/GaN HEMTs on SiC substrates with very high RF output power densities of about 40 W/mm have been reported [20]. However, the full advantages of GaN on the high thermal conductivity SiC cannot be obtained as the thermal performance is degraded due to the epitaxial layer defects at the interface between GaN and SiC [21], which we will discuss further in a later paragraph. Cree has been developing GaN on SiC for commercial sale since 2006 [22]. The gradual scale-up of high purity semi-insulating 4H-SiC substrates from 2-inch to 4-inch substrates has greatly enhanced the economic viability of wide band-gap microwave devices.

Figure 2. The basic structure of GaN HEMT.

In the past, SiC is mainly used as a substrate for RF GaN HEMT and demonstrated satisfactory performance. However, Si substrate is desired due to its low cost, good thermal conductivity, and availability of a large area. The growth of GaN on Si is more difficult than the growth of GaN on SiC since the growth of GaN on Si tends to result in higher dislocation density or microcracks due to higher thermal expansion coefficient and lattice mismatches [23]. With the progress of material engineering, the low cost and high performance. GaN on Si device has been achieved on a high-quality GaN layer grown on a large area Si substrate (8-inch wafer) [24]. One of the main issues of fabricating RF GaN HEMT on Si is the increased RF losses due to the parasitic conduction channel introduced at the III-nitride-Si interface and lower resistivity of Si substrates [25–28]. High resistive (HR) Si substrates are often adopted to solve the issue. However, the growth of high strain GaN on HR Si substrate shows a worse bowing problem. Moreover, the cost of HR Si is higher than that of low resistive (LR) Si substrate. These factors limit the production of the device on a larger silicon substrate. Substrate removing technique is reported to allow the fabrication of GaN HEMT on LR Si substrate with minimized substrate parasitic to improve RF/MW characteristic [29]. Though high-performance RF GaN HEMT on Si is still in development, GaN HEMT on Si has become the mainstream for power electronics applications. Currently, the power GaN HEMT with breakdown voltage higher than 1200 V has been demonstrated. In the later paragraphs, we will discuss and review the status of GaN on Si devices for both RF and power applications in details.

Micromachines **2021**, 12, 1159 4 of 32

Among all the potential substrate materials, single-crystal diamond shows the highest thermal conductivity [30]. A high cut-off frequency (85 GHz) of GaN HEMT on the diamond was fabricated using wafer bonding between GaN HEMT structure grown on Si wafer and polycrystalline diamond wafer [31,32]. AlGaN/GaN HEMT structure grown by molecular beam epitaxy (MBE) on diamond (111) was reported with RF small-signal characteristic [31,32]. A single-crystal AlN and AlGaN/GaN HEMT were grown on a diamond substrate by using (111) surface orientation with metal-organic vapor phase epitaxy (MOVPE) [15,33,34]. AlGaN/GaN HEMTs grown on diamond (111) substrate for RF power operation with an output density of 2.13 W/mm were achieved [31]. Although the device performance for GaN on diamond looks promising, the lack of a large diamond substrate limits the development of the technology. Commercially available sapphire is also one of the most prominent substrates for the epitaxy of GaN due to the limited native GaN availability [35]. However, the use of sapphire is limited as the stability of the GaN on sapphire is less than that of GaN on Si due to weaker scattering phenomena which is related to its thermal conductivity at high drain bias [36].

Along with the thermal conductivity of the substrate, Thermal Boundary Resistance (TBR) is an important parameter to affect the overall rise in temperature of a device [37]. The thermal effects of the device are boosted by TBR which is resulted from the interface for the growth of dissimilar materials. TBR is a measure of the resistance imposed by the interface to heat flow due to the different dynamics of the phonons and the poor quality of the crystal near the boundary. It is defined as the maximum temperature increase by the maximum power dissipation of the device. The TBR in commercial GaN HEMTs on SiC can reach levels greater than  $6 \times 10^{-4}$  cm<sup>2</sup>K/W which can increase the maximum temperature of the device by up to 40–50% [38,39]. The increase in TBR causes an offset to the advantages offered by the substrate with high thermal conductivity due to the discontinuity of the temperature gradient in TBR layers located at the GaN substrate interface [40]. Thermal conductivity for GaN and different substrate materials at 300 K and TBR values of GaN/ substrate interface simulated in [41] are listed in Table 1. The lower TBR values of GaN on Si substrate than that of SiC substrate is mainly due to the different thermal expansion coefficient [42], the roughness of the substrate materials as well as the defect related to the growth techniques. The high value of TBR at the interface of high thermal conductivity substrate and GaN could be reduced and has additional advantage if it has a better thermal coupling and fewer interface defects while low thermal conductivity like sapphire has a less significant influence of TBR on transporting heat [43].

**Table 1.** Temperature-dependent thermal conductivity of GaN/different substrate materials, TBR values for GaN/substrate interfaces used in simulations are listed [41,44].

| Material | Thermal<br>Conductivity<br>κ (W/m-K) | TBR (m <sup>2</sup> K/GW) | Thermal<br>Expansion<br>Coefficient,<br>(10 <sup>-6</sup> /K) | Lattice<br>Mismatch with<br>GaN (%) |  |

|----------|--------------------------------------|---------------------------|---------------------------------------------------------------|-------------------------------------|--|

| GaN      | 160 (300/T) <sup>1.4</sup>           | _                         | _                                                             | _                                   |  |

| Sapphire | $35 (300/T)^1$                       | 10–40                     | 39                                                            | 16                                  |  |

| Si       | 150 (300/T) <sup>1.3</sup>           | 10–40                     | 54                                                            | 17                                  |  |

| SiC      | 420 (300/T) <sup>1.3</sup>           | 30–60                     | 3.2                                                           | 4                                   |  |

| Diamond  | 1200 (300/T) <sup>1</sup>            | 20–50                     | 62.5                                                          | 12                                  |  |

# 1.3. Evolution of GaN HEMT

### 1.3.1. Different Gate Structure Designs

The HEMT structure was based on T. Minura et al. (1975) [45] and M.A. khan et al. (1994) [5]. At the interface of AlGaN and GaN, there exists 2-dimensional electron gas (2DEG) with high electron mobility owing to the difference in spontaneous polarization

*Micromachines* **2021**, *12*, *1159* 5 of 32

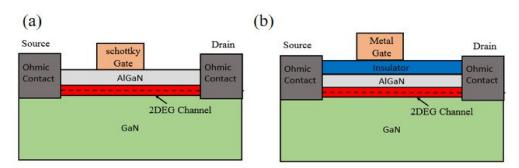

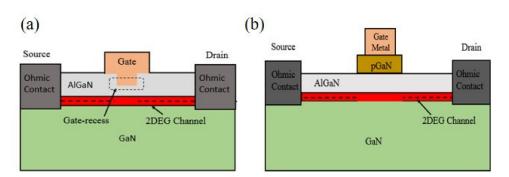

and piezoelectric polarization [46]. Hence the device operates as a normally-on device naturally. To deplete the 2DEG channel, a gate electrode on top of the AlGaN layer has a negative gate voltage concerning drain and source electrode applied. This type of device is known as depletion-mode (D-mode) HEMT. Moreover, there are two types of D-mode HEMT, namely with a Schottky gate electrode or with an insulating gate [47]. The first d-mode HEMT introduced had a Schottky gate electrode in which the metal gate electrode is directly deposited on top of AlGaN. Ni–Au or Pt metals were used to form the Schottky barrier [23,48,49]. In insulate gated d-mode HEMT, an insulating layer is placed in between the gate electrode and AlGaN similar to that of MOSFET to block the gate current [50]. Schottky gate and insulated gate d-mode HEMTs are shown in Figure 3.

Figure 3. (a) Schottky gate D-mode HEMT (b) Insulated gate D-mode HEMT.

D-mode HEMT is not preferred in system applications as it requires a negative bias to be applied. On the other hand, there is also a concern in fail-safe operation. Therefore, Enhancement-mode (E-mode, normally-off) device is favored and has become one of current focuses of technology development. To create e-mode devices, there are five popular structures: recessed gate, implanted gate, pGaN gate, direct-drive hybrid, and cascode hybrid [47]. For GaN HEMT in RF applications, the most common fabrication technique used for modifying the threshold voltage is "gate-recess". This process reduces the barrier thickness under the gate metal. The basic structure of gate recess HEMT is shown in Figure 4a.

Figure 4. (a) Basic structure of Gate-recess HEMT. (b) Schematic structure of p-GaN Gate HEMT.

There are also approaches to obtain E-mode devices by heterostructure or gate stack designs. Ohmaki et al. proposed a double-barrier-layer AlGaN/GaN HFET in 2006. The use of double-barrier-layer sustains the device at a BV of 435 V, Ron,sp of 1.9 m $\Omega$  cm $^2$ , with a threshold voltage of -0.1 V [51]. Inter University Microelectronics Centre (IMEC) presented another E-mode AlN/GaN/AlGaN HFET structure in 2010 with a double heterostructure-barrier layer. The double structure comprises of a high concentration 2DEG at the surface of the hetero structure and an ultrathin AlN barrier layer grown on silicon substrate; and the structure maintains a BV of 580 V, with an Ron,sp of 1.25 m $\Omega$  cm $^2$ , and a threshold voltage of about 0 V [52]. Mizutani et al. in 2007, proposed an E-mode AlGaN/GaN HFET with a thin InGaN cap layer. The proposed structure shifts the threshold voltage towards

*Micromachines* **2021**, *12*, *1159* 6 of 32

the positive direction by rising the conduction band of the AlGaN/GaN via the use of a polarization-induced field in the InGaN cap layer [53]. Ostermaier et al. in 2009, proposed an ultrathin InAIN/AIN barrier HEMT that have high performance under normally off operation. They selectively etched the n++ GaN cap layer structure, which in-turn controls the width of the ultrathin barrier layer [54]. The proposed structure operates with a threshold voltage of 0.7 V, a maximum transconductance of 400 mS/mm and a maximum output current of 800 mA/mm. Hughes Research Laboratories, in collaboration with the Next Generation of Nitrides Electronics Project from the US Defense Advanced Research Projects Agency (DARPA), proposed an E-mode HFET with a double-barrier layer via selective-area molecular beam epitaxy (MBE) [55]. For the integrated E-mode and D-mode AlN/GaN/AlGaN double-heterojunction field-effect transistors (DHFETs) on a single SiC substrate, an E-mode channel was achieved without additional procedures or compromise in the electrical characteristics. The idea of developing a monolithic integrated E-mode and D-mode device can be the groundwork for direct-coupled field-effect transistor (FET) logic circuits. Guowang Li et al. proposed an E-mode AlGaN/AlN/GaN HFET having 70% Al composition comprising of a thick AlGaN layer (17 nm), an AlN layer (0.6 nm) and an Al<sub>2</sub>O<sub>3</sub> (4 nm) layer. They used Ni/Au in the Schottky gate metal instead of Al/Au thereby enhancing the threshold voltage from -1.0 V to -0.13 V [56]. Chiu et al. proposed an E-mode HFET comprising of a composite dielectric layer via N<sub>2</sub>O plasma oxidation technology. The composite dielectric layer (Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub>) after the oxidation in the N<sub>2</sub>O for the AlGaN barrier layer improves the threshold voltage from −3.6 V to 0.17 V [57]. Based on this structure, Chiu et al. presented an E-mode HFET with a high-k composite dielectric layer in 2012. The AlGaN barrier layer was oxidized by nitric oxide (NO) gas prior to the Schottky metal gate deposition. After the oxidized AlGaN barrier layer stack  $(Al_2O_3/Ga_2O_3)$  is formed, a dielectric film of gadolinium oxide  $(Gd_2O_3)$  was deposited to complete the structure thereby, enhancing the threshold voltage from -3.15 V to 0.6 V [58]. Massachusetts Institute of Technology in collaboration with Harvard university presented one E-mode HFET with a scandium oxide (Sc<sub>2</sub>O<sub>3</sub>) high-k dielectric. In the study, Wang et al. introduced a Sc<sub>2</sub>O<sub>3</sub> high k-dielectric layer in the HFET to reduce the invert leakage current thereby having the switch-current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) reach 10s [59].

By reducing AlGaN barrier thickness, it can result in a reduction of polarization induced 2DEG and the threshold voltage is shifted positively with the help of the workfunction of the metal gate. A positive threshold voltage can be achieved with a deep enough gate recess etching thus forming an E-mode HEMT [60]. A chloride-based dry inductively coupled plasma reactive ion etching (ICP-RIE) for gate recess etching has been employed by several groups [61-66] which can effectively change the threshold voltage to the positive direction of AlGaN/GaN HEMT. Damage in the subsurface was also reported from ICP dry etching due to low etch selectivity between materials which increases the gate-leakage current [67]. The damages were found to be repaired after post-etching rapid thermal annealing (RTA) at 700 °C [65,66]. For the RF HEMT structure, recessed gate enhances the device performance by providing a better gate control capability of the channel carriers. On the other hand, due to the repaired damage with proper recessed gate process, flicker noise characteristics were reduced, which is beneficial for RF circuit applications such as voltage-controlled oscillators (VCOs) and mixers [68,69]. On the other hand, p-GaN gate technology is more popular for the fabricator of e-mode power GaN HEMT device. The schematic structure of p-GaN gate HEMT is shown in Figure 4b. The conduction band of the AlGaN is risen above the Fermi level when compared with a standard Schottky gate normally-on HEMT due to the presence of p-GaN cap and results in the depletion of the 2DEG channel. Uemoto et al. first proposed a p-AlGaN gate normally-off HEMT [70]. The thickness of the AlGaN barrier as well as Al-concentration needs to be defined appropriately to achieve an efficient depletion region in the channel [71–74]. A high doping concentration of Mg, a p-type dopant,  $(>10^{18} \text{ cm}^{-3})$  is necessary for the efficient depletion at the interface of the metal gate/pgate [75]. However, the hole concentration can be reduced at a high temperature above

Micromachines **2021**, 12, 1159 7 of 32

500 °C due to the formation of Mg-H complexes [76]. Hence, proper care is necessary during device processing like annealing of Ohmic contacts so that Mg concentration does not reduce. Another important feature is the choice of the metal gate as the threshold voltage of the device depends on metal/p-GaN Schottky barrier height. In this aspect, much researches have been done on metal gate work-function influence on p-GaN electrical behavior [77–80]. Schottky metal gates have shown improvement in lowering the leakage and increasing the threshold voltage than Ohmic gate [77,78]. Presently, the TiN gate is one of the good solutions due to its thermal and chemical stability along with the processing compatibility [81–84]. A p-GaN gate HEMT with a "self-aligned" process using Mo-based gate was demonstrated which employed "gate first" process [85]. Mo gate sustained the high-temperature annealing process of source-drain ohmic contact without the barrier degradation. Although p-GaN gate HEMT has reached commercialization, their reliability issues [80] need intensive researches.

#### 1.3.2. N Polar vs. Ga Polar

Typically group III-Nitride devices are fabricated using the Ga-polar (0001) orientation. However, the inverted N-polar polarity possesses a numerous advantage over Ga-polar counterparts. The absence of inversion symmetry in wurtzite group III-Nitride results in opposite polarization of N-polar crystal and Ga-polar crystal. Hence, the polarization induced electric fields of Ga-polar heterostructures is opposite to that of N-polar counterparts which results in formation of 2DEG of N-polar heterostructures above the wide-bandgap barrier layer instead of below [86]. The advantages offered by N-polar GaN HEMTs over Ga-polar HEMTs are as follows: (i) N-polar heterostructures has a strong back-barrier due to its inherent wide-bandgap Al(Ga)N back-barrier for electron confinement which reduces the effects due to short-channel [87], (ii) N-polar HEMTs has low-resistivity Ohmic contact as the channel layer with lower surface barrier to electrons and a narrower bandgap can contact 2DEG of N-polar HEMTs rather than contacting through wide-bandgap Al(Ga)N barrier [88,89] which results in the possibility of lowering the contact resistance by using selective regrowth of ohmic area in N-polar structure, (iii) N-polar heterostructure has improved scalability. The effective gate-channel distance is reduced by the quantum displacement of the 2DEG in N-polar HEMT which is opposite to that of Ga-polar HEMTs owing to the reduction in effective gate-channel capacitance due to quantum capacitance [90]. Such enhancement results in higher N-polar transconductance than that of Ga-polar with same gate-channel thickness. The aspect ratio as well as the charge density under the gate of N-polar HEMTs can be controlled independently where the enhancement of charge depletion due to the scaling of channel thickness are compensated by increasing the thickness and the polarization of charge-inducing back barrier. Whereas, gate aspect ratio in Ga-polar HEMT depends on the barrier thickness and there is a trade-off between the charge density under the gate and the barrier thickness [91]. N-polar heterostructure does not required intentional n-type doping for the formation of 2DEG [89,92,93] due to the presence of high-density unintentional bulk and surface donors [94]. A N-polar GaN HEMTs epitaxy grown by MOCVD on 4° off-cut 2-inch diameter sapphire substrate at UCSB for X-band power performance transceiver systems was reported with 2 tone results at 10 GHz [95]. The reported HEMTs structure is similar with that of structure reported by X. Zheng et al. [96]. The reported HEMT device shows very little 3rd order distortion in intermodulation and 65% of single tone high power added efficiency (PAE) with 3 W/mm power density which can be scaled favorably with 15 V drain voltage. A deep recess W-band power N-polar GaN HEMTs utilizing a new atomic layer deposition (ALD) ruthenium (Ru) gate metallization process with PAE of 33.8% and 6.2 W/mm high power density was demonstrated [97]. The demonstrated HEMTs has an outstanding control over the DC-RF dispersion due to presence of deep recess structure in conjunction with SiN thin passivation layer and has a high gain as the narrow 48-nm gate trench was filled by ALD Ru metal.

Micromachines **2021**, 12, 1159 8 of 32

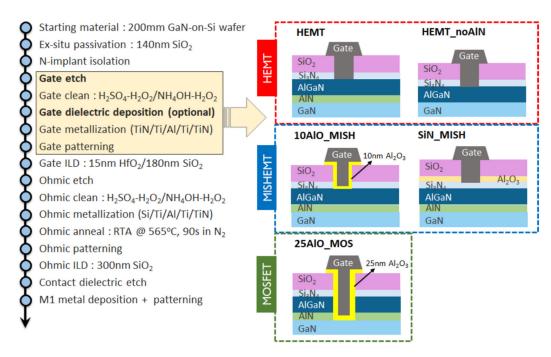

#### 1.4. CMOS Compatible Process for GaN HEMT

In wireless communication, to respond to the growing demand for high data rates, there is a push to a higher operating frequency, switching to millimeter-wave from the congested sub 6 GHz band. Beyond operational speed of power amplifiers, output power (Pout) and power added efficiency (PAE) in RF Front End Modules are critical for next-generation portable devices and small cells. As opposed to CMOS, the high-power handling capabilities of GaN are advantageous for mm-wave operations [98] as the more energy-efficient system can be achieved owing to its capability in the high output power with high efficiency at high-frequency. However, the integration of GaN HEMTs remains one of the main concerns. The current limitation of GaN RF technology is due to the use of expensive older generation Au-based processing as well as non-Si substrates [99]. Hence to make GaN devices for RF and MM-wave applications, migrating to 200 nm Si platform and using standardized CMOS fabrication tools for manufacturing the device become a crucial step to improve yield and reduce the cost. Similarly, the CMOS compatible technology can also benefit the development of GaN devices for power electronics. A CMOS-compatible 110 V/650 V e-mode GaN HEMT with excellent power converter switching performance with high robustness was fabricated on 6-inch GaN on a Si wafer [100]. Figure 5 shows an example fabrication process flow of GaN devices. GaN devices with low RF loss, low buffer dispersion as well as good leakage blocking capability have been demonstrated by integrating the device on the Si platform based on the Au-free, Si CMOS compatible process [98,101–103]. To enhance the functionality as well as the performance of the RF modules, various approaches to integrate CMOS and GaN devices have been developed [104,105].

**Figure 5.** Gate-first process flow for the fabrication of GaN devices. Five device splits were realized based on differences in gate processing [98].

# 1.5. GaN-Based CMOS Technology

A lot of demonstration has been done on power integrated circuit based on GaN [106–108] which depends on the integration of E-mode and D-mode n- type HEMTs. However, these E/D mode circuits have reduced output voltage swing and also suffers from static power dissipation. Therefore, a CMOS-like circuit technology is required to increase the efficiency of ICs based on GaN as this circuit technology has negligible static power consumption, has higher noise immunity and less circuit complexity [109].

Micromachines **2021**, 12, 1159 9 of 32

However, the challenges of the monolithic integration of the p-type GaN FETs with n-type GaN FETs along with lack of high-performance of p-type GaN FETs are the major obstacle towards achieving high efficiency GaN-based ICs. A various epitaxial structures of p-type GaN FETs have been demonstrated [110–117]. A GaN complementary inverter circuit comprising of both E-mode n-type GaN FET and p-type GaN FET monolithically integrated on Si Substrate without regrowth technology was also demonstrated [118]. The probe station with thermal chuck were used to characterize the fabricated inverter under high operation temperature. The fabricated circuit shows an outstanding transfer characteristics up to 300 °C with maximum recorded voltage gain of about 27 V/V at 0.59 V input voltage with 5 V as V<sub>DD</sub> supply. A very high density of 2D hole gas (2DHG) induced by the polarization at the interface of GaN/AlN was discovered [119] which led to the development of p-channel heterostructure field effect transistors (HFETs) that reach the linear current density of 100 mA/mm [112]. A p-channel MISFET with a recessed-gate was grown by metalorganic chemical vapor deposition (MOCVD) using p-GaN/AlGaN/GaN hetrostructure on Si substrate [113,118]. The fabricated structure contains both 2-dimensional electron gas (2DEG) and 2-dimensional hole gas (2DHG) without regrowth technology which is suitable for implementing GaN- based complementary circuit. The fabricated long channel p-type device when compared with p-FET GaN/AlGaN on sapphire substrate exhibits state of the art on-off ratio performance. A p-channel 2DHG GaN/AlN transistors which can break the barrier of GHz speed was demonstrated [120]. The fabricated transistor exhibits an on-current density of 428 mA/mm and a cut-off frequency of 20 GHz. A wide-bandgap CMOS platform formed using these fabricated p-channel HFETs along with excellent performance n-channel HFETs [121] was expected to achieve a new domain in the RF and power electronics applications [122].

In the later paragraphs, we will review in more detail the progress and performance of GaN on Si devices. Moreover, the progress in hetero-integration will also be described.

#### 2. GaN HEMT on Si

# 2.1. GaN Epitaxial Growth on Silicon

Silicon substrate is a general and commercial materials in semiconductor technology. Actually, a good epitaxy must be fine-matched in lattice and thermal expansion coefficient between GaN and heterogenous substrate, like Si, Sapphire, SiC . . . etc. The related summary in physical parameters is listed in Table 2 [123].

| Mismatch                         | Si    | SiC  | Sapphire | AlN   | GaN   |

|----------------------------------|-------|------|----------|-------|-------|

| Crystal Structure                | FCC   | HCP  | HCP      | HCP   | HCP   |

| Lattice Constant (Å)             | 5.43  | 3.08 | 4.758    | 3.112 | 3.189 |

| Lattice Mismatch (%)             | -16.9 | 3.5  | 16.08    | 2.4   | _     |

| Thermal Expansion ( $10^{-6}$ K) | 3.59  | 4.3  | 7.3      | 4.15  | 5.59  |

| Thermal Mismatch (%)             | 55    | 30   | -23      | 34    | _     |

**Table 2.** The lattice and thermal mismatch of Si, SiC, Sapphire, AlN, and GaN.

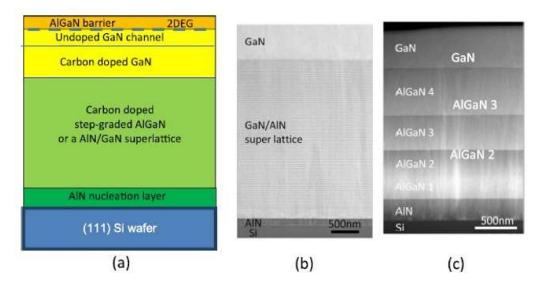

Due to the mismatch of lattice constant and thermal expansion coefficient between Si and GaN, it is more difficult to achieve high quality GaN structure growth on Si [124–126]. In general, a lot of defects exist, and the gallium nitride layer may crack when cooling process. In order to solve these problems, gallium nitride epitaxial layers with high uniformity, high quality and no cracks can be grown on silicon substrate by growing buffer layer as shown in Figure 6 [12,127]. The buffer layer can be designed in the following two ways: (1) AlN/GaN superlattice growth through the step gradient AlGaN layer [128], and (2) AlGaN/GaN superlattice [129]. The bending of the wafer will increase with the increase of the thickness. A multilayer-buffer structure reduces the tensile stress caused by the huge difference in thermal expansion coefficient between GaN and Si. It's useful for inducing compressive strain in the growth process, as to counteract tensile strain introduced in the cooling process, prevent cracking and produce a flat wafer.

Micromachines **2021**, 12, 1159

**Figure 6.** (a) Schematic cross-section of the typical epitaxial layer structure used for the manufacture of GaN-on-Si HEMTs. (b) TEM image of a GaN/AlN superlattice buffer layer and (c) a step graded AlGaN buffer layer, both on Si substrates [12].

Furthermore, the breakdown voltage in GaN HEMT is affected by the quality and resistivity of GaN-based templates. In order to operate an efficient GaN channel, it also needs higher resistivity buffer layer to prevent the DC leakage current and AC coupling. The characteristics of GaN high-frequency power amplifiers will change with the resistance of the underlying buffer layer, which is mainly due to the signal coupling effect. However, several groups have used different methods to improve the buffer layer resistivity, which employed p-type dopant (Mg) to enhance GaN buffer structure (n-type intrinsically). Another method is using Carbon dopant which plays a more attractive role in buffer layer. Compared to Mg case, the storage effect of Carbon-doped method isn't strong. According to doped buffer layer, the carrier concentrations and electrical properties (breakdown voltage) are adjusted by varied epitaxial conditions [130].

On the other hand, the top barrier layer includes AlGaN or InAlN, which results in 2DEG of HEMT through polarization charges in nitride-based materials are critical. While the thin AlGaN layer is grown on GaN channel layer, the Al content and thickness would be limited due to the lattice mismatch of GaN. The interface charge could be adjusted by varied barrier thickness and Al compositions. Compared to AlGaN, InAlN could reduce epitaxial defects as a result of thicker critical thickness. It shows that a good lattice-matched InAlN (18% In) exhibits a stronger spontaneous polarization to generate a higher channel charge density [131].

### 2.2. Power GaN Performance Si Substrate

As described in Section 1, the traditional power HEMT structure uses a Schottky metal to modulate the 2DEG in the channel. Generally, the metal stack Ni/Au is used for the HEMT. However, in order to efficiently control the gate leakage current, high-k gate dielectric layer was employed to form metal–insulator–semiconductor (MIS) gate, [132] for commercial power GaN HEMT on Si. The passivation layer provides additional protection and reduces the current loss in the surface state of devices. The breakdown voltage of GaN power components on Si in the low- and medium-power fields are predicted above 900 V, and the GaN shows very high potential in power applications due to the benefits of a low switching loss and lower cost [133].

Furthermore, the power electronics application represents one major market in the developments for GaN power devices like p-GaN HEMTs for enhancement-mode (E-mode) operation. The breakdown voltages for p-GaN HEMTs have exceeded 1000 V (Ron,sp of 2 m $\Omega$  cm<sup>2</sup>). In power switching applications, a normally-off (enhancement-

Micromachines **2021**, 12, 1159 11 of 32

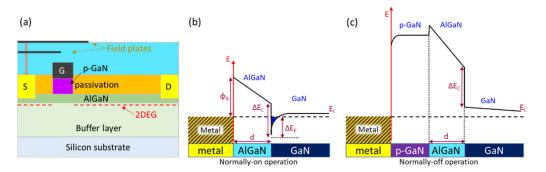

mode) GaN HEMT is desirable due to the safe-operation formation and efficient gate control to switch on/off. A variety of e-mode GaN HEMTs are fabricated by using p-GaN gate [74], gate recess [134], or plasma treatment techniques. The p-GaN gate HEMT showed a good performance, reliability, and commercialization. Figure 7 shows the band structures of normally-on AlGaN/GaN HEMTs and normally-off p-GaN/AlGaN/GaN HEMTs. The 2DEG channel is depleted at a zero-bias condition as the conduction band energy of AlGaN is lifted due to the p-GaN region. The electrical characteristics of the p-GaN gate HEMT shows  $V_{\rm TH}$ , the  $V_{\rm GS}$  limitation, and the gate leakage current (I\_GSS) depend on the structure of the gate stack by using normally on and off system [135]. In order to deplete the 2DEG channel at  $V_{\rm G}$  = 0, the general AlGaN thickness is 10~15 nm, and the thickness of the p-GaN gate is 50~100 nm. A doping Mg concentration of the p-GaN (or p-AlGaN) gate is around  $10^{18} \sim 10^{19}$  cm $^{-3}$ .

**Figure 7.** (a) Cross-sectional schematic of p-GaN gate HEMT [135] and (b) schematic of the operation principle of the normally on HEMT and (c) normally off HEMT [74].

# 2.3. RF GaN Performance Si Substrate

GaN technology that can offer high output power and efficiency at high frequencies is regarded as the most critical technology to reduce the complexity in designing upcoming mm-wave band communication system for 5G or beyond applications. In particular, GaN on Si technology that can greatly reduce production costs has attracted more attention. However, due to the challenges in obtaining higher-quality epitaxy on Si, RF GaN HEMT was fabricated primarily on SiC for high-frequency applications until 2014 when MACOM announced the mass production of 4" GaN on Si technology. Due to the continuous improvement of epitaxial technology, almost all major semiconductor foundry starts to invest heavily on the development of GaN on Si technologies.

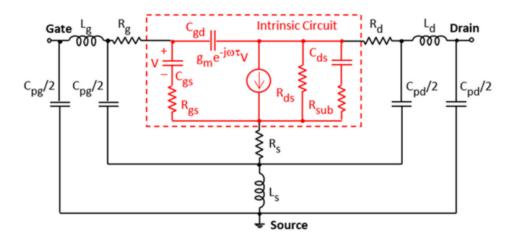

In order to develop RF GaN HEMT with superior high-frequency characteristics, we can refer to the equivalent circuit [136] shown in Figure 8, the small signal model of a GaN HEMT includes gate parasitic capacitance and resistances. According to Eq (1)(2) [137], we must decrease capacitance [138], ohmic contact resistance [139], gate resistance [140] and increase transconductance [141] in order to maximum the  $f_T$  and fmax.

$$F_{T} = \frac{g_{m}}{2\pi(C_{GS} + C_{GD})[1 + (R_{S} + R_{D})G_{DS} + g_{m} \times C_{GD}(R_{S} + R_{D})]} \tag{1}$$

$$F_{MAX} = \frac{F_T}{2\sqrt{(R_i + R_S + R_G) \times G_{DS} + 2\pi F_T R_G C_{GD}}}$$

(2)

Micromachines **2021**, *12*, 1159

Figure 8. Small-signal equivalent circuit for the tested MOSFETs.

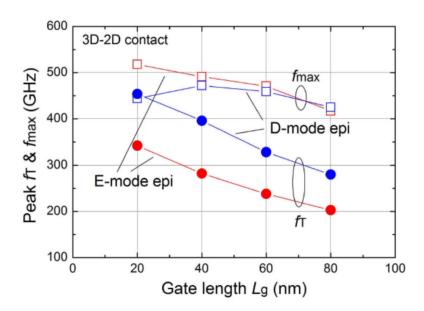

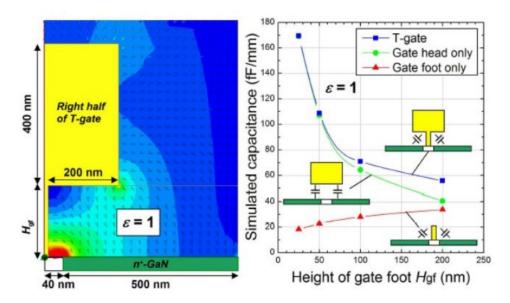

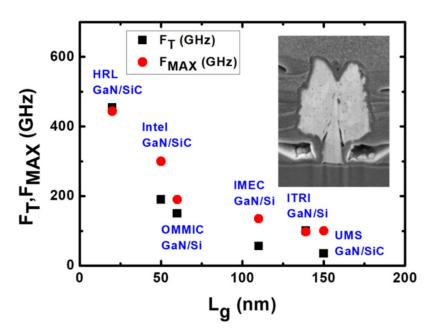

To operate at high frequency, the gate length must be minimum to reduce gate capacitance, as shown in Figure 9. But, the parasitic resistance will be increased and degrade the high frequency performance [142], the T-shaped gate becomes a key element to reduce the gate parasitic resistance. The height and width of the T-shaped gate should be optimized for both capacitance and resistance values. Keisuke Shinohara et al. [142] demonstrated the most suitable T-gate shape through simulation based on gate capacitance as show in Figures 10 and 11. Benchmark of cut-off frequency versus  $L_G$  [143–148] illustrates the importance of gate length shrinking to increase  $f_T$ . Both NTU [149] and Intel [143] demonstrated 40 nm gate length GaN HEMT on Si with  $f_T$ /fmax higher than 300 GHz, though the current record  $f_T$ /fmax values of 450 GHz was achieved by HRL [144] with the 20 nm Gate GaN on SiC technology.

**Figure 9.**  $F_T$  and  $F_{MAX}$  versus Lg [142].

Micromachines **2021**, 12, 1159

Figure 10. Simulation for T-gate capacitance [142].

Figure 11. Benchmark for frequency versus Lg.

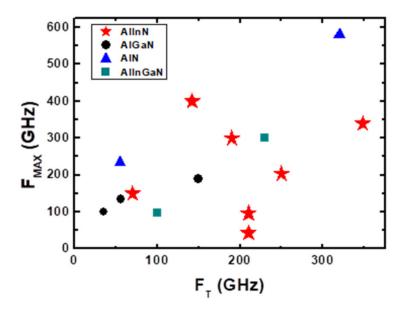

There are many device technologies have been developed based on GaN HEMT on SiC substrates. Most of those technologies can be applied on GaN HEMT on Si as well. We will describe some of the typical examples below. Hiroyuki Ichikawa et al. [150] designed 150 nm gate length InAlN/GaN and AlGaN/GaN HEMT, the AlInN/GaN HEMT showed high  $G_{\rm M}$  and exhibited a  $f_{\rm T}/{\rm fmax}$  of 70/150 GHz. Michael L. Schuette et al. [141] demonstrated a peak  $f_{\rm T}/{\rm fmax}$  of 348/340 GHz for 27 nm gate length on InAlN/GaN HEMT with gate recess. Ezgi Dogmus et al. [151] used ultra-thin AlN (4 nm) barrier to replace AlGaN and in-situ SiN demonstrated a  $f_{\rm T}/{\rm fmax}$  of 55/235 GHz. Jeong-Sun Moon et al. [152] designed 50 nm gate length AlGaN/GaN HEMT with graded AlGaN barrier and n++regrowth, and the HEMT exhibited a ft/fmax of 156/308 GHz. Lei Li et al. [153] demonstrated  $f_{\rm T}/{\rm fmax}$  of 250/204 GHz using n++regrowth for InAlN/GaN HEMT on Si substrate. Figure 12 benchmark  $f_{\rm T}$  versus  $f_{\rm MAX}$  [141,150–155].

Micromachines **2021**, 12, 1159 14 of 32

**Figure 12.** Comparison of the measured  $f_T$  and  $f_{MAX}$  in GaN-based HEMTs from literature.

GaN HEMT on Si also have high load pull result comparable to SiC substrate [155], nevertheless, GaN HEMT on Si substrate shows high potential. D.C. Dumka et al. [156] demonstrated 13.1 dB linear gain, maximum  $P_{OUT}=34.5$  dBm, output power density 7 W/mm and PAE 65.6% at 10 GHz in X band. Diego Marti et al. [157] showed 6 dB linear gain, output power density 1.35 W/mm, and PAE 12% at 94 GHz in W band.

For used in 5G mm-Wave communications, higher data rates require more complex communication systems such as Multi-input Multi-output (MIMO). MIMO employs complex frequency and phase division. So high linearity devices are required to avoid interaction each complex frequency bands. J. Vidkjær et al. [158] summarized some solution for linearity include geometrical, layout and epitaxial design. Weichuan Xing et al. [159] designed 150\*150 nm nanostrip gate hole structure by BCl<sub>3</sub>/Cl<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> insulator which have good linearity. Jeong-sun Moon et al. [160] used AlGaN/GaN graded channel which have good PAE and linearity. Bin Hou et al. [161] used barrier layer of sandwich structure and AlGaN back barrier which show good power performance and linearity. Kai Zhang et al. [162] used Fin-FET HEMT that have good linearity compared to the planar HEMT.

#### 3. GaN HEMT on Silicon-on-Insulator (SOI) Substrates

# 3.1. GaN Epitaxial Growth on Silicon-on-Insulator (SOI) Substrates

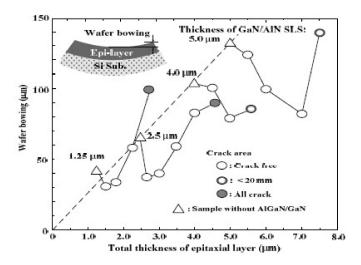

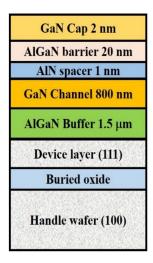

In epitaxial issues, the bowing effect always exists on the hetero-interface due to the lattice mismatch and the thermal expansion differences. T. Egawa from Nagoya Institute of Technology has reported a relative function of the wafer bowing and epitaxial thickness of AlGaN/GaN HEMT on Si [163], as shown in Figure 13. A thicker GaN/AlN superlattice structure exhibits higher bowing value in these experiments. It is a wafer bowing reference in HEMT epitaxial developments on Si. However, based on the outstanding electrical isotropic and mechanical features of the SOI substrate, it is expected to be a significant contender as a technological platform for mass production of GaN HEMT in the near future. However, the SOI substrate still suffer from a bowing effect, which may result in broken wafers or difficulties in subsequent fabrication processing steps, as well as a lower temperature tolerance during wafer process. Recently, from our study, we demonstrate the growth of AlGaN/GaN heterostructure on a 150-mm SOI substrate with different boron doping concentration in handle wafer, as shown in Figure 14. By heavily doping Boron in silicon handle wafer of SOI substrate, we can effectively reduce the bowing effect, increase the thickness of the epitaxial layer, and further improve the device performance. Heavily doped handle wafer causes a reduction in wafer bowing by >97%, as shown in

Micromachines **2021**, 12, 1159 15 of 32

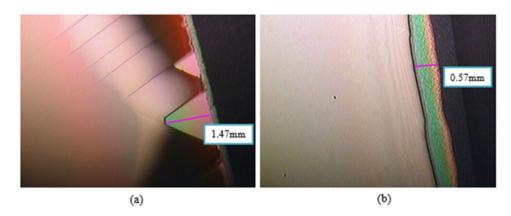

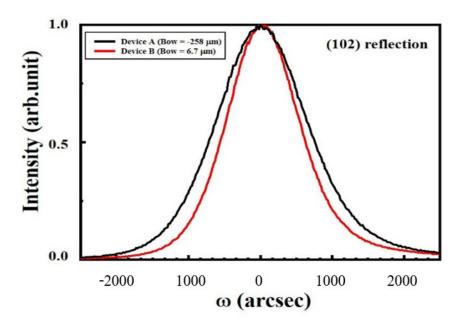

Table 3. Moreover, it can be seen from Figure 15 that the issue of edge cracks for the heavily doped SOI substrate (sample B) are great improved, and there is no peeling phenomenon, which means that the heavily doped SOI substrate have better ability to resist the stress generated during GaN epitaxy. Figure 16 is the comparison of the half-width values of the GaN epitaxial layer (102) measured by X-ray diffraction analyzer. It can be observed that the BOW value is related to the epitaxial quality. That is, the more severe the bowing effect, the worse the epitaxial quality, which has also been demonstrated in GaN on SiC and bulk GaN substrate [164,165].

Figure 13. Wafer bowing as a function of total epitaxial layer thickness [163].

Figure 14. Schematic cross-section of AlGaN/GaN HEMT on SOI substrate.

Table 3. Device characteristic of different Boron doped level in handle wafer.

| Sample                                         | Α                                              | В                                              |  |  |

|------------------------------------------------|------------------------------------------------|------------------------------------------------|--|--|

| Dope-level                                     | Light doped                                    | Heavy doped                                    |  |  |

| Doping concentration (atoms-cm <sup>-3</sup> ) | $1.35 \times 10^{15} \sim 1.49 \times 10^{16}$ | $5.95 \times 10^{19} \sim 1.26 \times 10^{20}$ |  |  |

| Bowing (µm)                                    | -258                                           | 6.7                                            |  |  |

| FWHM (arcsec) (1 0 2)                          | 1484                                           | 1188                                           |  |  |

Micromachines **2021**, 12, 1159

Figure 15. Top section of OM image (a) Sample A. (b) Sample B.

**Figure 16.** Asymmetric (102) XRD  $\omega$ -scan rocking curves of substrate with big BOW value (black) and small BOW value (red) measured from surface.

# 3.2. Power GaN HEMT on SOI

In the past several years, enhancement mode (E-mode) AlGaN/GaN HEMTs have been demonstrated to be the potential devices for next generation high efficiency power switches and converters application [2,166]. Currently, SiC [19] and Si [167] are the most popular substrates for GaN HEMT. However, GaN-on-SOI has been considered as a highly potential option which may provide better performance in high frequency and high-power system, owing to its capability in defect reduction of epitaxial layer, as described in Section 3.1.

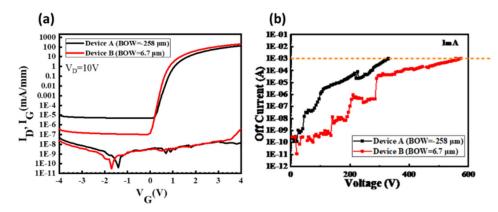

According to our studies shown in Section 3.1, the BOW value of GaN on SOI substrate is close related to threading dislocation density (TDD) and epitaxial quality. The HEMT devices on SOI substrate with lower BOW value exhibit 1 order smaller off-state leakage and 8.4% smaller specific on resistance, also 68.8% improvement is observed in 3-terminal off-state breakdown voltage (BV $_{\rm GD}$ ), shown as Figure 17. Moreover, the dynamic R $_{\rm ON}$  degradation can be reduced. This implies that by heavily doping in handle wafer not only reduce the bowing effect, but also improve the quality of substrate and the performance of high-power device.

Micromachines **2021**, 12, 1159 17 of 32

**Figure 17.** (a)  $I_{DS}$ - $V_{GS}$  characteristics of HEMTs with big BOW value (Device A, black line) and small BOW value (Device B, red line) ( $V_{DS}$  = 10 V). (b) Three-terminal off-state characteristic of the E-mode HEMTs at  $V_{GS}$  = -5 V.

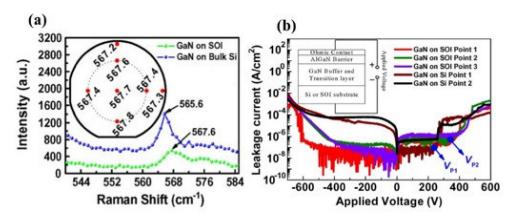

GaN-on-SOI substrate exhibits a capability to improve the power device performance and also have been proven by many research teams [168-172] including smaller reverse recovery leakage [169], higher breakdown voltage [168,169] and smaller vertical leakage [172]. Kevin J. Chen et al. [169] reported the SOI substrate with a reduced stress in the GaN epilayers (shown as Figure 18a) and an excellent E-mode HEMTs on SOI produced by fluorine plasma implantation method with a high ON/OFF current ratio ( $10^8-10^9$ ), large breakdown voltage (1471 V with floating substrate), and also a smaller vertical leakage at reverse bias, as shown in Figure 18b.

**Figure 18.** (a) GaN-on-SOI and GaN-on-Si (bulk) wafers under Micro-Raman spectroscopy. The E2 peak on the GaN-on-SOI wafer was mapped (Inset) (b) Characteristics of vertical leakage on GaN-on-SOI and GaN-on-Si (bulk) platforms [169].

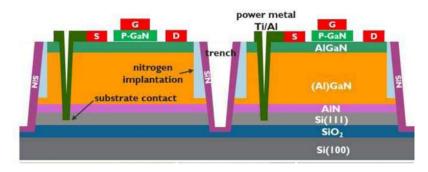

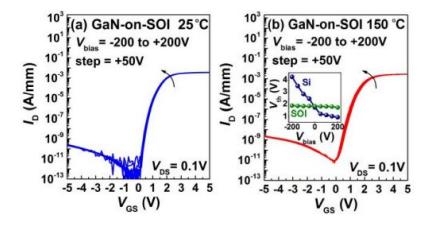

Moreover, most GaN power switching systems are currently produced using a multichip approach, resulting in significant complexity and expense [173–175]. Monolithic integration of GaN-based power devices has steadily gained interest for GaN high-power systems. The benefits of monolithic integration of GaN power systems on a single chip include minimizing parasitic inductance, reducing die size, and enhancing design flexibility [107,176]. To prevent mutual influence between the devices in monolithic GaN power integrated circuit, it suggests that the low and high side HEMT transistors must be fully isolated for a half bridge, as shown in Figure 19 [172,177]. However, it is challenging to accomplish on GaN-on-Si substrates because those HEMTs share a common conductive Si substrate. Figure 20a shows the transfer characteristics of a GaN monolithic half bridge with a common Si substrate biased from -200 to 200 V at 150 °C. Significant variations in threshold voltage (Vth) and drive current are seen when the Si substrate is biased negatively. Nevertheless, using GaN-on-SOI and a trench isolation method, this

Micromachines **2021**, 12, 1159 18 of 32

issue could be overcome [172,177,178]. The transfer characteristics of GaN-on-SOI HEMT, as shown in Figure 20b, illustrate the benefits of device isolation. When the substrate of a neighboring device is biased between -200 V and 200 V, transfer characteristics vary relatively little, which is in sharp contrast to characteristics on a silicon substrate.

Figure 19. Schematic cross-section of the isolated e-mode p-GaN HEMT [177].

**Figure 20.** Transfer characteristics while simultaneously biasing the silicon substrate from -200 V to 200 V (a) with a common silicon substrate (b) with SOI substrate [177].

# 3.3. RF GaN HEMT on SOI

In addition to the power devices, AlGaN/GaN HEMTs have also been demonstrated to be the potential devices for RF applications [179–182]. Moreover, GaN-based MMIC (Microwave Monolithic Integrated Circuit) has steadily gained interest as compared to a system in package or a multi-chip module, since monolithic integration of GaN RF systems allows for smaller, cheaper, and less complicated circuitry [181,182].

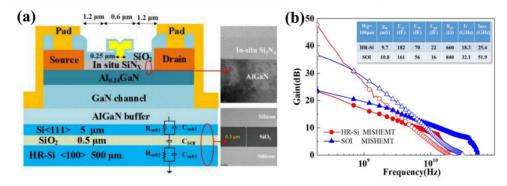

SOI substrate is outstanding for its better vertical isolation performance and a lower substrate loss [183]. Besides, when compared to GaN on Si substrate devices, GaN on SOI substrate devices demonstrated better DC, breakdown voltage, and RF properties [170,184,185]. It was demonstrated that GaN-on-SOI substrates perform better in terms of tensile stress relaxation and surface flatness than Si substrates. It can result in a reduction of defect density, which is further supported by pulse and low-frequency noise measurements. The SOI substrate capacitances extracted from the small signal model are lower than the HR-Si substrate, as illustrated in Figure 21, owing to the series connection of device layer, buried oxide layer, and handle wafer of SOI substrate. As a result of the small substrate capacitances of SOI substrate shunt to the C<sub>DS</sub>, the effective C<sub>DS</sub> items that dominated the feedback capacitance were decreased. Furthermore, the utilization of SOI substrate can increase the device's bandwidth and linearity was proven at the same time, as shown in Figure 21b [185].

Micromachines **2021**, 12, 1159

**Figure 21.** (a) Cross-sectional structure of MISHEMT on SOI substrate (b) high frequency parameters for AlGaN/GaN MISHEMT on SOI substrate(blue) and AlGaN/GaN MISHEMT on HR-Si substrate (red). [185].

#### 4. GaN HEMTs on QST Substrates

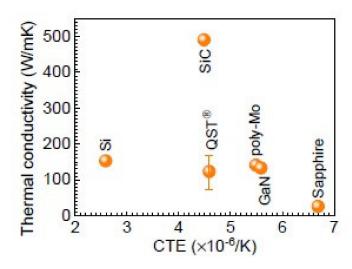

Recently, a new engineered substrate consists of polycrystalline core and single crystalline surface layer, which exhibits a good thermal expansion and crystalline match to GaN, are presented. It provides a good matching in coefficient of thermal expansion (CTE) characteristics with Gallium Nitride (GaN). The template enables growth of thick and high quality GaN semiconductor layers on 8- and even 12-inch wafers and support a lower cost for GaN devices in power supplies and RF transmitters commercial markets. According to Qromis Inc., Qromis Substrate Technology (QST) promises a thicker GaN epitaxy to expands the GaN HEMT's limitation in breakdown voltage roadmaps (up to 1200 V) in power devices in vertical electron paths. Compatible with conventional GaN growth platforms, as the substrates are thermally matched to GaN, it offers low defect density, high crystal quality, and low wafer bow. As previous sections described, the high quality GaN power devices enabled are potential for a higher switching speed, simpler and smaller form, and higher-temperature operation.

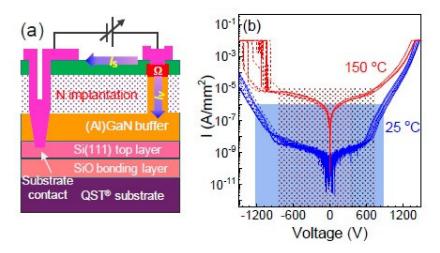

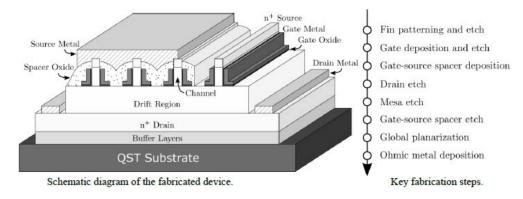

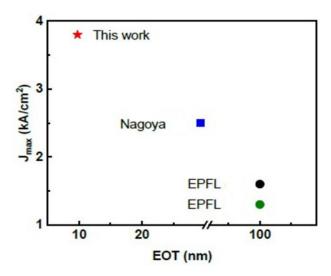

The Naval Research Laboratory (NRL), Kyma and Qromis Technology reported some material characterization studies. It's interesting that GaN device layers up to 15μm were demonstrated with a wafer bow of 1 µm for growth on 150-mm-diameter substrates [186]. The development to manufacture 200 mm freestanding GaN from 300 mm QST® [187] also looks promising. According to several reports, the thermal conductivity and CTE relationship for different substrates are depicted in Figure 22. It also shows a high quality AlGaN/GaN buffers grown on substrates with a less mismatch in coefficient of thermal expansion (CTE). Figure 23 shows an illustration of evaluating the vertical buffer leakage currents in both reverse and forward bias mode, and it exhibits a maximum of reverse current of 1 µA/mm at 25 °C and 10 µA/mm at 150 °C as the reverse voltage exceeds 700 V. The leakage current increases by ~3 orders from 25 to 150 °C [188]. According to a MIT group, a GaN vertical power FinFETs on engineered substrate was demonstrated [189]. Figure 24 shows the schematic of the quasi-vertical device architecture, which consists of 132 fins with 100 nm, 700 nm and 21 um widths, spacing and length respectively. It exhibits a current density of  $J_{DS}=3.8 \text{ kA/cm}^2$  at  $V_{GS}=1.5 \text{ V}$  and  $V_{DS}=4 \text{ V}$ , and a maximum  $g_m = 2 \text{ kS/cm}^2$  at  $V_{DS} = 4 \text{ V}$ . The current density in each fin is higher than  $30 \text{ kA/cm}^2$  at the same bias condition. They also benchmark vertical and quasi-vertical MOSFETs on non-GaN substrates, as shown in Figure 25.

Micromachines **2021**, 12, 1159 20 of 32

**Figure 22.** Different substrate for coefficient of thermal expansion (CTE) and thermal conductivity [188].

**Figure 23.** (a) The illustration of vertical buffer leakage measurements (b) The leakage current density under voltage bias for a 5.6 mm-thick buffer grown on 200 mm GaN-on-QST<sup>®</sup> substrate [188].

Figure 24. A schematic diagram of the vertical GaN FinFET devices and fabrication steps [189].

Micromachines **2021**, 12, 1159 21 of 32

**Figure 25.** Benchmarking maximum current density in vertical GaN-on-Silicon transistors as a function of equivalent oxide thickness [189].

# 5. Heterogeneous Integration of GaN HEMT

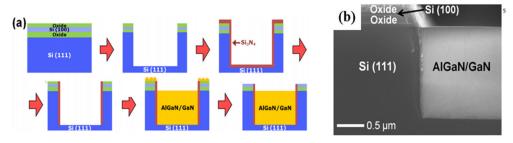

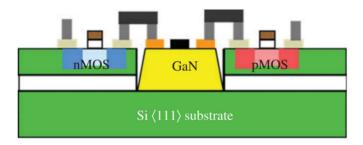

The conventional silicon-based RF devices fabricated on 32 nm Si complementary metal-oxide-semiconductor (CMOS) with a cut-off frequency of 445 GHz were exhibited and the cut-off frequency are expected to further scale [190]. However, despite having impressive cut-off frequency, Si CMOS is not well suited with high voltage or high-power density due to lower breakdown voltage whereas GaN devices are more suitable for these types of applications. Hence, co-integrating Si with GaN on a single chip may help in achieving high power and high-performance application. The main motivation for integrating GaN and CMOS is due to the superior GaN performance in fast power switching and the high functionality of CMOS logic, reduction in interconnect distance as well as losses, smaller form factor, reduction in power consumption, lower cost, and lower assembling complexity [191,192]. There are two types of GaN and CMOS integration variants on wafer-level namely Monolithic Integration and Heterogeneous Integration (HI). In the past few years, the key technology development and production is heterogeneous integration. For high-frequency applications in space and defense and the 5G application in the commercial world, heterogeneous integration for RF has become an essential task. Typically, hetero-integration of RF devices is done with different semiconductor materials not only CMOS to address the required specific performance like Diverse Accessible Heterogeneous Integration (DAHI) technology [193]. HI methods can be wafer to wafer (WTW), chip to wafer (CTW), or Chip to Chip (CTC), etc [194]. CTW and CTC are usually used for integrating dissimilar heterogeneous materials as it minimizes coefficient of Thermal Expansion (CTE) as well as wafer warpage issues which enable known good die (KGD) and pretty good die (PGD) that helps in achieving good yield. In WTW integration, CTE issues are challenging, and the yield is compromised. High frequency 3D HI faces challenges such as implementing effective 3D screening method as in some cases chiplets don't have test pads and there is insufficient availability of process design kit (PDK) with RF functionality, co-simulation capability, and 3D parasitic extraction [194]. One heterogeneous integration method that makes the GaN power system compatible with CMOS fabrication using SOI substrate was stated by the IBM research division [195] as shown in Figure 26.

Micromachines **2021**, 12, 1159 22 of 32

**Figure 26.** (a) Heterogeneous integration of SOI substrate with top Si (100) and bottom Si (111) and GaN epitaxial (b) SEM cross-section [195].

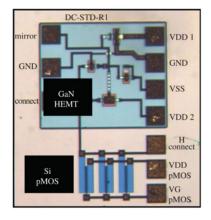

A DC-DC boost converter was designed using GaN power transistors integrated with bipolar-CMOS-DMOS (BCD) which combines both the advantages of high-voltage low-loss GaN devices and high-integration BCD circuits [196]. The designed GaN2BCD technology is a promising power converter application platform. Deeply scaled E/D-mode GaN HEMTs integrated with monolithically integrable GaN Schottky diodes were able to offer advantages in MMIC applications [142]. GaN-on-Si monolithic microwave integrated circuits (MMICs) were fabricated on 200-mm-diameter using a fully CMOS-compatible fabrication process which enables integration of wafer-level 3D GaN MMICs with Si CMOS circuits for performance and functionality enhancement while the size, weight, power, and cost is reduced [197]. As shown in Figure 27, a team from Raytheon [198] in the United States successfully demonstrated fabricating GaN HEMTs in windows on SOI wafers containing Si CMOS transistors, with DC and RF performance comparable to GaN HEMTs on SiC substrate, as well as a first GaN-Si CMOS heterogeneously integrated MMIC: GaN amplifier with CMOS gate bias control circuitry (a current mirror) and heterogeneous interconnects, as shown in Figure 28.

Figure 27. GaN HEMT and Si CMOS are heterogeneously combined on a modified SOI wafer [198].

Figure 28. GaN-Si CMOS heterogeneously integrated MMIC [198].

Micromachines 2021, 12, 1159 23 of 32

For heterogeneous integration, wafer bonding is one of the most promising integration approach for integrating group III-V materials and CMOS on Si [191]. Monolithic structure can be done by direct wafer bonding [199] or heteroepitaxy [200]. Direct wafer bonding can be used for integrating non-lattice matched semiconductors and also for integrating different crystal structures. Moreover, no additional intermediate layers are required and can also integrate two or more wafers. However, it requires a very flat, smooth, and particle-free surface along with fitting wafer diameter and chip sizes.

A new 3D integrated circuit (3DIC) solution, System on Integrated Chips (SoICTM), was developed by Taiwan Semiconductor Manufacturing Company (TSMC) [201] to integrate active and passive chips into a new integrated SoC system. Comparing the typical 3DIC stacking with SoIC, the latter offers higher I/O density bonding density, lower energy consumption/ bit data, lower electrical parasites, and lower thermal resistance [190] which might help in unleashing the boundary of IC designer on heterogeneous integrations in future 5G, AI, mobile, and HPC applications. IMEC developed NaNO-TSV (Through Silicon Vias) connection for heterogeneous integration as 3D system-on-chip (3D-SoC) integration technology which possess a wafer-to-wafer bonding approach combined with via-last TSV connection [202]. Finally, Wafer-level packaging (WLP) of the heterogeneous integrated devices is required to be protected from the environment [203]. WLP also eliminates assembly equipment, reduces package cost, and minimizes the chip size as well as provides high yield and high reliability.

#### 6. Conclusions

In the previous GaN HEMTs development roadmap, the heterogeneous epitaxy has been one of the issues affecting devices performance. The wide application of compound semiconductors has attracted wide attention and become matured gradually, including and ranging from RF power amplifiers to electronic systems. The demand tendency for power devices is increasing, especially in electric vehicles and the fast-charging applications. As high-frequency communications keep developing, the GaN HEMT technology will be very critical. Traditional silicon substrates will no longer be only GaN HEMTs template but will be replaced by other smooth and friendly substrate for some applications. These advanced substrate technologies efficiently improve device characteristics, performance, and reliability. It will bring thicker GaN buffer layer, high thermal conductivity, and high resistance substrate in the future high-power high-frequency components. In addition, the heterogeneous integration of GaN HEMTs and CMOS structure have become a new direction. In this article, we provide a brief and comprehensive overview of these important technology developments.

**Author Contributions:** Data curation, Y.-Y.L., C.L., Y.-T.C., Y.-W.H., P.-T.T. and L.-H.H.; project administration, Y.-Y.L., W.-C.L., A.-J.T. and L.-H.H.; supervision, Y.-J.C., C.-H.L., H.-C.K. and E.Y.C.; writing—original draft, Y.-Y.L., C.L., Y.-T.C., P.-T.T. and L.-H.H.; writing—review and editing, L.-H.H. and Y.-Y.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** Ministry of Science and Technology, Taiwan (107-2221-E-009-113-MY3, 108-2221-E-009-113-MY3, 109-2222-E-009-001-MY3, 110-2218-E-182-001-MY3).

**Acknowledgments:** The authors would like to thank Ministry of Science and Technology, Industrial Technology Research Institute, Taiwan Semiconductor Research Institute, and the Semiconductor Research Center, Hon Hai Research Institute, for the helpful discussion.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Chuang, R.W.; Chang, S.; Chang, S.-J.; Chiou, Y.; Lu, C.; Lin, T.; Lin, Y.; Kuo, C.; Chang, H.-M. Gallium nitride metal-semiconductor-metal photodetectors prepared on silicon substrates. *J. Appl. Phys.* **2007**, 102, 073110. [CrossRef]

- 2. Mishra, U.K.; Parikh, P.; Wu, Y.-F. AlGaN/GaN HEMTs-an overview of device operation and applications. *Proc. IEEE* **2002**, *90*, 1022–1031. [CrossRef]

Micromachines **2021**, 12, 1159 24 of 32

3. Wu, Y.-F.; Kapolnek, D.; Ibbetson, J.P.; Parikh, P.; Keller, B.P.; Mishra, U.K. Very-high power density AlGaN/GaN HEMTs. *IEEE Trans. Electron Devices* **2001**, *48*, 586–590.

- 4. Wu, Y.-F.; Saxler, A.; Moore, M.; Smith, R.; Sheppard, S.; Chavarkar, P.; Wisleder, T.; Mishra, U.; Parikh, P. 30-W/mm GaN HEMTs by field plate optimization. *IEEE Electron Device Lett.* **2004**, 25, 117–119. [CrossRef]

- 5. Asif Khan, M.; Bhattarai, A.; Kuznia, J.; Olson, D. High electron mobility transistor based on a GaN-Al<sub>x</sub>Ga<sub>1-x</sub>N heterojunction. *Appl. Phys. Lett.* **1993**, *63*, 1214–1215. [CrossRef]

- 6. Dumka, D.; Lee, C.; Tserng, H.; Saunier, P.; Kumar, M. AlGaN/GaN HEMTs on Si substrate with 7 W/mm output power density at 10 GHz. *Electron. Lett.* **2004**, *40*, 1023–1024. [CrossRef]

- 7. Eastman, L.F.; Tilak, V.; Smart, J.; Green, B.M.; Chumbes, E.M.; Dimitrov, R.; Kim, H.; Ambacher, O.S.; Weimann, N.; Prunty, T. Undoped AlGaN/GaN HEMTs for microwave power amplification. *IEEE Trans. Electron Devices* **2001**, *48*, 479–485. [CrossRef]

- 8. Kemerley, R.T.; Wallace, H.B.; Yoder, M.N. Impact of wide bandgap microwave devices on DoD systems. *Proc. IEEE* **2002**, *90*, 1059–1064. [CrossRef]

- 9. Duboz, J.Y. GaN as seen by the industry. Phys. Status Solidi (A) 1999, 176, 5–14. [CrossRef]

- 10. Dunleavy, L.; Baylis, C.; Curtice, W.; Connick, R. Modeling GaN: Powerful but challenging. *IEEE Microw. Mag.* **2010**, *11*, 82–96. [CrossRef]

- 11. Mimura, T.; Hiyamizu, S.; Fujii, T.; Nanbu, K. A new field-effect transistor with selectively doped GaAs/n-AlxGa1-xAs heterojunctions. *Jpn. J. Appl. Phys.* **1980**, *19*, L225. [CrossRef]

- 12. Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R. The 2018 GaN power electronics roadmap. *J. Phys. D: Appl. Phys.* **2018**, *51*, 163001. [CrossRef]

- 13. Sano, H.; Ui, N.; Sano, S. A 40W GaN HEMT Doherty power amplifier with 48% efficiency for WiMAX applications. In *Proceedings* of the IEEE Compound Semiconductor Integrated Circuits Symposium, Portland, OR, USA, 14–17 October 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 1–4.

- 14. Gaska, R.; Yang, J.; Osinsky, A.; Chen, Q.; Khan, M.A.; Orlov, A.; Snider, G.; Shur, M. Electron transport in AlGaN–GaN heterostructures grown on 6H–SiC substrates. *Appl. Phys. Lett.* **1998**, *72*, 707–709. [CrossRef]

- 15. Hirama, K.; Taniyasu, Y.; Kasu, M. AlGaN/GaN high-electron mobility transistors with low thermal resistance grown on single-crystal diamond (111) substrates by metalorganic vapor-phase epitaxy. *Appl. Phys. Lett.* **2011**, *98*, 162112. [CrossRef]

- 16. Tang, X.; Rousseau, M.; Defrance, N.; Hoel, V.; Soltani, A.; Langer, R.; De Jaeger, J.C. Thermal behavior analysis of GaN based epi-material on different substrates by means of a physical–thermal model. *Phys. Status Solidi* (A) **2010**, 207, 1820–1826. [CrossRef]

- 17. Yamaki, F.; Inoue, K.; Ui, N.; Kawano, A.; Sano, S. A 65% drain efficiency GaN HEMT with 200 W peak power for 20 V to 65 V envelope tracking base station amplifier. In *Proceedings of the 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011*; IEEE: Piscataway, NJ, USA, 2011; pp. 1–4.

- 18. Mitani, E.; Aojima, M.; Maekawa, A.; Sano, S. An 800-W AlGaN/GaN HEMT for S-band high-power application. *CSMantech Line Dig.* **2007**, *0.2*, 1–3.

- 19. Pengelly, R.S.; Wood, S.M.; Milligan, J.W.; Sheppard, S.T.; Pribble, W.L. A review of GaN on SiC high electron-mobility power transistors and MMICs. *IEEE Trans. Microw. Theory Tech.* **2012**, *60*, 1764–1783. [CrossRef]

- 20. Wu, Y.-F.; Moore, M.; Saxler, A.; Wisleder, T.; Parikh, P. 40-W/mm double field-plated GaN HEMTs. In *Proceedings of the 2006 64th device research conference, State College, PA, USA, 26–28 June 2006*; IEEE: Piscataway, NJ, USA, 2006; pp. 151–152.

- 21. Dumka, D.; Chou, T.; Jimenez, J.; Fanning, D.; Francis, D.; Faili, F.; Ejeckam, F.; Bernardoni, M.; Pomeroy, J.; Kuball, M. Electrical and thermal performance of AlGaN/GaN HEMTs on diamond substrate for RF applications. In *Proceedings of the 2013 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 13–16 October 2013*; IEEE: Piscataway, NJ, USA, 2013; pp. 1–4.

- 22. Smith, R.P.; Sheppard, S.; Wu, Y.-F.; Heikman, S.; Wood, S.; Pribble, W.; Milligan, J. AlGaN/GaN-on-SiC HEMT technology status. In *Proceedings of the 2008 IEEE Compound Semiconductor Integrated Circuits Symposium, Monterey, CA, USA, 12–15 October 2008*; IEEE: Piscataway, NJ, USA, 2008; pp. 1–4.

- 23. Javorka, P.; Alam, A.; Wolter, M.; Fox, A.; Marso, M.; Heuken, M.; Luth, H.; Kordos, P. AlGaN/GaN HEMTs on (111) silicon substrates. *IEEE Electron Device Lett.* **2002**, 23, 4–6. [CrossRef]

- 24. Lenci, S.; De Jaeger, B.; Carbonell, L.; Hu, J.; Mannaert, G.; Wellekens, D.; You, S.; Bakeroot, B.; Decoutere, S. Au-free AlGaN/GaN power diode on 8-in Si substrate with gated edge termination. *IEEE Electron Device Lett.* **2013**, *34*, 1035–1037. [CrossRef]

- 25. Yacoub, H.; Fahle, D.; Finken, M.; Hahn, H.; Blumberg, C.; Prost, W.; Kalisch, H.; Heuken, M.; Vescan, A. The effect of the inversion channel at the AlN/Si interface on the vertical breakdown characteristics of GaN-based devices. *Semicond. Sci. Technol.* **2014**, *29*, 115012. [CrossRef]

- 26. Sahoo, A.; Subramani, N.; Nallatamby, J.-C.; Sylvain, L.; Loyez, C.; Quéré, R.; Medjdoub, F. Small signal modeling of high electron mobility transistors on silicon and silicon carbide substrate with consideration of substrate loss mechanism. *Solid State Electron*. **2016**, *115*, 12–16. [CrossRef]

- 27. Luong, T.T.; Lumbantoruan, F.; Chen, Y.Y.; Ho, Y.T.; Weng, Y.C.; Lin, Y.C.; Chang, S.; Chang, E.Y. RF loss mechanisms in GaN-based high-electron-mobility-transistor on silicon: Role of an inversion channel at the AlN/Si interface. *Phys. Status Solidi* (*A*) **2017**, 214, 1600944. [CrossRef]

- 28. Chandrasekar, H.; Bhat, K.; Rangarajan, M.; Raghavan, S.; Bhat, N. Thickness dependent parasitic channel formation at AlN/Si interfaces. *Sci. Rep.* **2017**, *7*, 1–10. [CrossRef]

Micromachines **2021**, 12, 1159 25 of 32

29. Hsu, S.S.; Tsou, C.-W.; Lian, Y.-W.; Lin, Y.-S. GaN-on-silicon devices and technologies for RF and microwave applications. In *Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 24–26 August 2016*; IEEE: Piscataway, NJ, USA, 2016; pp. 1–3.

- 30. Pan, L.S.; Kania, D.R. Diamond: Electronic Properties and Applications; Springer Science & Business Media: Boston, MA, USA, 2013.

- 31. Hirama, K.; Kasu, M.; Taniyasu, Y. RF high-power operation of AlGaN/GaN HEMTs epitaxially grown on diamond. *IEEE Electron Device Lett.* **2012**, *33*, 513–515. [CrossRef]

- 32. Diduck, Q.; Felbinger, J.; Eastman, L.; Francis, D.; Wasserbauer, J.; Faili, F.; Babic, D.; Ejeckam, F. Frequency performance enhancement of AlGaN/GaN HEMTs on diamond. *Electron. Lett.* **2009**, *45*, 758–759. [CrossRef]

- 33. Hirama, K.; Taniyasu, Y.; Kasu, M. Heterostructure growth of a single-crystal hexagonal AlN (0001) layer on cubic diamond (111) surface. *J. Appl. Phys.* **2010**, *108*, 013528. [CrossRef]

- 34. Taniyasu, Y.; Kasu, M. MOVPE growth of single-crystal hexagonal AlN on cubic diamond. *J. Cryst. Growth* **2009**, *311*, 2825–2830. [CrossRef]

- 35. Yagi, S.; Shimizu, M.; Inada, M.; Yamamoto, Y.; Piao, G.; Okumura, H.; Yano, Y.; Akutsu, N.; Ohashi, H. High breakdown voltage AlGaN/GaN MIS–HEMT with SiN and TiO2 gate insulator. *Solid-State Electron.* **2006**, *50*, 1057–1061. [CrossRef]

- 36. Mukhopadhyay, P.; Bag, A.; Gomes, U.; Banerjee, U.; Ghosh, S.; Kabi, S.; Chang, E.Y.; Dabiran, A.; Chow, P.; Biswas, D. Comparative DC characteristic analysis of AlGaN/GaN HEMTs grown on Si (111) and sapphire substrates by MBE. *J. Electron. Mater.* **2014**, *43*, 1263–1270. [CrossRef]

- 37. Douglas, E.; Ren, F.; Pearton, S. Finite-element simulations of the effect of device design on channel temperature for AlGaN/GaN high electron mobility transistors. *J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom.* **2011**, 29, 020603. [CrossRef]

- 38. Manoi, A.; Pomeroy, J.W.; Killat, N.; Kuball, M. Benchmarking of thermal boundary resistance in AlGaN/GaN HEMTs on SiC substrates: Implications of the nucleation layer microstructure. *IEEE Electron Device Lett.* **2010**, *31*, 1395–1397. [CrossRef]

- 39. Riedel, G.J.; Pomeroy, J.W.; Hilton, K.P.; Maclean, J.O.; Wallis, D.J.; Uren, M.J.; Martin, T.; Forsberg, U.; Lundskog, A.; Kakanakova-Georgieva, A. Reducing thermal resistance of AlGaN/GaN electronic devices using novel nucleation layers. *IEEE Electron Device Lett.* 2008, 30, 103–106. [CrossRef]

- 40. Nochetto, H.C.; Jankowski, N.R.; Bar-Cohen, A. The impact of GaN/substrate thermal boundary resistance on a HEMT device. In Proceedings of the ASME International Mechanical Engineering Congress and Exposition, Denver, CO, USA, 11–17 November 2011; pp. 241–249.

- 41. Park, K.; Bayram, C. Thermal resistance optimization of GaN/substrate stacks considering thermal boundary resistance and temperature-dependent thermal conductivity. *Appl. Phys. Lett.* **2016**, *109*, 151904. [CrossRef]

- 42. Hull, R.; Osgood, R.; Sakaki, H. Nitride Semiconductors and Devices; Springer: Berlin/Heidelberg, Germany, 1999.

- 43. Kuzmík, J.; Bychikhin, S.; Pogány, D.; Gaquière, C.; Pichonat, E.; Morvan, E. Investigation of the thermal boundary resistance at the III-nitride/substrate interface using optical methods. *J. Appl. Phys.* **2007**, *101*, 054508. [CrossRef]

- 44. Fletcher, A.A.; Nirmal, D.; Ajayan, J.; Arivazhagan, L. An intensive study on assorted substrates suitable for high JFOM AlGaN/GaN HEMT. Silicon 2021, 13, 1591–1598. [CrossRef]

- 45. Mimura, T.; Yokoyama, N.; Kusakawa, H.; Suyama, K.; Fukuta, M. MP-A4 GaAs MOSFET for low-power high-speed logic applications. *IEEE Trans. Electron Devices* **1979**, 26, 1828. [CrossRef]

- 46. Schwierz, F.; Ambacher, O. Recent advances in GaN HEMT development. In *Proceedings of the 11th IEEE International Symposium on Electron Devices for Microwave and Optoelectronic Applications*, 2003, EDMO 2003, Orlando, FL, USA, 18 November 2003; IEEE: Piscataway, NJ, USA, 2003; pp. 204–209.

- 47. Lidow, A.; De Rooij, M.; Strydom, J.; Reusch, D.; Glaser, J. *GaN Transistors for Efficient Power Conversion*; John Wiley & Sons: Hoboken, NJ, USA, 2019.

- 48. Liu, Q.; Lau, S. A review of the metal-GaN contact technology. Solid State Electron. 1998, 42, 677-691. [CrossRef]

- 49. Liu, Q.; Yu, L.; Lau, S.; Redwing, J.; Perkins, N.; Kuech, T. Thermally stable PtSi Schottky contact on n-GaN. *Appl. Phys. Lett.* **1997**, 70, 1275–1277. [CrossRef]

- 50. Kordoš, P.; Heidelberger, G.; Bernát, J.; Fox, A.; Marso, M.; Lüth, H. High-power SiO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor heterostructure field-effect transistors. *Appl. Phys. Lett.* **2005**, *87*, 143501. [CrossRef]

- 51. Ohmaki, Y.; Tanimoto, M.; Akamatsu, S.; Mukai, T. Enhancement-Mode AlGaN/AlN/GaN High Electron Mobility Transistor with Low On-State Resistance and High Breakdown Voltage. *Jpn. J. Appl. Phys.* **2006**, 45, L1168–L1170. [CrossRef]

- 52. Medjdoub, F.; Derluyn, J.; Cheng, K.; Leys, M.; Degroote, S.; Marcon, D.; Visalli, D.; van Hove, M.; Germain, M.; Germain, G. Low On-Resistance High-Breakdown Normally Off AlN/GaN/AlGaN DHFET on Si Substrate. *IEEE Electron Device Lett.* **2010**, 31, 111–113. [CrossRef]

- 53. Mizutani, T.; Ito, M.; Kishimoto, S.; Nakamura, F. AlGaN/GaN HEMTs With Thin InGaN Cap Layer for Normally Off Operation. *IEEE Electron Device Lett.* **2007**, *28*, 549–551. [CrossRef]

- 54. Ostermaier, C.; Pozzovivo, G.; Carlin, J.F.; Basnar, B.; Schrenk, W.; Douvry, Y.; Gaquiere, C.; DeJaeger, J.-C.; Cico, K.; Frohlich, K.; et al. Ultrathin InAlN/AlN Barrier HEMT With High Performance in Normally Off Operation. *IEEE Electron Device Lett.* 2009, 30, 1030–1032. [CrossRef]

Micromachines **2021**, 12, 1159 26 of 32

55. Brown, D.F.; Shinohara, K.; Williams, A.; Milosavljevic, I.; Grabar, R.; Hashimoto, P.; Willadsen, P.J.; Schmitz, A.; Corrion, A.L.; Kim, S. Monolithic Integration of Enhancement- and Depletion-Mode AlN/GaN/AlGaN DHFETs by Selective MBE Regrowth. *IEEE Trans. Electron Devices* **2011**, *58*, 1063–1067. [CrossRef]

- Guowang, L.; Zimmermann, T.; Cao, Y.; Chuanxin, L.; Xiu, X.; Ronghua, W. Threshold Voltage Control in Al0.72Ga0.28N/AlN/GaN HEMTs by Work-Function Engineering. IEEE Electron Device Lett. 2010, 31, 954–956.

- 57. Chiu, H.-C.; Yang, C.-W.; Chen, C.-H.; Fu, J.S.; Chien, F.-T. Characterization of enhancement-mode AlGaN/GaN high electron mobility transistor using N2O plasma oxidation technology. *Appl. Phys. Lett.* **2011**, *99*, 153508. [CrossRef]

- 58. Chiu, H.; Wu, J.; Yang, C.; Huang, F.; Kao, H. Low-Frequency Noise in Enhancement-Mode GaN MOS-HEMTs by Using Stacked Al2O3/Ga2O3/Gd2O3 Gate Dielectric. *IEEE Electron Device Lett.* **2012**, *33*, 958–960. [CrossRef]

- 59. Wang, X.; Saadat, O.I.; Xi, B.; Lou, X.; Molnar, R.J.; Palacios, T.; Gordon, R.G. Atomic layer deposition of Sc2O3 for passivating AlGaN/GaN high electron mobility transistor devices. *Appl. Phys. Lett.* **2012**, *101*, 232109. [CrossRef]

- 60. Cai, Y.; Zhou, Y.; Lau, K.M.; Chen, K.J. Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode. *IEEE Trans. Electron Devices* **2006**, *53*, 2207–2215. [CrossRef]

- 61. Moon, J.; Wu, S.; Wong, D.; Milosavljevic, I.; Conway, A.; Hashimoto, P.; Hu, M.; Antcliffe, M.; Micovic, M. Gate-recessed AlGaN-GaN HEMTs for high-performance millimeter-wave applications. *IEEE Electron Device Lett.* **2005**, 26, 348–350. [CrossRef]

- 62. Moon, J.S.; Wong, D.; Hussain, T.; Micovic, M.; Deelman, P.; Hu, M.; Antcliffe, M.; Ngo, C.; Hashimoto, P.; McCray, L. Submicron enhancement-mode AlGaN/GaN HEMTs. In *Proceedings of the 60th DRC. Conference Digest Device Research Conference, Santa Barbara*, CA, USA, 24–26 June 2002; IEEE: Piscataway, NJ, USA, 2002; pp. 23–24.

- 63. Okita, H.; Kaifu, K.; Mita, J.; Yamada, T.; Sano, Y.; Ishikawa, H.; Egawa, T.; Jimbo, T. High transconductance AlGaN/GaN-HEMT with recessed gate on sapphire substrate. *Phys. Status Solidi* (*A*) **2003**, 200, 187–190. [CrossRef]

- 64. Wang, W.-K.; Li, Y.-J.; Lin, C.-K.; Chan, Y.-J.; Chen, G.-T.; Chyi, J.-I. Low damage, Cl 2-based gate recess etching for 0.3-μm gate-length AlGaN/GaN HEMT fabrication. *IEEE Electron Device Lett.* **2004**, 25, 52–54. [CrossRef]

- 65. Kumar, V.; Kuliev, A.; Tanaka, T.; Otoki, Y.; Adesida, I. High transconductance enhancement-mode AlGaN/GaN HEMTs on SiC substrate. *Electron. Lett.* **2003**, *39*, 1758–1760. [CrossRef]

- 66. Lanford, W.; Tanaka, T.; Otoki, Y.; Adesida, I. Recessed-gate enhancement-mode GaN HEMT with high threshold voltage. *Electron. Lett.* 2005, 41, 449–450. [CrossRef]

- 67. Zhuang, D.; Edgar, J. Wet etching of GaN, AlN, and SiC: A review. Mater. Sci. Eng. R: Rep. 2005, 48, 1–46. [CrossRef]

- 68. Andreani, P.; Sjoland, H. Tail current noise suppression in RF CMOS VCOs. IEEE J. Solid-State Circuits 2002, 37, 342–348. [CrossRef]