# Article Gate-Stack Engineering to Improve the Performance of 28 nm Low-Power High-K/Metal-Gate Device

Jeewon Park <sup>1,2</sup>, Wansu Jang <sup>2</sup> and Changhwan Shin <sup>3,\*</sup>

- <sup>1</sup> Department of Semiconductor and Display Engineering, Sungkyunkwan University, Suwon 16419, Korea; tmfktys@g.skku.edu

- <sup>2</sup> Foundry, Samsung Electronics, Yongin 17113, Korea; wansu.jang@samsung.com

- <sup>3</sup> Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Korea

- Correspondence: cshin@skku.edu; Tel.: +82-31-290-7694

**Abstract:** In this study, a gate-stack engineering technique is proposed as a means of improving the performance of a 28 nm low-power (LP) high-k/metal-gate (HK/MG) device. In detail, it was experimentally verified that HfSiO thin films can replace HfSiON congeners, where the latter are known to have a good thermal budget and/or electrical characteristics, to boost the device performance under a limited thermal budget. TiN engineering for the gate-stack in the 28 nm LP HK/MG device was used to suppress the gate leakage current. Using the proposed fabrication method, the on/off current ratio ( $I_{on}/I_{off}$ ) was improved for a given target  $I_{on}$ , and the gate leakage current was appropriately suppressed. Comparing the process-of-record device against the 28 nm LP HK/MG device, the thickness of the electrical oxide layer in the new device was reduced by 3.1% in the case of n-type field effect transistors and by 10% for p-type field effect transistors. In addition, the reliability (e.g., bias temperature instability, hot carrier injury, and time-dependent dielectric breakdown) of the new device was evaluated, and it was observed that there was no conspicuous risk. Therefore, the HfSiO film can afford reliable performance enhancement when employed in the 28 nm LP HK/MG device with a limited thermal budget.

Keywords: high-k/metal-gate; HfSiON; HfSiO; gate-stack engineering

## 1. Introduction

To meet the needs of a hyper-connected society, the need for various types of integrated circuit (IC) chips has dramatically increased. Although fin-shaped field-effect transistors (FinFETs) have been widely adopted in low-power/high-performance IC chips over the last a few decades, they are still not very cost-effective for some applications. If a technique for dramatically improving the performance of planar bulk transistors in legacy technology (e.g., 28 nm technology) can be developed, it would potentially replace cutting-edge FinFET devices.

To improve the performance of 28 nm gate-first high-k/metal-gate (HK/MG) devices, it is essential to optimize the quality of high-k films. In terms of thermal budget, the quality of HfSiON films is known to be better than that of HfSiO congeners [1–6]. For this reason, HfSiON is generally preferred because the gate stack in the gate-first process is more likely to be exposed to heat and/or stress. Nitride in HfSiON is known to prevent crystallization, as well as to improve the film properties. However, studies have shown that it also has a negative impact, e.g., mobility degradation due to nitrides [7]. If HfSiO film can be optimized to minimize the mobility degradation as well as to ensure reliability, better device performance can be achieved. Atomic layer deposition (ALD) is widely used for HfSiO deposition, and it can ensure a better film quality in a hydrophilic environment [8–10].

The gate leakage current is a critical factor that directly impacts performance characteristics [11]. As shown in [12], efforts to suppress leakage current even in the latest transistor structures have been continuously studied. TiN engineering (e.g., by controlling

**Citation:** Park, J.; Jang, W.; Shin, C. Gate-Stack Engineering to Improve the Performance of 28 nm Low-Power High-K/Metal-Gate Device. *Micromachines* **2021**, *12*, 886. https:// doi.org/10.3390/mi12080886

Academic Editor: Enxia Zhang

Received: 26 June 2021 Accepted: 26 July 2021 Published: 27 July 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

the thickness of TiN) was carried out to suppress the gate leakage current. However, the unstable membranes of the thin TiN layer would be likely to increase the gate leakage current, and, thus, a thick TiN is thought to be a better choice in preventing the formation of interfacial traps, such as oxygen void diffusion and boron penetration [13]. In particular, it improves the threshold voltage ( $V_{\text{th}}$ ) distribution of p-type field-effect transistors (PFETs), and it is known to effectively improve the reliability, such as the bias temperature instability (BTI) [14].

#### 2. Materials and Methods

In this study, a metal oxide semiconductor (MOS) structure was fabricated to develop a gate-first high-k/metal-gate 28 nm LP transistor on an epitaxial Si (100) wafer. In the case of the process-of-record (POR) MOS structure, SiO<sub>2</sub>/HfSiON/TiN was used as an interlayer (IL), high-k material, and metal-gate, respectively, and they were deposited in order. For the newly proposed fabrication process, the interlayer (IL) of SiO<sub>2</sub> was used, and, then, cleaning steps for scaling down the IL layer were added to maximize the device performance. IL scaling also aims to create a hydrophilic environment for the ALD process. However, excessive IL scaling affects the reliability of oxide film quality and cannot be performed in large quantities. As the IL layer was very thin, the physical measurement was hard to use, and, thus, an electrical measurement was used to monitor the IL layer thickness. When depositing HfSiO instead of HfSiON, ALD was used. This was conducted with the intention of avoiding the degradation effect of nitride. Additionally, the TiN thickness was increased by 15% in the developed recipe to suppress the gate leakage current. This was to compensate for leakage caused by the decreased IL layer. Afterwards, gate etching, spacer formation, source/drain implantation, spike annealing, and silicide processes were carried out in both fabrication procedures. Figure 1 summarizes the process flow charts.

| þ | STI formation                | ¢ | STI formation                         |

|---|------------------------------|---|---------------------------------------|

| ¢ | IL Deposition                | ¢ | IL Deposition + IL scaling            |

| Q | High-k Deposition (HfSiON)   | ¢ | High-k Deposition (HfSiO)             |

| ¢ | TiN Deposition               | Q | TiN Deposition (thickness adjustment) |

| Q | Gate etch and spacer process | Q | Gate etch and spacer process          |

| Q | S/D implant and Spike Anneal | Q | S/D implant and Spike Anneal          |

| ¢ | Silicide and BEOL process    | ¢ | Silicide and BEOL process             |

| - | (a)                          |   | (b)                                   |

**Figure 1.** Fabrication process flow of (**a**) process-of-record (POR) and (**b**) the one proposed in this study.

The performance improvement was confirmed by comparing the value of  $I_{on}/I_{off}$  against the gate leakage current and electrical oxide thickness (EOT or  $T_{ox}$ ).  $T_{ox}$  was quantitatively estimated based on the measured capacitance in the inversion mode of MOS device. The capacitance characteristics can be inferred from the changes in EOT. Note that the gate leakage current indicates the gate current under  $V_{GS} = V_{DD}$  (=1 V in this study) and  $V_{DS} = 0$  V, for the n-type field-effect transistor (NFET).  $I_{on}$  is the measured current under  $V_G = V_D = V_{DD}$  (=1 V in this study), and  $I_{off}$  is the measured leakage current under  $V_G = 0$  V and  $V_D = V_{DD}$  (=1 V in this study). All electrical data were measured at room temperature. All samples were analyzed under the same conditions. The test pattern used for verification was designed with a 28 nm gate length, and the ratio of n-type MOSFET's gate width to p-type's one, i.e.,  $W_{n-type}$ : $W_{p-type} = 1:1.4$ . The gate leakage current and  $T_{ox}$  were measured in a large-scale pattern to better analyze the interfacial properties. Note

that thirteen samples per group were used for evaluation. The geometrical parameters of device structure used in this work are summarized in Table 1.

Table 1. Geometrical parameters of device structure.

| Parameters               | NFETs               | PFETs               |

|--------------------------|---------------------|---------------------|

| Gate length              | 28 nm               | 28 nm               |

| Gate width (normalized)  | 1x                  | 1.4x                |

| Gate length(large-scale) | $\geq 1 \text{ um}$ | $\geq 1$ um         |

| Gate width (large-scale) | $\geq 1 \text{ um}$ | $\geq 1 \text{ um}$ |

| Tox                      | $\leq 2 \text{ nm}$ | $\leq 2 \text{ nm}$ |

#### 3. Results and Discussion

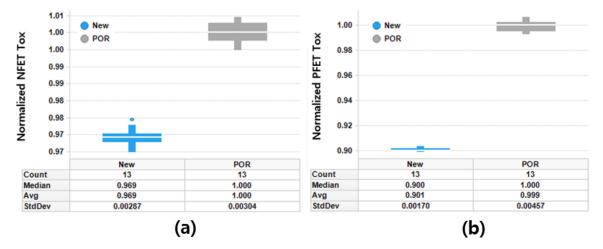

The thickness of the IL layer in the process-of-record (POR) samples is different from that in the newly fabricated samples because of the scaling down of the IL layer in the new samples. Thus, the electrical oxide thickness was measured for comparative purposes. With the newly proposed fabrication process, the gate leakage of MOSFET was well suppressed. Compared to the POR device, the electrical oxide thickness in the new device was reduced by 3.1% for the n-type field-effect transistor (NFET) and 10% for the PFET (see Figure 2). It is clear that the thinner the gate oxide, the better the device performance of MOSFET. However, the limit for reducing the physical oxide thickness should be set/determined by reliability requirements. The reliability of the samples fabricated by the newly proposed process flow was evaluated in terms of hot-carrier injection (HCI), bias temperature instability (BTI), and time-dependent dielectric breakdown (TDDB). The measured results are summarized in Figure 3.

**Figure 2.** Normalized electrical oxide thickness of (**a**) n-type field-effect transistor (NFET) and (**b**) p-type field-effect transistor (PFET).

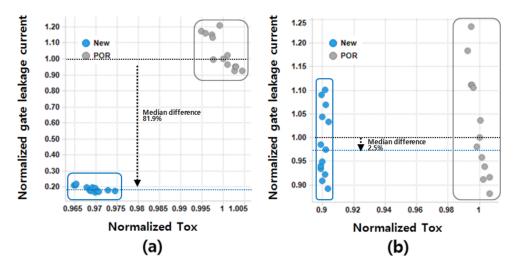

Figure 4 shows the plot of the normalized gate-on-leakage vs. the electrical oxide thickness for the NFET and PFET. The gate leakage current was suppressed by 81.9% for the NFET and 2.5% for the PFET. Note that the gate leakage current was measured in a long-channel MOSFET to avoid short channel effects. The purpose of this was to minimize the impact of the test pattern on leakage current so that the leakage of the film could be accurately measured. Direct numerical comparison of items with different thicknesses is not possible. However, it is noteworthy that the leakage current decreased in spite of the decrease in  $T_{ox}$ . In the case of the NFET (see Figure 4a), the fact that the gate leakage current was not increased (even though  $T_{ox}$  was decreased) is attributed to the change in the threshold voltage ( $V_{th}$ ) of the NFET as well as to the increase in the thickness of TiN. Increasing the TiN content has several advantages. In reality, as reported in [13,14], increasing the TiN content can be effective to block boron penetration, thereby reducing

interface defects and resistance. It is known that the degree of  $V_{th}$  distribution decreases as the boron penetration decreases (which may be beneficial). The NFET and PFET show different trends because of the fluctuations in  $V_{fb}$  and  $V_{th}$  owing to the change in the thickness of TiN. In addition, the effect of the presence or absence of high-k nitride on the channel is considered to be the key factor in determining the difference between the NFETs and PFETs [15–17]. The use of HfSiO as the HK film material, as well as the increase in TiN thickness, also contributes to suppressing leakage. As mentioned in [3], HfSiO is advantageous for suppressing leakage because it has a higher bandgap than that of HfSiON. HfSiON, which is currently in use, has a relatively low bandgap but is used because it was judged to be sufficient for operation. An additional benefit of leakage reduction can be achieved by using HfSiO as the HK material.

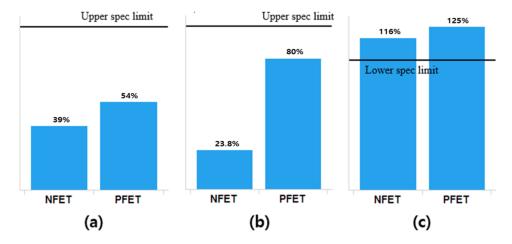

**Figure 3.** Reliability test result: (**a**) hot-carrier injection (HCI), (**b**) bias temperature instability (BTI), and (**c**) time-dependent dielectric breakdown (TDDB).

**Figure 4.** Normalized gate leakage current vs. normalized electrical oxide thickness for (**a**) NFET and (**b**) PFET.

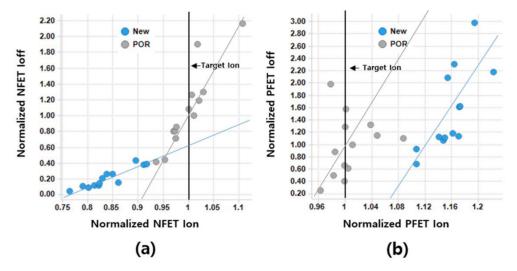

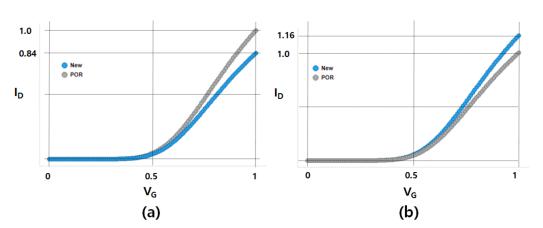

As shown in Figure 5, the comparison of the on/off current ratio  $(I_{on}/I_{off})$  of the POR device against that of the new device (which is fabricated by the newly proposed method) shows that, for the NFET,  $I_{on}$  of the new device (vs. that of the POR device) is decreased by 17.6%, but  $I_{off}$  is decreased by 85.5%. The improvement in  $I_{on}/I_{off}$  is confirmed more clearly in the NFET than in the PFET. It is noteworthy that  $I_{on}/I_{off}$  largely differs between the two devices. As the slope of the  $I_{on}$  vs.  $I_{off}$  plot is lower for the new device (see Figure 5a), it follows that  $I_{off}$  of the new device is less increased for a given improvement of  $I_{on}$ . Even if

$I_{on}$  of the new device is enhanced to the level of the POR device's, the  $I_{off}$  of the new device is expected to be approximately 40% lower than that of the POR device. The slope of the  $I_{on}$ vs.  $I_{off}$  plot for the p-type POR device is almost identical to that for the new p-type device. It is noteworthy that the on/off current ratios for the PFET device are largely comparable to each other. For the PFETs, the  $I_{on}$  of the new device (vs. POR device) is increased by 16%, and  $I_{off}$  is also increased by 18%. Table 2 summarizes the normalized  $I_{on}$ ,  $I_{off}$ , and  $I_{on}/I_{off}$  of NFETs and PFETs. Although  $I_{on}/I_{off}$  for PFETs seems to have decreased, it can be considered as an equivalent level within one sigma variation. Note that the PFET's one sigma of  $I_{on}/I_{off}$  is 0.35. Figure 6 shows the measured input transfer characteristics. Note that the PFET (vs. the POR device) achieves a higher current for a given gate voltage, but the NFET (vs. the POR device) shows a lower current for a given gate voltage.

Figure 5. Normalized *I*on vs. normalized *I*off of (a) NFET and (b) PFET.

| Table 2. Normalized value for | the new d | levice. |

|-------------------------------|-----------|---------|

|-------------------------------|-----------|---------|

| <b>Device Parameters</b> | NFETs | PFETs |

|--------------------------|-------|-------|

| Normalized <i>I</i> on   | 0.824 | 1.16  |

| Normalized <i>I</i> off  | 0.145 | 1.18  |

| Normalized Ion/Ioff      | 5.68  | 0.98  |

Figure 6. Measured input transfer characteristics of (a) NFET and (b) PFET.

Compared to the POR fabrication method, the enhanced device performance achieved with the new fabrication method can be judged to be the main reason for the gain by considering the mobility, as discussed in [7]. The better quality of the HfSiO film leads to

better  $I_{on}/I_{off}$  than that achieved with the HfSiON film if there is no problem with the risk from the heat budget covered in the previous study [18].

Reliability was evaluated at the wafer level, where three evaluations were conducted to prove the quality of the gate oxide and high-k film. The parameters determined include the bias temperature instability (BTI), hot-carrier injury/injection (HCI), and time-dependent dielectric breakdown. These methods are the well-known methods for reliability evaluation, as in [19–22]. All three evaluation results satisfied the specifications (see Figure 3). As summarized in Table 3, HCI was evaluated based on  $\Delta ids$ , BTI was based on  $\Delta V_{th}$ , and TDDB was based on  $V_{max}$ . Using accelerated evaluation (e.g., using a high temperature), all samples are evaluated under the condition that can confirm the lifetime of 10 years (see Table 3).  $\Delta ids$  in HCI evaluation and  $\Delta V_{th}$  in BTI evaluation are used to measure the lifetime of the device.  $\Delta V_{th}$  is selected based on the value converted from  $V_{max}$ . TDDB also evaluates the reliability of the gate oxide and whether the  $V_{max}$  state can be maintained normally. The reliability evaluation results prove that there is no problem with the heat budget.

Table 3. Detailed criteria for reliability test from JEDEC.

| Test Type | Criteria                                |

|-----------|-----------------------------------------|

| HCI       | $\Delta ids$ = 10%, 125 °C, AC 10 years |

| BTI       | 125 °C, AC 10 years                     |

| TDDB      | 125 °C, AC 10 years                     |

### 4. Conclusions

A technique to enhance the on/off current ratio of a 28 nm transistor was proposed and developed. The proposed technique can improve  $I_{on}/I_{off}$  while keeping the gate leakage current small by adjusting the thickness of TiN. Furthermore, it can enhance the gate-to-channel controllability by lowering the IL. Moreover, it can eliminate the disadvantages of nitride use in the process of using HfSiON as a high-k film. The results of this study prove that the transistor using the HfSiO layer as a high-quality high-k film can afford better  $I_{on}/I_{off}$  performance than that achieved with the HfSiON film under the limits of maintaining wafer-scale reliability. Further research on how to increase  $I_{on}/I_{off}$  in PFETs, as well as modifying  $V_{th}$  by adjusting the test pattern size, additional simulations or experiments with various sizes of transistors are required under the improved film quality conditions.

**Author Contributions:** Conceptualization, J.P. and W.J.; methodology, J.P. and W.J.; software, J.P.; validation, J.P., W.J. and C.S.; formal analysis, J.P. and C.S.; investigation, J.P. and W.J.; resources, J.P. and W.J.; data curation, J.P. and C.S.; writing—original draft preparation, J.P.; writing—review and editing, C.S.; visualization, J.P.; supervision, C.S.; project administration, C.S.; funding acquisition, J.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the National Research Foundation of Korea (NRF) through a grant funded by the Korean Government (MSIP) (No. 2020R1A2C1009063).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Koyama, M.; Satake, H.; Koike, M.; Ino, T.; Suzuki, M.; Iijima, R.; Kamimuta, Y.; Takashima, A.; Hongo, C.; Nishiyama, A. Degradation mechanism of HfSiON gate insulator and effect of nitrogen composition on the statistical distribution of the breakdown. In Proceedings of the International Electron Devices Meeting (IEEE) 2003, Washington, DC, USA, 8–10 December 2003.

- Koyama, M.; Kaneko, A.; Ino, T.; Koike, M.; Kamata, Y.; Iijima, R.; Kamimuta, Y.; Takashima, A.; Suzuki, M.; Hongo, C.; et al. Effects of nitrogen in HfSiON gate dielectric on the electrical and thermal characteristics. In Proceedings of the International Electron Devices Meeting (IEEE) 2002, San Francisco, CA, USA, 8–11 December 2002; pp. 849–852.

- 3. Sayan, S.; Nguyen, N.V.; Ehrstein, J.; Chambers, J.J.; Visokay, M.R.; Quevedo-Lopez, M.A.; Colombo, L.; Yoder, D.; Levin, I.; Fischer, D.A.; et al. Effect of nitrogen on band alignment in HfSiON gate dielectrics. *Appl. Phys. Lett.* 2005, *87*, 212905. [CrossRef]

- 4. Yang, X.M.; Wu, X.M.; Yu, T. Improvement of thermal stability and electrical performance in HfSiO gate dielectrics by nitrogen incorporation. *Phys. E Low Dimens. Syst. Nanostruct.* **2011**, *44*, 361–366. [CrossRef]

- 5. Sato, M.; Aoyama, T.; Sekine, K.; Yamaguchi, T.; Hirano, I.; Eguchi, K.; Tsunashima, Y. Effects of nitrogen concentration and post-treatment on reliability of HfSiON gate dielectrics in inversion states. *Jpn. J. Appl. Phys.* **2006**, *45*, 2949. [CrossRef]

- 6. Naito, T.; Tamura, C.; Inumiya, S.; Hasunuma, R.; Yamabe, K. Homogeneity improvements in the dielectric characteristics of HfSiON films by nitridation. *Jpn. J. Appl. Phys.* **2007**, *46*, 3197. [CrossRef]

- Garros, X.; Casse, M.; Reimbold, G.; Martin, F.; Leroux, C.; Fanton, A.; Renault, O.; Cosnier, V.; Boulanger, F. Guidelines to improve mobility performances and BTI reliability of advanced High-K/Metal gate stacks. In Proceedings of the 2008 Symposium on VLSI Technology (IEEE), Honolulu, HI, USA, 17–19 June 2008; pp. 68–69.

- 8. Kim, H.; Lee, H.-B.-R.; Maeng, W.-J. Applications of atomic layer deposition to nanofabrication and emerging nanodevices. *Thin Solid Film* **2009**, *517*, 2563–2580. [CrossRef]

- Morita, Y.; Hirano, A.; Migita, S.; Ota, H.; Nabatame, T.; Toriumi, A. Impact of surface hydrophilicization prior to atomic layer deposition for HfO2/Si direct-contact gate stacks. *Appl. Phys. Express* 2008, 2, 011201. [CrossRef]

- 10. Kirsch, P.D.; Quevedo-Lopez, M.; Krishnan, S.; Song, S.-C.; Choi, R.; Majhi, P.; Senzaki, Y.; Bersuker, G.; Lee, B.H. Atomic layer deposited HfO2 and HfSiO to enable CMOS gate dielectric scaling, mobility, and VTH stability. *ECS Trans.* 2006, 1, 15. [CrossRef]

- 11. Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits. *Proc. IEEE* 2003, *91*, 305–327. [CrossRef]

- 12. Bousari, N.B.; Anvarifard, M.K.; Haji-Nasiri, S. Improving the electrical characteristics of nanoscale triple-gate junctionless FinFET using gate oxide engineering. *AEU Int. J. Electron. Commun.* **2019**, *108*, 226–234. [CrossRef]

- 13. Bae, S.H.; Song, S.C.; Choi, K.; Bersuker, G.; Brown, G.A.; Kwong, D.L.; Lee, B.H. Thickness optimization of the TiN metal gate with polysilicon-capping layer on Hf-based high-k dielectric. *Microelectron. Eng.* **2006**, *83*, 460–462. [CrossRef]

- 14. Chen, C.L.; King, Y.C. TiN metal gate electrode thickness effect on BTI and dielectric breakdown in HfSiON-based MOSFETs. *IEEE Trans. Electron Devices* **2011**, *58*, 3736–3742. [CrossRef]

- 15. Kadoshima, M.; Matsuki, T.; Miyazaki, S.; Shiraishi, K.; Chikyo, T.; Yamada, K.; Aoyama, T.; Nara, Y.; Ohji, Y. Effective-workfunction control by varying the TiN thickness in Poly-Si/TiN gate electrodes for scaled high-*k* CMOSFETs. *IEEE Electron Device Lett.* **2009**, *30*, 466–468. [CrossRef]

- 16. Lee, S.H.; Choi, R.; Choi, C. Effects of composition and thickness of TiN metal gate on the equivalent oxide thickness and flat-band voltage in metal oxide semiconductor devices. *Microelectron. Eng.* **2013**, *109*, 160–162. [CrossRef]

- Rotondaro, A.; Visokay, M.; Chambers, J.; Shanware, A.; Khamankar, R.; Bu, H.; Laaksonen, R.; Tsung, L.; Douglas, M.; Kuan, R.; et al. Advanced CMOS transistors with a novel HfSiON gate dielectric. In Proceedings of the 2002 Symposium on VLSI Technology. Digest of Technical Papers (IEEE) (Cat. No. 01CH37303), Honolulu, HI, USA, 11–13 June 2002; pp. 148–149.

- 18. Khan, Z.N.; Ahmed, S.; Ali, M. Effect of thermal budget on the electrical characterization of atomic layer deposited HfSiO/TiN gate stack MOSCAP structure. *PLoS ONE* **2016**, *11*, e0161736. [CrossRef] [PubMed]

- Lee, K.T.; Nam, J.; Jin, M.; Bae, K.; Park, J.; Hwang, L.; Kim, J.; Kim, H.; Park, J. Frequency dependent TDDB behaviors and its reliability qualification in 32nm high-k/metal gate CMOSFETs. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. 2A. 3.1–2A. 3.5.

- Nigam, T.; Parameshwaran, B.; Krause, G. Accurate product lifetime predictions based on device-level measurements. In Proceedings of the 2009 IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 634–639.

- Li, X.; Qin, J.; Bernstein, J.B. Compact modeling of MOSFET wearout mechanisms for circuit-reliability simulation. *IEEE Trans. Device Mater. Reliab.* 2008, *8*, 98–121. [CrossRef]

- Park, M.-C.; Yang, G.-Y.; Yang, J.-S.; Lee, K.-H.; Park, Y.-K. New perspective on lifetime prediction approach for BTI and HCI stressed device and its impact on circuit lifetime. In Proceedings of the 2014 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Yokohama, Japan, 9–11 September 2014; pp. 337–340.