# **ARTICLE**

Received 1 Oct 2015 | Accepted 2 Feb 2016 | Published 10 Mar 2016

DOI: 10.1038/ncomms10908

OPEN

1

# Mobility overestimation due to gated contacts in organic field-effect transistors

Emily G. Bittle<sup>1,2</sup>, James I. Basham<sup>1,3</sup>, Thomas N. Jackson<sup>3</sup>, Oana D. Jurchescu<sup>2</sup> & David J. Gundlach<sup>1</sup>

Parameters used to describe the electrical properties of organic field-effect transistors, such as mobility and threshold voltage, are commonly extracted from measured current-voltage characteristics and interpreted by using the classical metal oxide-semiconductor field-effect transistor model. However, in recent reports of devices with ultra-high mobility ( $>40\,\mathrm{cm^2\,V^{-1}\,s^{-1}}$ ), the device characteristics deviate from this idealized model and show an abrupt turn-on in the drain current when measured as a function of gate voltage. In order to investigate this phenomenon, here we report on single crystal rubrene transistors intentionally fabricated to exhibit an abrupt turn-on. We disentangle the channel properties from the contact resistance by using impedance spectroscopy and show that the current in such devices is governed by a gate bias dependence of the contact resistance. As a result, extracted mobility values from d.c. current-voltage characterization are overestimated by one order of magnitude or more.

<sup>&</sup>lt;sup>1</sup> National Institute of Standards and Technology, Engineering Physics Division, 100 Bureau Drive, MS 8120, Gaithersburg, Maryland 20899, USA. <sup>2</sup> Department of Physics, Wake Forest University, 1834 Wake Forest Road, Winston-Salem, North Carolina 27109, USA. <sup>3</sup> Department of Electrical Engineering, The Pennsylvania State University, 121 Electrical Engineering East, University Park, State College, Pennsylvania 16802, USA. Correspondence and requests for materials should be addressed to E.G.B. (email: emily.bittle@nist.gov) or to D.J.G. (email: david.gundlach@nist.gov).

rganic semiconductors (OSCs) remain a topic of considerable interest for basic and applied research. As such, accurate electrical characterization and parameterization of physical properties which govern the device operation of light emitting diodes, field-effect transistors and photovoltaic cells is essential for continued device performance improvement and possible commercialization of organic semiconductor-based devices. Charge carrier mobility is one of several commonly cited physical properties, and describes charge motion under applied electric field. The organic field-effect transistor (OFET) is routinely used as a test structure for extracting mobility in addition to being a key element in circuits. The most commonly used method to evaluate OFET parameters such as field-effect mobility,  $\mu$ , and threshold voltage,  $V_{\rm th}$ , is the classical metaloxide-semiconductor field-effect transistor (MOSFET) model. This model is described for the two extreme modes of operation above threshold,  $|V_{GS}| > V_{th}|$ , in equations (1) and (2). For linear mode,  $|V_{\rm DS}| < |V_{\rm GS} - V_{\rm th}|$ ,

$$I_{\rm D} = \mu_{\rm lin} c_{\rm ox} \frac{W}{L} \left[ (V_{\rm GS} - V_{\rm th}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right], \tag{1}$$

and for saturation mode  $|V_{\rm DS}| > |V_{\rm GS} - V_{\rm th}|$ ,

$$I_{\rm D} = \mu_{\rm sat} c_{\rm ox} \frac{W}{2L} (V_{\rm GS} - V_{\rm th})^2, \tag{2}$$

where  $V_{\rm GS}$  is the gate voltage,  $V_{\rm th}$  is the threshold voltage,  $I_{\rm D}$  is the drain current,  $V_{\rm DS}$  is the drain voltage,  $\mu_{\rm lin}$  and  $\mu_{\rm sat}$  are the linear and saturation mobility, respectively, W and L are the width and length of the transistor channel and  $c_{\rm ox}$  is the oxide capacitance per unit area. In this paper, we illustrate how this model describing the device behaviour for idealized materials and interfaces that adhere to solid-state band theory can lead to severe inaccuracies in extracted parametric values when used to analyse non-ideal transistors.

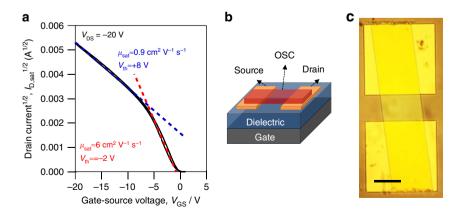

We focus on a particular non-ideality in OFET transistor characteristics, shown in Fig. 1a, which appears in many high-mobility single-crystal FETs<sup>1-3</sup>, polymer<sup>4-10</sup> and small molecule thin film transistors<sup>11,12</sup>. In this non-ideal case,  $I_{\rm D}$  shows an abrupt change in slope as a function of  $V_{\rm GS}$ , whereas in the classical model  $I_{\rm D}$  ( $I_{\rm D}^{1/2}$ ) is linear with  $V_{\rm GS}$  in the linear (saturation) regime as defined in equations (1) and (2). This slope is regularly used to calculate mobility and extrapolate the threshold voltage. As reports of transistors with this non-ideal behaviour become more prevalent in the literature, yielding impressive mobility values, a detailed understanding of the source

of the non-ideal behaviour and its impact on extracted figures of merit has become important. Here, we fabricate a transistor to exhibit non-ideal  $I_{\rm D}-V_{\rm GS}$  characteristics and use impedance spectroscopy to disentangle the contact behaviour from the transistor channel behaviour to directly compare these measurements to d.c. I–V measurements made on the same OFET device. This comparison clarifies the impact that a non-ohmic contact can have on transistor behaviour, and by extension, on the mobility extracted from the I–V data. We show that the mobility can be overestimated by up to one order of magnitude in transistors with pronounced non-ideal current-voltage characteristics, an effect which arises from the gate-bias dependence of the contact resistance.

#### Results

Material and electrical considerations. For this study, we characterized the electrical properties of single-crystal rubrene fieldeffect transistors fabricated in a bottom contact, bottom gate geometry (Fig. 1b). The bottom-contact geometry simplifies the electric field distribution and the parasitic gate to source/drain overlap capacitance, and eliminates charge transport in the outof-plane direction in the OSC. Rubrene was chosen because its single crystals have been shown to exhibit nearly ideal transistor behaviour and are useful for fundamental studies<sup>13</sup>. Small molecule single crystals have lower molecular disorder and more straightforward transport pathways than polymer thin films, which involve a convolution of pi-pi and backbone transport. Furthermore, single crystals do not suffer from pronounced grain boundaries that can lead to large potential drops in the channel as in the case of polycrystalline thin films of small molecule semiconductors <sup>14,15</sup>. A micrograph of a completed field-effect transistor device is shown in Fig. 1c.

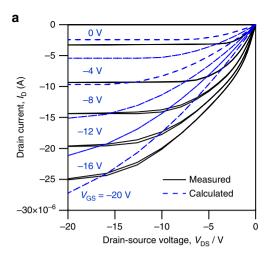

Current-voltage characterization. The d.c.  $I_{\rm D}-V_{\rm GS}$  characteristics for a device biased in the saturation regime with  $V_{\rm DS}=-20\,\rm V$  are plotted in Fig. 1a. For both saturation ( $|V_{\rm DS}|>|V_{\rm GS}-V_{\rm th}|$ ) and linear ( $|V_{\rm DS}|<|V_{\rm GS}-V_{\rm th}|$ ) regimes, the current-voltage characteristics change from high slope to low slope as the gate bias is increased from 0 V. The kink where the slope change happens, around  $-6\,\rm V$  in the saturation characteristics, allows us to define two regions: one at small gate bias  $(0>V_{\rm GS}>-6\,\rm V)$  with high slope and another at large gate bias  $(-20\,\rm V< V_{\rm GS}<-7\,\rm V)$  with low slope. This behaviour deviates from the ideal FET behaviour given by equations (1) and (2),

Figure 1 | Current-voltage characteristics for a non-ideal transistor and transistor geometry. (a) Plot of the transfer characteristics in the saturation regime ( $V_{DS} = -20 \text{ V}$ ) of a rubrene transistor exhibiting non-ideal characteristics. Fit lines in red and blue illustrate the ambiguity associated with characterizing OFETs. (b) Bottom gate/bottom contact OFET. (c) Image of transistor. Drain and source contact pairs are  $250 \times 250 \,\mu\text{m}$  squares and the rubrene active area is  $140 \,\mu\text{m}$  wide  $\times 100 \,\mu\text{m}$  long. Scale bar is  $100 \,\mu\text{m}$ .

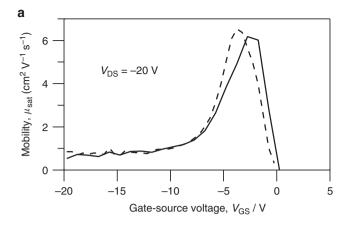

**Figure 2 | Overestimation of the mobility.** 'Mobility', as defined in equations (1) and (2), are plotted in the saturation (**a**) and linear (**b**) regimes as a function of gate bias, increasing bias direction in solid lines and reverse in dashed lines. Similar results were found for 30 transistors measured during the course of this study.

where the slope is constant with  $V_{\rm GS}$  ( $I_{\rm D} \propto V_{\rm GS}$  in the linear regime and  $I_{\rm D}^{1/2} \propto V_{\rm GS}$  in the saturation regime.) The slope and intercept of linear fits to the  $I{-}V$  data provide an aggregate mobility and threshold voltage values when evaluated in the MOSFET model. In the saturation regime, these fits yield mobility of  $6\,{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$  and threshold voltage of  $-2\,{\rm V}$  at low gate bias, and  $0.9\,{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$  and  $8\,{\rm V}$  at high gate bias. The extracted mobility differs by  $\sim\!6\,\times$  and  $V_{\rm th}$  differs by  $10\,{\rm V}$ .

Mobility as a function of gate voltage was extracted using the MOSFET model for the saturation ( $V_{\rm DS}=-20\,\rm V$ ) and linear ( $V_{\rm DS}=-0.1\,\rm V$ ) regimes and is plotted in Fig. 2a,b. The differential mobility values extracted from the MOSFET model are nearly constant for  $-20\,\rm V < V_{\rm GS} < -10\,\rm V$ , but increase to a peak at  $V_{\rm GS}\approx-5\,\rm V$ . Hysteresis, likely due to modest charge trapping in the transistor channel, is small. Forward and reverse sweeps show a comparable variation of the mobility with gate bias. The linear and saturation regime mobilities have similar magnitude and variation with gate bias, which creates ambiguity about the intrinsic transistor channel mobility.

In several devices we fabricated using nominally the same processing method the discrepancy in the mobility was as large as  $14 \times$ . We have included two examples in Supplementary Fig. 1. For contrast, we have also included a sample prepared on platinum contacts, which shows nearly ideal behaviour in Supplementary Fig. 2. We have reexamined data from several references  $^{1,3,5-7,9-11,16}$  with a similar discrepancy between the high and low gate bias regions by applying equations (1) and (2)

**Figure 3 | Prevalence of overestimation of the mobility.** Our estimates of peak mobility,  $\mu_{\rm peak}$ , at low gate bias and aggregate mobility,  $\mu_{\rm agg}$ , calculated for higher gate bias using the MOSFET equations applied to hand fits of published data<sup>1,3,5–7,9–11,16</sup>. We also include our data from Fig. 1a and the Supplementary Figs (SI) 1b, 1d and 2. Polymers are given by filled symbols and small molecules are given by open symbols. Selected papers show a change from high to low slope in the transconductance data as gate bias is increased in either the saturation or linear regime for p-type conduction. Lines are guides to the eye, and show the ratio of peak to high gate bias values.

to our estimates from the slopes of published I-V characteristics. The comparison plotted in Fig. 3 show that for most of the data examined, the peak mobility is  $\sim 3 \times$  to  $5 \times$  of the aggregate mobility calculated at high gate bias; with largest disparity being  $18 \times$ . It is important to note that the mobility values calculated using the MOSFET model are scalar fit parameters and not intrinsic material parameters. We made an effort in our literature search to include data on polymers, small molecules, as well as semiconductors with different band gaps, but have found no correlation between this behaviour and material type.

Explanations for this non-ideal behaviour vary in the literature. Some have proposed that at low gate bias, the accumulation layer is not tightly confined to the interface and extends into the bulk where there is less effect of the disorder associated with the OSC/dielectric interface. At higher gate bias, the charges become confined to the interface at high gate fields and mobility decreases due to the increased disorder<sup>1</sup>, charges become trapped in the gate dielectric at high field<sup>17</sup> or that the high carrier density causes Coulombic interactions between the charges 18. Other reports have proposed that a high contact resistance restricts current at high gate bias when the channel and contact resistance become comparable<sup>19</sup>. However, this latter interpretation is not consistent with observations by several other groups who report a decrease in contact resistance with increasing gate bias<sup>20,21</sup>. Researchers studying ambipolar operation have speculated that this effect could be due to negative trap filling in low band gap materials<sup>16</sup>, which we discuss below.

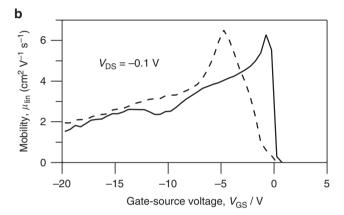

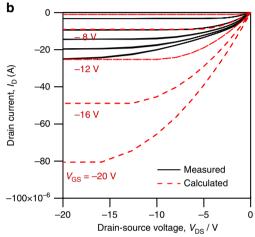

To further analyse our results in the context of the MOSFET model, we use the aggregate mobility and  $V_{\rm th}$  shown in Fig. 1a for the two distinct regions to calculate the  $I_{\rm D}$  versus  $V_{\rm DS}$  at various  $V_{\rm GS}$  by using equations (1) and (2). The calculated values for  $I_{\rm D}$

**Figure 4 | A comparison of mobility estimation results.** Measured  $I_D$  versus  $V_{DS}$  plots compared with plots calculated from equations (1) and (2) using extracted mobility and  $V_{th}$  obtained from the fitting lines to the measured data in Fig. 1a for the device biased in saturation in the two distinct regions; (a) high gate bias and (b) low gate bias.

$(V_{\rm DS},\,V_{\rm GS})$  are plotted in Fig. 4a,b and reveal that the classical MOSFET relationship describing  $I_{\rm D}$   $(V_{\rm DS})$  provides a poor fit when compared with the measured characteristics. The best agreement to the measured data is obtained by using the aggregate mobility  $(\mu_{\rm sat}\!=\!0.9\,{\rm cm^2\,V^{-1}\,s^{-1}})$  and corresponding threshold voltage  $(V_{\rm th}\!=\!+\,8\,{\rm V})$  extracted for high gate bias.

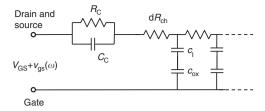

Impedance analysis. We have used impedance spectroscopy to characterize and extricate the components of the transistor for the linear regime (measured at  $V_{\rm DS}=0\,\rm V$ ) to clarify what governs device operation in the different gate bias ranges,  $V_{\rm GS}$ . The impedance data were analysed by using a combination of a transmission line to model the transistor channel and a parallel RC circuit to model the contacts ( $R_{\rm C}$  and  $C_{\rm C}$ ),

$$Z_{\rm T} = Z_{\rm dist} + Z_{\rm C},\tag{3}$$

$$Z_{\rm dist} = \frac{1}{j\omega W L c'} \lambda \coth \lambda, \ \lambda = \sqrt{\frac{1}{4} j\omega c' r L^2},$$

(4)

$$Z_{\rm C} = \frac{jR_{\rm C}}{j - \omega R_{\rm C} C_{\rm C}},\tag{5}$$

shown in Fig. 5 where  $Z_{\rm dist}$  is the transistor channel impedance and  $Z_{\rm C}$  is the contact impedance. The transistor channel was

**Figure 5 | Model of the transistor impedance.** Equivalent circuit used to model a.c. transistor behaviour.

divided into elements of length dx; resistance and capacitance per area,

$$dR_{\rm ch} = \frac{r}{W}dx,\tag{6}$$

$$c' = \frac{c_{\text{ox}}c_{\text{I}}}{c_{\text{ox}} + c_{\text{I}}},\tag{7}$$

where r is the sheet resistance and  $c_{\rm I}$  is the interfacial capacitance per area. Due to the experimental design, the contact resistance is frequency independent, whereas the distributed channel resistance is frequency dependent, and the two are easily separated. The transmission line model was shown by Hamadani  $et\ al.^{22}$  to be successful in the analysis of poly(3-hexylthiophene) transistors when  $Z_{\rm C}$  is included.

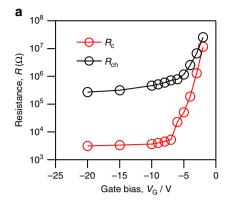

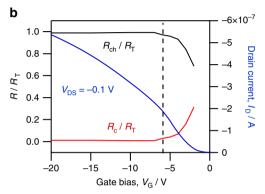

The channel and contact resistance were extracted for the reverse (negative to positive  $V_{GS}$ ) trace by fitting equation (3) to the impedance data and are plotted in Fig. 6a as a function of gate bias. Additional details about the impedance data modelling are included in the Supplementary Figs 3 and 4. The channel resistance varies as  $1/V_{\rm GS}$  over the entire bias range. This functional dependence is consistent with linear region MOSFET operation as given by equation (1). The contact resistance exhibits a pronounced gate bias dependence over a small bias range  $(0 \text{ V} > V_{GS} > -6 \text{ V})$ , where  $R_{C}$  decreases exponentially by a factor of  $\sim 5,000$  as the amplitude of  $V_{\rm G}$  increases. At high gate bias  $(-10 > V_{GS} > -20 \text{ V})$ , the contact resistance remains at a constant low value. This functional dependence of contact resistance with gate bias is most consistent with that of a gated Schottky contact, where a relatively abrupt transition from thermionic to thermionic-field emission and finally to field emission (tunnelling) results in an exponential decrease and plateau of the contact resistance. The charge accumulation in the channel provides the necessary conditions for the tunnelling injection process and is analogous to the formation of a highly doped contact region that greatly reduces that depletion region formed at the metal-semiconductor interface and allows for efficient injection.

Figure 6b provides a graphical comparison of  $I_{\rm D}(V_{\rm GS})$  biased in the linear regime at small  $V_{\rm DS}$  ( $V_{\rm DS}=-0.1\,\rm V$ ) to the channel and contact resistances as a fraction of total resistance ( $R_{\rm T}=R_{\rm ch}+R_{\rm C}$ ). This comparison best illustrates the influence of  $R_{\rm C}$  ( $V_{\rm GS}$ ) on I–V characteristics for this device. The large change in contact resistance at low gate bias correlates with high transconductance ( $g_{\rm m}=dI_{\rm D}/dV_{\rm GS}$ ) of the transistor I–V characteristics and with the peak in the differential mobility, Fig. 2b. At high gate bias,  $R_{\rm C}$  is low ( $\approx 10^3\,\Omega$ ) relative to the channel resistance ( $\approx 10^5\,\Omega$ ) and nearly constant. In this same bias regime, we observe nearly linear behaviour of  $I_{\rm D}(V_{\rm GS})$  and in the levelling of the differential mobility extracted from the I–V characteristics. We therefore conclude that the mobility peak at  $V_{\rm GS}\approx -5\,\rm V$  is a result of exponentially changing contact resistance relative to the more slowly changing channel resistance.

Electrical contact between metals and organic semiconductors has long been known to have a strong influence on the operation

**Figure 6 | Comparison of contact and channel resistance.** (a)  $R_{\rm C}$  and  $R_{\rm ch}$  values extracted from fits to impedance data using equation (3) for reverse (negative to positive  $V_{\rm GS}$ ) sweep in the linear regime. (b) Plot of the I-V characteristic (blue) for  $V_{\rm DS}=-0.1\,\rm V$  negative to positive sweep, along with plot of  $R_{\rm C}/R_{\rm T}$  and  $R_{\rm ch}/R_{\rm T}$ .

and extrinsic performance of organic electronic devices  $^{17,23-28}$ . OFET measurements of the contact resistance $^{26,28}$  and local potential  $^{14,29,30}$  show that the metal–organic semiconductor interface can be a significant source of potential drop at the injection contact and can be highly influential on I-V characteristics. In particular, transistor behaviour can be significantly impacted by charge injection from the metal electrode into the OFET channel due to the large current density ( $10^6$  times larger than for diodes, such as light-emitting diodes and photovoltaics.) Calculations of the effects of contact resistance on OFETs, modelled by using either a Schottky barrier or low-mobility areas at the contact, show that  $R_{\rm C}$  can be gatevoltage dependent, which significantly impacts the resulting current–voltage (I-V) characterization  $^{31}$ .

The effect of a gated source contact on FET operation has been previously observed and/or induced in devices based on a large number of materials. For example, poly and amorphous silicon and zinc oxide FETs with Schottky contacts (source gated transistors or Schottky source barrier transistors) have been engineered to take advantage of the high transconductance and low output conductance for specific circuit applications<sup>32–35</sup>. Precisely, how the contact affects operations depends on many factors. Carbon nanotube FETs and two-dimensional layered FETs are similar to organic FETs in that conventional doping of the contact region is challenging and Schottky contacts are routinely formed to the semiconductor<sup>36,37</sup>. Injection and transport studies on the former devices<sup>36,37</sup> report injection barriers that are typically less than 0.3 eV and a transition from thermionic to thermionic-field emission to field emission (tunnelling) with applied voltage that is less abrupt than we

report here for rubrene single-crystal FETs. We expect FETs with the pronounced dependence of transconductance on bias to result from a larger injection barrier and in devices where the magnitude of the channel resistance falls within the range of the exponentially decreasing contact resistance. High-mobility organic semiconductors with contacts having large injection barriers would appear to be prone to this specific effect. Similarly, such an effect might be present but not readily observed in low-mobility organic FETs because the transition would likely occur in the subthreshold region. At a minimum, a large injection barrier is expected in devices exhibiting ambipolar operation and confirms that contacts with large injection barriers are less selective than assumed<sup>6,7</sup>.

Ambipolar behaviour is often observed in low bandgap OSCs. The poor charge selectivity of contacts that facilitate ambipolar behaviour can, under the appropriate bias stress conditions, result in electron injection and trapping. It has recently been suggested<sup>16</sup> that electron trapping during bias conditions can contribute to non-ideal behaviour and give rise to over-estimation of the field effect mobility. The most likely mechanism being the current-voltage characteristics reflect non-equilibrium measurement conditions where the trapped charge is not neutralized by the injected counter charge. This permits the quasi Fermi level to move more quickly through the band gap and the current to increase more rapidly with increasing gate bias than under equilibrium conditions. Such charge trapping would only further enhance the gated contact-controlled transconductance that we report here for wide band gap organic semiconductors because of the resulting electrostatics, which inhibit compression of the depletion region at the Schottky barrier interface and efficient charge injection. The non-ideal behaviour reported for low band gap ambipolar FETs is consistent with both gated-Schottky contacts, further enhanced by electron trapping as well as measurements made under nonequilibrium conditions. A more detailed and careful study is required to disentangle such effects in these systems.

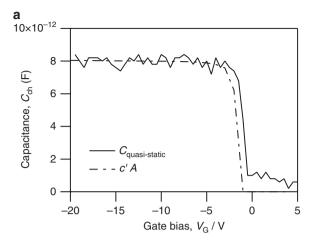

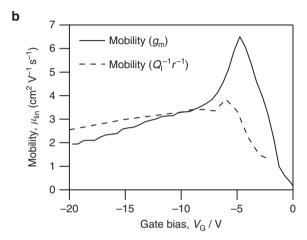

Although the transconductance of our transistor is dominated by the gate-activated R<sub>C</sub> for low gate bias, the impedance measurements gave us access to the channel behaviour in this region. We can use this to calculate the true mobility of the device channel above the apparent threshold voltage of the device, which corresponds with the sharp turn-on in channel capacitance seen in Fig. 7a. Channel mobility can be calculated from the accumulated charge in the transistor channel, Q<sub>I</sub>, and the sheet resistance, r, in the channel by using equation (8) and the results of impedance modelling<sup>38</sup>. The channel mobility calculated for low gate bias from the channel r and  $Q_I$  plotted in Fig. 7b shows that channel mobility increases slowly over this range to a constant value and does not show the pronounced peak as in the differential mobility extracted from device I-V characteristics analysed with the MOSFET model. This impedance-based analysis of the channel mobility further supports our conclusion that the apparent high mobility is due to the effect of the gate voltage dependence of R<sub>C</sub> on the total device transconductance and not to a variation of the transistor channel.

$$\mu = \frac{1}{Q_{\rm I}r}, Q_{\rm I} = \int_{-\infty}^{V} c' dV_{\rm GS} \approx \sum_{-\infty}^{V} c' \delta V_{\rm GS},$$

(8)

## **Discussion**

The importance of contacts has been widely acknowledged in organic electronic devices  $^{17,19,21,39}$ . There exists numerous studies using gated four-terminal measurements, gated transfer length measurements and scanned Kelvin probe microscopy, all of which attempt to measure  $R_{\rm C}$ , correct for the reduced  $V_{\rm DS}$  and

**Figure 7 | Determining the mobility.** (a) The capacitance in the channel (c'A, where A is the area of the transistor). (b) Mobility for the reverse (negative to positive  $V_{\text{GS}}$ ) sweep: the differential mobility (solid line) calculated from the linear transistor characteristics using equation (1) and mobility (dashed line) calculated from equation (8) using the channel properties obtained from the fit to impedance data.

$V_{\rm GS}$ , and extract 'intrinsic' channel mobility <sup>1,21,29</sup>. However, these approaches rely on the assumption that the measured dependence of drain current on gate voltage (transconductance) is controlled mainly by the channel properties, the channel potential as a function of position is accurately measured and the channel threshold voltage is given by the intercept of the fitting line. Furthermore, analytical expressions that model the extrinsic transistor d.c. I-V characteristics as a forward-biased diode in series with an ideal transistor do not accurately capture the physics governing device operation or the inherent twodimensional effects of the drain and gate fields. They often yield fits to data that agree only over a limited bias range. These approaches are best suited to devices with ohmic contacts (linear I-V characteristics) that can be modelled as a resistor in series with the transistor. Efforts have been made to improve the charge injection and extraction at the metal contact to OSCs in OFETs including the use of self-assembled monolayers or contact area doping of the semiconductor<sup>39–43</sup>. When characterizing new OSCs, contact optimization is often not addressed; this can lead to over- or under-estimates of their performance potential.

It is important to note that the method detailed here for device parameterization is not entirely exempt from contact effects. Accurate parameterization near the apparent threshold voltage remains problematic because charge injection still limits channel charging and channel resistance extraction at the lowest frequency range used in these measurements (20 Hz) and results in the apparent slow increase in channel mobility as shown in Fig. 7b. At longer charging timescales and at sweep rates comparable to I-V measurements, quasi-static capacitancevoltage measurements provide vet another route to characterizing channel accumulation. Plotted in Fig. 7a is the quasi-static capacitance taken at  $dV_{\rm GS}/dt=0.5~{\rm V~s}^{-1}$  and showing channel accumulation at  $V_{GS} \approx -1 \text{ V}$ . A small shift in channel accumulation is observed relative to the characteristics extracted by using impedance spectroscopy. Smaller voltage ramp rates are required to reveal larger shifts towards positive threshold voltage but present a significant measurement challenge. This calls into question the accuracy of other important parameters such as threshold voltage and subthreshold slope. These parameters, like mobility, are routinely used in benchmarking performance and to estimate interface trap density with the assumption that both are governed entirely by the channel interface properties.

We show here that by disentangling channel and contact impedance in working transistors, we gain a better understanding of the origin of non-ideal behaviour in the  $I_{\rm D}$ – $V_{\rm GS}$  characteristics of OFETs. Strongly varying contact resistance at low  $|V_{\rm GS}|$  results in transistor behaviour that is dominated by charge injection. This leads to an overestimation of the channel mobility by an order of magnitude when extracted using the MOSFET model and ambiguity in the transistor behaviour near the threshold. Analysis of the current–voltage data is not straightforward due to the variety of non-ideal contact and channel effects present in organic field-effect transistors. For accurate measurement of device parameters, such as mobility and subthreshold behaviour, more robust measurements and analysis must be developed along with contact engineering methods to improve charge injection at the metal–organic semiconductor interface.

#### Methods

**Sample preparation.** We used pre-fabricated transistor test structures consisting of a heavily doped silicon substrate (gate electrode, n-type  $10^{-3}\,\Omega$  cm), thermally grown silicon dioxide layer (gate dielectric,  $\approx 57\,\mathrm{nm}$ ) and photolithographically defined metal electrodes (source and drain contacts, 40 nm gold on 5 nm titanium). The completed transistors have channel lengths of  $50-100\,\mathrm{\mu m}$ . We used a self-assembled monolayer of octadecyltrichlorosilane (OTS) to improve the semiconductor adhesion and to create a hydrophobic surface on the SiO<sub>2</sub> to eliminate water<sup>3,15,44</sup>. This layer is assembled by immersing the prefabricated substrates overnight in 5 mmol  $1^{-1}$  OTS in hexadecane, followed by sonication for 5 min in each of the following solvents: chloroform, isopropyl alcohol and de-ionized water, and then heating the wafer to 150 °C for 10 min.

Rubrene single crystals were grown by physical vapour transport in a tube oven under argon flow and carefully laminated to the surface of the prefabricated substrates. The starting material was 99.99 % rubrene from Sigma-Aldrich and used as received. The transistors that we considered for this study were those where the rubrene crystal occupied the drain-source channel and the contacts pads only; this was done to ensure that the transistor was isolated and to remove parasitic impedance from charged rubrene outside of the transistor area, Fig. 1c.

**Electrical characterization.** I-V measurements were taken with an Agilent 4155C Semiconductor Parameter Analyzer. Impedance measurements were taken using an Agilent E4980 LCR meter by applying the high potential and current terminals to the gate and low potential and current terminals to the shorted drain and source. A d.c. bias voltage  $(V_{\rm GS})$  is applied to the gate along with a small a.c. signal  $(V_{\rm GS})$  ( $\omega$ ) = 0.025 V). At each d.c. bias point, the a.c. frequency  $f=\omega/2\pi$  is swept from 20 to 2 MHz. Quasi-static capacitance was measured with a Hewlett Packard 4140B pA Meter at  $dV_{\rm GS}/dt$  = 0.5 V s  $^{-1}$ . I-V, impedance and quasi-static capacitance measurements were taken successively in the dark at room temperature in an  $N_2$  gas environment. Computer interfacing was done using Instrument Control  $^{45}$ .

# References

- Takeya, J. et al. Very high-mobility organic single-crystal transistors with in-crystal conduction channels. Appl. Phys. Lett. 90, 102120 (2007).

- Takeya, J. et al. In-crystal and surface charge transport of electric-field-induced carriers in organic single-crystal semiconductors. Phys. Rev. Lett. 98, 196804 (2007).

- Goldmann, C. et al. Determination of the interface trap density of rubrene single-crystal field-effect transistors and comparison to the bulk trap density. J. Appl. Phys. 99, 034507 (2006).

- Li, J. et al. A stable solution-processed polymer semiconductor with record high-mobility for printed transistors. Sci. Rep. 2, 754 (2012).

- Chen, H. et al. Highly π-extended copolymers with diketopyrrolopyrrole moieties for high-performance field-effect transistors. Adv. Mater. 24, 4618–4622 (2012).

- Lee, J. et al. Solution-processable ambipolar diketopyrrolopyrrole-selenophene polymer with unprecedentedly high hole and electron mobilities. J. Am. Chem. Soc. 134, 20713–20721 (2012).

- Lee, J. et al. Boosting the ambipolar performance of solution-processable polymer semiconductors via hybrid side-chain engineering. J. Am. Chem. Soc. 135, 9540–9547 (2013).

- Tseng, H.-R. et al. High mobility field effect transistors based on macroscopically oriented regionegular copolymers. Nano Lett. 12, 6353–6357 (2012).

- Luo, C. et al. General strategy for self-assembly of highly oriented nanocrystalline semiconducting polymers with high mobility. Nano Lett. 14, 2764–2771 (2014).

- Tseng, H.-R. et al. High-mobility field-effect transistors fabricated with macroscopic aligned semiconducting polymers. Adv. Mater. 26, 2993–2998 (2014).

- Yuan, Y. et al. Ultra-high mobility transparent organic thin film transistors grown by an off-centre spin-coating method. Nat. Commun. 5, 3005 (2014).

- 12. Giri, G. et al. Tuning charge transport in solution-sheared organic semiconductors using lattice strain. Nature 480, 504–508 (2011).

- Blülle, B., Häusermann, R. & Batlogg, B. Approaching the trap-free limit in organic single-crystal field-effect transistors. *Phys. Rev. Appl.* 1, 034006 (2014).

- Teague, L. C. et al. Surface potential imaging of solution processable acenebased thin film transistors. Adv. Mater. 20, 4513–4516 (2008).

- Jurchescu, O. D. et al. Organic single-crystal field-effect transistors of a soluble anthradithiophene. Chem. Mater. 20, 6733–6737 (2008).

- Phan, H., Wang, M., Bazan, G. C. & Nguyen, T.-Q. Electrical instability induced by electron trapping in low-bandgap donor-acceptor polymer field-effect transistors. Adv. Mater. 27, 7004–7009 (2015).

- 17. Sirringhaus, H. 25th Anniversary Article: organic field-effect transistors: the path beyond amorphous silicon. *Adv. Mater.* **26**, 1319–1335 (2014).

- Fratini, S., Xie, H., Hulea, I. N., Ciuchi, S. & Morpurgo, A. F. Current saturation and Coulomb interactions in organic single-crystal transistors. *New J. Phys.* 10, 033031 (2008).

- Braga, D. & Horowitz, G. High-performance organic field-effect transistors. *Adv. Mater.* 21, 1473–1486 (2009).

- Reyes-Martinez, M. A., Crosby, A. J. & Briseno, A. L. Rubrene crystal fieldeffect mobility modulation via conducting channel wrinkling. *Nat. Commun.* 6, 6948 (2015).

- Hamadani, B. H. & Natelson, D. Temperature-dependent contact resistances in high-quality polymer field-effect transistors. *Appl. Phys. Lett.* 84, 443–445 (2004).

- Hamadani, B. H., Richter, C. A., Suehle, J. S. & Gundlach, D. J. Insights into the characterization of polymer-based organic thin-film transistors using capacitance-voltage analysis. *Appl. Phys. Lett.* 92, 203303 (2008).

- Kahn, A., Koch, N. & Gao, W. Electronic structure and electrical properties of interfaces between metals and π-conjugated molecular films. *J. Polym. Sci. Part B Polym. Phys.* 41, 2529–2548 (2003).

- Scott, J. C. Metal-organic interface and charge injection in organic electronic devices. J. Vac. Sci. Technol. A 21, 521–531 (2003).

- Miyadera, T., Minari, T., Tsukagoshi, K., Ito, H. & Aoyagi, Y. Frequency response analysis of pentacene thin-film transistors with low impedance contact by interface molecular doping. *Appl. Phys. Lett.* 91, 013512 (2007).

- Gundlach, D. J. et al. An experimental study of contact effects in organic thin film transistors. J. Appl. Phys. 100, 024509 (2006).

- Necliudov, P. V., Rumyantsev, S. L., Shur, M. S., Gundlach, D. J. & Jackson, T. N. 1/f noise in pentacene organic thin film transistors. *J. Appl. Phys.* 88, 5395–5399 (2000)

- Zimmerling, T. & Batlogg, B. Improving charge injection in high-mobility rubrene crystals: from contact-limited to channel-dominated transistors. *J. Appl. Phys.* 115, 164511 (2014).

- Teague, L. C. et al. Probing stress effects in single crystal organic transistors by scanning Kelvin probe microscopy. Appl. Phys. Lett. 96, 203305 (2010).

- Nichols, J. A., Gundlach, D. J. & Jackson, T. N. Potential imaging of pentacene organic thin-film transistors. Appl. Phys. Lett. 83, 2366–2368 (2003).

- Li, T., Ruden, P. P., Campbell, I. H. & Smith, D. L. Investigation of bottomcontact organic field effect transistors by two-dimensional device modeling. *J. Appl. Phys.* 93, 4017–4022 (2003).

- Shannon, J. M. & Gerstner, E. G. Source-gated thin-film transistors. IEEE Electron Device Lett. 24, 405–407 (2003).

- Sporea, R. A., Guo, X., Shannon, J. M. & Silva, S. R. Source-gated transistors for versatile large area electronic circuit design and fabrication. *ECS Trans.* 37, 57–63 (2011).

- Ma, A. M. et al. Zinc oxide thin film transistors with Schottky source barriers. Solid-State Electron. 76, 104–108 (2012).

- Ma, A. M. et al. Schottky barrier source-gated ZnO thin film transistors by low temperature atomic layer deposition. Appl. Phys. Lett. 103, 253503 (2013).

- Appenzeller, J., Radosavljević, M., Knoch, J. & Avouris, P. Tunneling versus thermionic emission in one-dimensional semiconductors. *Phys. Rev. Lett.* 92, 048301 (2004).

- Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- Chow, P.-M. D. & Wang, K.-L. A new AC technique for accurate determination of channel charge and mobility in very thin gate MOSFET's. *IEEE Trans. Electron Devices* 33, 1299–1304 (1986).

- Wakatsuki, Y., Noda, K., Wada, Y., Toyabe, T. & Matsushige, K. Molecular doping effect in bottom-gate, bottom-contact pentacene thin-film transistors. *J. Appl. Phys.* 110, 054505 (2011).

- Gundlach, D. J., Jia, L. L. & Jackson, T. N. Pentacene TFT with improved linear region characteristics using chemically modified source and drain electrodes. *IEEE Electron Device Lett.* 22, 571–573 (2001).

- Kymissis, I., Dimitrakopoulos, C. D. & Purushothaman, S. High-performance bottom electrode organic thin-film transistors. *IEEE Trans. Electron Devices* 48, 1060–1064 (2001).

- Gundlach, D. J. et al. Contact-induced crystallinity for high-performance soluble acene-based transistors and circuits. Nat. Mater. 7, 216–221 (2008).

- Noda, K., Wada, Y. & Toyabe, T. Intrinsic difference in Schottky barrier effect for device configuration of organic thin-film transistors. *Org. Electron.* 15, 1571–1578 (2014).

- Pernstich, K. P. et al. Threshold voltage shift in organic field effect transistors by dipole monolayers on the gate insulator. J. Appl. Phys. 96, 6431–6438 (2004).

- 45. Pernstich, K. P. Instrument Control (iC)—an open-source software to automate test equipment. *J. Res. Natl Inst. Stand. Technol.* 117, 176 (2012).

# Acknowledgements

We thank Oleg Kirillov for design and fabrication of transistor test beds.

## **Author contributions**

E.G.B., J.I.B. and D.J.G. designed the experiments. E.G.B. fabricated and measured OFET devices, and analysed the data. J.I.B. wrote the code used to analyse the impedance data. T.N.J., O.D.J. and D.J.G. supervised the project. E.G.B. and D.J.G. wrote the manuscript; O.D.J. and D.J.G. edited the manuscript. Certain commercial equipment, instruments or materials are identified in this paper to specify the experimental procedure adequately. Such identification is not intended to imply recommendation or endorsement by the National Institute of Standards and Technology, nor is it intended to imply that the materials or equipment identified are necessarily the best available for the purpose.

### **Additional information**

**Supplementary Information** accompanies this paper at http://www.nature.com/naturecommunications

$\label{lem:competing financial interests:} The \ authors \ declare \ no \ competing \ financial \ interests.$

**Reprints and permission** information is available online at http://npg.nature.com/reprintsandpermissions.

**How to cite this article:** Bittle, E. G. *et al.* Mobility overestimation due to gated contacts in organic field-effect transistors. *Nat. Commun.* 7:10908 doi: 10.1038/ncomms10908 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this

article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/