Open Access

This article is licensed under <a href="#">CC-BY-NC-ND 4.0</a> © (\*) (\*) (\*)

pubs.acs.org/CR

## Phase-Change Memory for In-Memory Computing

Published as part of Chemical Reviews special issue "Neuromorphic Materials".

Ghazi Sarwat Syed,\* Manuel Le Gallo, and Abu Sebastian

Cite This: Chem. Rev. 2025, 125, 5163-5194

## **ACCESS** |

Metrics & More

Article Recommendations

ABSTRACT: In-memory computing (IMC) is an emerging computational approach that addresses the processor-memory divide in modern computing systems. The core concept is to leverage the physics of memory devices and their array-level organization to perform computations directly within the memory array. Phase-change memory (PCM) is a leading memory technology being explored for IMC. In this perspective, we review the current state of phase-change materials, PCM device physics, and the design and fabrication of PCM-based IMC chips. We also provide an overview of the application landscape and offer insights into future developments.

#### CONTENTS

| 1. Introduction                                       | 5163 |  |

|-------------------------------------------------------|------|--|

| 2. Part 1: Evolution of Materials, Devices, and Chips | 5165 |  |

| 2.1. Materials Engineering                            | 5165 |  |

| 2.2. Device Engineering                               | 5166 |  |

| 2.3. Chip Scale Demonstration                         | 5166 |  |

| 3. Part 2: Material Properties                        | 5167 |  |

| 3.1. Property A: Glass Formation Ability              | 5167 |  |

| 3.2. Property B: Crystallization Kinetics             | 5168 |  |

| 3.3. Property C: Electronic and Atomic Structure      | 5169 |  |

| 3.4. Property D: Structural Relaxation and Noise      |      |  |

| Characteristics                                       | 5169 |  |

| 3.5. Property E: Carrier Transport                    | 5170 |  |

| 4. Part 3: Device Properties                          | 5172 |  |

| 4.1. Threshold Switching                              | 5172 |  |

| 4.2. Device Failure Modes                             | 5172 |  |

| 4.3. Nonidealities                                    | 5173 |  |

| 4.4. Cell Geometry                                    | 5175 |  |

| 4.5. New Device Concepts                              | 5176 |  |

| 5. Part 4: Chip Design and Integration                | 517  |  |

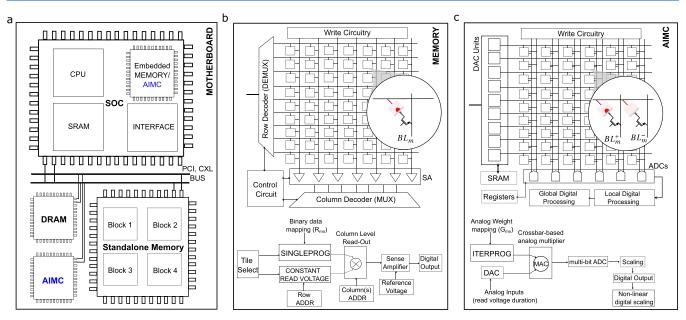

| 5.1. Microarchitecture Differences                    | 5177 |  |

| 5.2. Differences in Device Requirements               | 5179 |  |

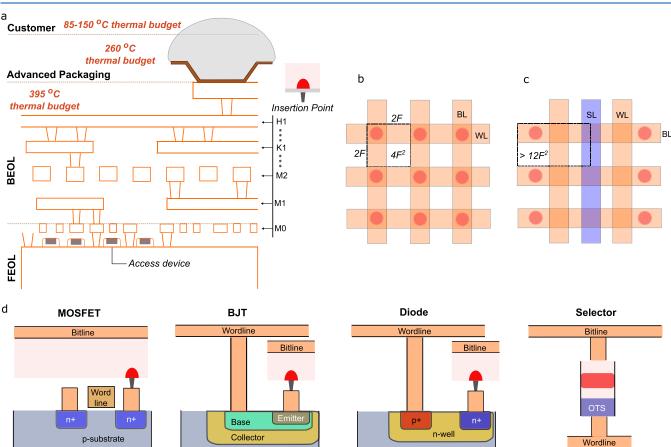

| 5.3. Device Integration                               | 5180 |  |

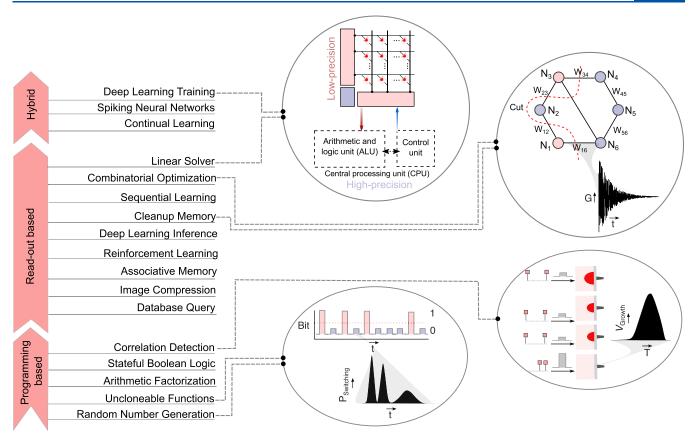

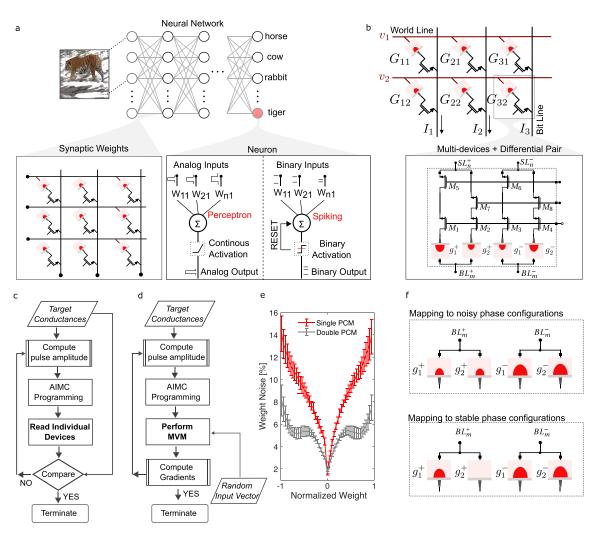

| 5. Part 5: Application Portfolio of PCM-Based IMC     | 5182 |  |

| 7. Outlook                                            | 5187 |  |

| Author Information                                    | 5187 |  |

| Corresponding Author                                  |      |  |

| Authors                                               |      |  |

| Notes                                                 |      |  |

| Biographies                                           | 5188 |  |

Acknowledgments References 5188 5188

### 1. INTRODUCTION

In the present day, semiconductor materials are typically described in physics textbooks as having a periodically ordered arrangement of atoms, a disordered amorphous arrangement, or a mixture of both. However, this was not always the case. For a long time, textbooks mainly discussed crystals as the only viable materials for functional semiconductor devices. This belief was largely because the initial semiconductor devices, such as the transistor, were created from crystalline materials such as germanium and silicon. In the early 1960s, this belief started to be challenged. The research centered around chalcogenide glasses, which consist of elements from the oxygen group of the periodic table, including sulfur, selenium, and tellurium. By introduction of thin films of tellurium alloyed with neighboring elements such as arsenic and antimony, studies began to demonstrate that these glasses could switch between resistive and conducting states, similar to the behavior of transistors. Furthermore, some materials stayed conductive until a stronger electrical current pulse was applied to revert

Received: September 2, 2024 Revised: April 24, 2025 Accepted: April 29, 2025 Published: May 22, 2025

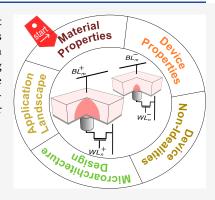

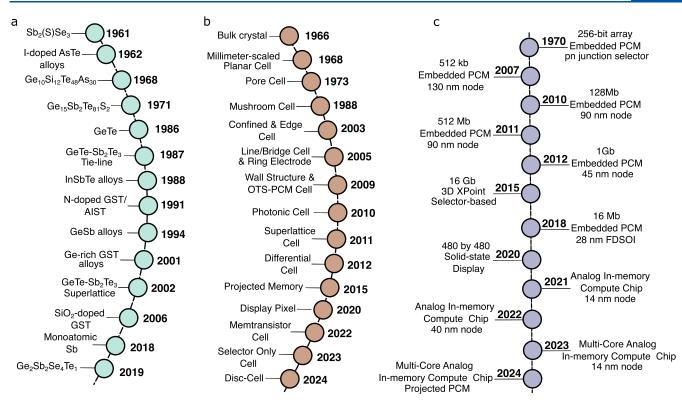

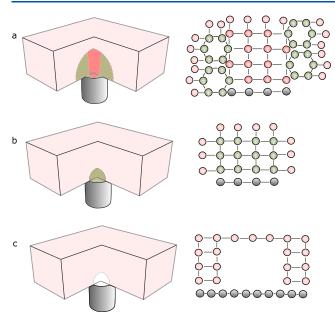

Figure 1. Phase change mechanism and operational regimes. (a) This artistic depiction illustrates heat-induced solid-state transitions between amorphous and crystalline phases within a phase change material, such as  $Ge_2Sb_2Te_5$ . These phases exhibit distinct electrical, thermal, and mechanical properties. <sup>10–13</sup> In PCM devices, nanosecond time-scale current pulses generate Joule heating. (b) Illustration of the two key physical attributes that facilitate computation using PCM devices. The right panel depicts the direct overwrite regime using melt-quench dynamics. Programming curves demonstrate achievable conductance values in response to partial RESET pulses of varying amplitudes. Increasing the amplitude of the RESET pulse results in the formation of a larger amorphous volume, largely independent of the previous phase state. The left plot illustrates the accumulative property, displaying how conductance values evolve over successive applications of a constant amplitude SET pulse. As the amorphous region shrinks due to crystallization dynamics, the device conductance gradually increases.

them to the resistive state. This became what is currently known as phase-change memory (PCM). The early discovery of PCM has made it arguably the most mature memristive technology.<sup>2</sup> PCM stores information by altering the atomic configurations within a nanoscale volume of material, resulting in a change in device conductance. However, unlike mainstream metal-oxide-based memristive devices, PCM employs volumetric switching instead of filamentary switching. This volumetric switching is facilitated by specific materials such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, which can be reversibly toggled between amorphous and crystalline phases with differing electrical and thermal properties. Both of these transitions are assisted by Joule heating, i.e., the transition from the crystalline to the amorphous phase relies on a melt-quench process, while the reverse transition primarily relies on crystal growth<sup>3-5</sup> (see Figure 1a). One of the appealing characteristics of PCM is its ability to retain stored data for long durations, typically up to 10 years at room temperature, while also enabling data to be written in just tens of nanoseconds. This characteristic continues to position PCM as a candidate for high-density nonvolatile data storage.6-

Another particularly interesting emerging application, regarded as a natural transition for PCM due to its similarities with data-storage technology, is computational memory or inmemory computing (IMC). <sup>14,15</sup> In this paradigm, PCM devices are utilized not only for data storage but also for performing certain computational tasks. For example, by using PCM devices and two fundamental physical laws of electrical engineering, Ohm's law and Kirchhoff's current law, simple circuits can implement basic operations related to deep neural networks (DNNs) with mere femtojoules of energy. This approach eliminates the need to transfer data back and forth over power-hungry and high-latency interconnects between physically separated computing units and memory in conventional computers. Additionally, the potential for PCM devices

to achieve very small cell sizes could allow large DNNs to be held entirely on-chip in a nonvolatile manner.

There are two key properties leveraged in PCM-based IMC<sup>16</sup> (see Figure 1b). The first property is the ability of a PCM device to store a range of conductance levels, not just two. This is important because it enhances the storage density, where one device can encode an entire synaptic weight in the case of DNNs. Programming a continuum of conductance states in devices is easily achieved by varying phase configurations (or the amount and geometry of the amorphous volume in an otherwise crystalline phase-change material) through the application of partial amorphization pulses. The second property is the accumulative property resulting from crystallization dynamics. In this scheme, the device conductance evolves according to the number of (constant amplitude) crystallization pulses that encode a computational problem with the result of the computation stored in place. This property allows for fine adjustment of the conductance levels in the devices and is essential, for example, in emulating critical dynamics required in certain computations. These capabilities, combined with a scalable structure, termed a crossbar, that can be integrated readily using already established back-end-of-the-line (BEOL) processes present another key advantage. Through massive parallelization of computations, many distinct computations on the same data, the technology allows for nontrivial reductions in the time and space complexities for certain computational tasks.

In this review, we aim to provide readers with a comprehensive account of PCM-based IMC technology. The review is divided into five parts. The first part offers an overview of the history of key advancements in materials, device concepts, and chip designs that have brought PCM to its current state. The second part delves into the material science and physics of phase-change materials, highlighting the key properties that make these materials such fascinating

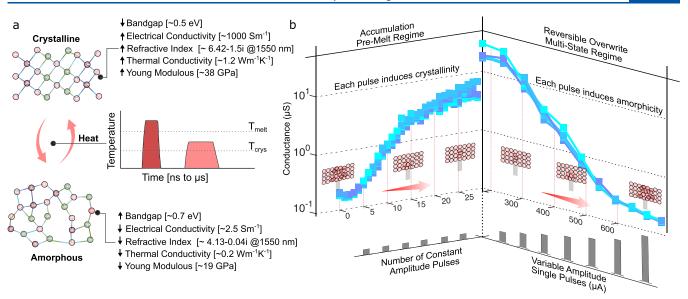

Figure 2. Historical overview of PCM. Timeline plots illustrate the evolution of PCM (a) materials, (b) devices, and (c) chips.

material systems. The third part explores the key device properties that underpin the capabilities and performance metrics of PCM devices. The fourth part compares PCM-based IMC chips with standard memory chips, highlighting the key differences (and thus the research opportunities). The fifth part surveys various applications that leverage PCM-based IMC. Finally, we present an outlook on the opportunities and challenges.

## PART 1: EVOLUTION OF MATERIALS, DEVICES, AND CHIPS

## 2.1. Materials Engineering

The early observations of phase-change phenomena in solidstate electrical devices can be traced back to experiments with stibnite<sup>17</sup> (Sb<sub>2</sub>Se<sub>3</sub>) and ternary glass compositions<sup>18</sup> of As-Te-I (see Figure 2a). However, these materials were hindered by a limited number of switching cycles, presumably due to the sublimation and decomposition of elements due the high operational electrical currents. 19 A breakthrough occurred in 1968 with the observation of stable switching in As-Te-Ge glass, specifically within the composition of  $Si_{12}Te_{48}As_{30}Ge_{10}$ , which demonstrated a notable memory effect. Minor modifications to this composition were found to sustain a low-resistance state after switching, maintaining this state even in the absence of an applied voltage. From the early 1970s through the mid-1980s, research focused on Te-based eutectic alloys with low melting points, such as Te-Ge and Te-Sb, which were favored due to their ability to easily transition into an amorphous state. Among these, GeTe was notable for its fast crystallization and large properties contrast, 20 yet its substantial volume expansion of 10% presented challenges for enduring multiple phase transitions. This prompted a shift toward exploring GeTe-based compositions within the GeTe-

Sb<sub>2</sub>Te<sub>3</sub> tie-line, <sup>21</sup> including variants like Ge<sub>14</sub>Sb<sub>29</sub>Te<sub>57</sub> (commonly referred to in atomic fraction ratio as Ge<sub>1</sub>Sb<sub>2</sub>Te<sub>4</sub>), Ge<sub>19</sub>Sb<sub>25</sub>Te<sub>56</sub>, Ge<sub>22</sub>Sb<sub>22</sub>Te<sub>56</sub>, and Ge<sub>25</sub>Sb<sub>18</sub>Te<sub>55</sub>. These compositions undergo a two-step crystallization process, resulting in a ~4% volume change.<sup>22</sup> The transition involves progressing from the amorphous to the metastable cubic phase and subsequently to the stable hexagonal phase. Ge<sub>22</sub>Sb<sub>22</sub>Te<sub>56</sub>, commonly referred to as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST),<sup>23</sup> offers good amorphous-phase stability with activation energies exceeding 2.2 eV, making it a preferred material for data storage applications.<sup>21</sup> Further exploration into another chalcogenide family, centered on the Sb<sub>x</sub>Te<sub>y</sub> eutectic alloy and commonly denoted as doped SbTe compounds, 24,25 involved doping with In (e.g.,  $In_x(Sb_7Te_3)_{1-x}$ ) or with Ag and In (e.g.,  $Ag_xIn_y(Sb_{70}Te_{30})_{1-x-y}$ , also referred to as AIST). These compositions exhibited growth-dominated characteristics, contrasting with the nucleation-driven tie-line compositions, and swiftly garnered considerable attention for optical data storage. The role of individual elements also became clearer with such studies. Sb-rich compositions enabled fast crystallizing materials, while Ge-rich (Te-poor) alloys showed higher thermal stability against crystallization.

In the 2000s, as interest in electrical memory devices surged, the focus shifted toward engineering materials capable of low programming currents, higher retention (amorphous phase stability), enhanced endurance, and faster crystallization speeds. Achieving low programming currents and higher retention involved increasing the electrical resistivity of the films, which was accomplished through Ge-rich compositions or doping with elements like  $^{26-28}$  N, C, O, and dielectrics such as  $\mathrm{SiO}_2$ , as well as reducing the physical thickness of the material. It is worth noting that since dopant concentrations could reach nontrivial amounts (up to 15 at. %), the term doping is often replaced by alloying in the context of phase-

change materials. Improving endurance has involved developing materials with minimal volume changes during phase transitions, as well as compositions with reduced elemental and phase segregation propensities. Even monatomic composition, specifically using only Sb, has been explored as a phase-change material.<sup>31</sup> Techniques like templated crystallization from nanoparticles like Au and substructure stabilizing dopants such as Sc have demonstrated improvements in the crystallization switching speeds.<sup>32</sup> More recently, chalcogenide-based materials have garnered attention as promising materials for integrated optical memories and reconfigurable photonic devices. This interest arises from their unique combination of large optical contrast (with  $\Delta n$  ranging from approximately 0.5 to 3.5). The requirement to reduce excessive loss from free carrier absorption has spurred interest in newer compositions such as  $Ge_2Sb_2Se_4Te_1$ ,  $^{\frac{1}{3}3}$  and has renewed the interest in  $Sb_2Se_3$  and  $Sb_2S_3$  materials.  $^{34}$  Significant advancements have been made in the high-throughput screening of phase-change materials. Unlike traditional sequential synthesis, where bulk materials are synthesized, deposited, and characterized separately, these methods enable combinatorial synthesis, i.e., the deposition of compositional gradients on a single substrate, also allowing for in situ characterization of the material properties. The approach utilizes controlled codeposition from separate targets onto temperature-controlled substrates with independently operated shutters.<sup>35</sup> Additionally, closed-loop autonomous systems that integrate in situ real-time measurements with machine learning have been developed to accelerate discovery of newer materials.<sup>30</sup>

## 2.2. Device Engineering

Comparable to the first functional transistor, the electrical configuration of early PCM devices involved bulky electrical probes, typically featuring one fixed and one mobile probe, making lateral contact with the chalcogenide crystals (Figure 2b). Subsequently, investigations into thin-film-based phasechange films commenced. Among the initial realizations were planar and pore-type structures,<sup>37</sup> which exhibited reversible switching characteristics. It became apparent early on that the energy needed to switch PCM was directly proportional to the volume of phase-change material,<sup>38</sup> and contact areas to the electrode, prompting efforts to minimize feature size. Since the first memory chip was reported, <sup>39</sup> PCM devices have decreased in size by a factor of 1000, and their switching currents have also been reduced by a factor of 1000. Among the first successful device designs were mushroom-type<sup>40</sup> and confinedtype<sup>41</sup> devices, which were made at the 180 and 230 nm technology node. These device designs provided vertical integration and became a starting point for two modern-day approaches in PCM device engineering: contact minimization and volume minimization, respectively. The advent of electron lithography enabled the creation of small contacts between electrodes and ultrathin phase-change films, achieving crosssectional areas as small as 225 nm<sup>2</sup> in the early 2000s. This development gave rise to the formation of line or bridge cell structures. 42 However, due to their lateral span, these structures could not be integrated with high density, limiting their applicability to serving as test structures for material screening and fundamental device studies. In the pursuit of reducing programming currents even further, newer device structures were introduced. These included designs utilizing ring-type electrodes<sup>43</sup> and wall-type structures.<sup>44</sup> The former employed a bottom electrode composed of a thin film of metal

arranged in an annular shape, surrounding a core made of dielectric material instead of a single solid metal. On the other hand, the latter design aimed to generate Joule heating not within the phase-change material itself but within the bottom electrode and then transfer it to the phase-change material. This approach led to the bottom electrode being commonly referred to as a 'heater'. Following these approaches, some specific modern-day device structures exhibit programming energies in the tens of femtojoules via extreme volume/contact scaling. 45–48 In efforts to improve the integration density, a thin-film two-terminal Ovonic Threshold Switch (OTS) as the selector of a PCM device was soon demonstrated.

Commercial PCM products notably utilized device designs established before 2010. However, over the past decade, there has been a surge in the development of new device designs that can be tailored for emerging applications. These include functional on-chip photonic<sup>50,51</sup> PCM devices, as well as microheater-based structures enabling solid-state phase-change display pixels<sup>52</sup> and RF switches. Additionally, significant advances have been made in computational PCM unit cells, incorporating multisynaptic devices<sup>53</sup> and employing differential configurations. 54,55 Novel device structures, such as the projected-type, which incorporate a noninsulating layer to redirect current flow around the amorphous volume, have been developed to enhance computational precision. 56,57 Furthermore, structures like memtransistive devices, designed to execute more sophisticated computations, have also emerged.<sup>58</sup> Significant advancements have also been made in enabling devices with ultralow programming currents, such as superlattice structures formed by stacking chalcogenide films, 59 and the disc-type device, which confines the active switching region to a compact geometry, thereby enhancing Joule heating efficiency and thermal confinement. 60 Furthermore, selector-only devices have been introduced that use chalcogenide materials that do not rely on phase transitions induced by Joule heating for conductance modulation. These devices combine memory and selector functionalities into a single unit<sup>61</sup> and due to reduced thermal crosstalks, promise a scalability that surpasses the OTS-PCM cells.

#### 2.3. Chip Scale Demonstration

The earliest lab-scale demonstrations of PCM chips occurred in 1969 with a passive crossbar<sup>19</sup> based on an As-Ge-I alloy (see Figure 2c). By 1970, a 256-bit array of amorphous semiconductor memory cells, connected in series with silicon p-n junction diodes to minimize sneak currents, was developed.<sup>39</sup> However, the volume of phase-change material required for device operation was too large, resulting in a significant power consumption during programming operations. Subsequently, in 1978, a 1024-bit PCM chip was demonstrated. Although the programming voltages and currents in this chip were lower than those in earlier attempts, they still fell short of being competitive with the memory technologies of the time. From the 1980s to the early 2000s, attempts to develop reliable PCM cells have faced significant challenges, leading to device degradation and operational instability. Consequently, interest in electrical memory cells using phase-change materials had gradually declined. However, since the 1990s, phase-change materials have found widespread use in optical memory devices and continue to serve as information storage medium in CDs, DVDs, and Blu-Ray disks.

The success of optical storage using phase-change materials sparked renewed interest in PCM in the early 2000s.

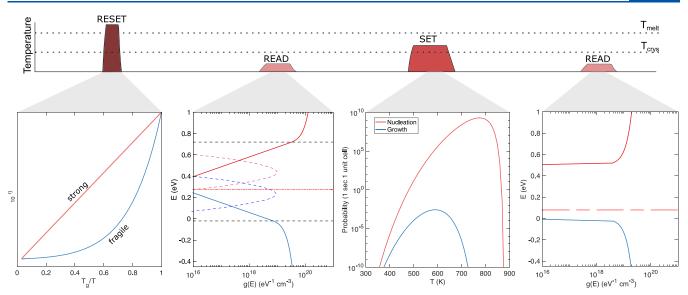

Figure 3. Conceptual illustrations of programming and read operations in PCM. (a) A RESET operation transitions the PCM device to a low conductance state by heating the phase-change material above its melting temperature, followed by rapid cooling. The high fragility in viscosity induces amorphization. (b) A low conductance value is measured during the READ operation, which can be attributed to charge transport mediated by the amorphous phase's defect states. These are shown as Gaussian-distributed profiles for acceptor and donor-type trap states in the energy band diagram (g(E)) represents the density of states). Note that the Fermi level is pinned in the middle of the bandgap due to the equal concentration of the donors and acceptors states. (c) A SET operation transitions the PCM device to a high-conductance state by crystallizing a previously amorphous region by heating the phase-change material above its crystallization temperature. Material and temperature-dependent nucleation and growth rates, as illustrated in the panel determine the crystallization speed. (d) The higher conductance is measured during the READ operation, which can be attributed to the disappearance of the localized traps states.

Companies such as Intel, Samsung, STMicroelectronics, Micron, and SK Hynix obtained licenses to begin manufacturing their own PCM chips of various sizes. In 2008, Numonyx, a memory company formed by Intel and STMicroelectronics and later acquired by Micron in 2010, introduced the first PCM product consisting of 128-Mbit chips in the 90 nm CMOS process.<sup>62</sup> Meanwhile, in 2007, Hitachi demonstrated<sup>63</sup> a 512-kbit memory in 130 nm CMOS technology. Micron also introduced a 45 nm 1-Gbit PCM chip in 2012, supplied to Nokia for integration into mobile phones, but it was withdrawn in 2014.64 In 2011, IBM demonstrated 512-Mbit 2bit/cell multilevel memory cells 90 nm, 65 followed by 4bit/cell in 2013.66 A significant advancement in PCM technology occurred with the announcement of 3D Xpoint memory by Intel and Micron.<sup>67</sup> This technology supposedly utilized a Gerich phase-change alloy as the storage component and another chalcogenide glass as the selector element. The technology was introduced in 2015 (although only commercialized in 2018) under the Intel Optane brand, offering low-latency, lowcapacity nonvolatile memory options ranging from 16 to 64 GB. The production of 3D Xpoint memory, however, ceased in 2022, supposedly owing to an inadequate market need.<sup>68</sup> In 2023, SK Hynix demonstrated its version of a four-tier 3D Xpoint memory.<sup>69</sup> STMicroelectronics also commercially introduced a chip manufacturing process based on 28 nm fully depleted silicon-on-insulator (FDSOI) for Ge-rich phasechange alloy-based embedded PCM, for automotive, microcontroller applications.<sup>70</sup> In the realm of computational PCM, IBM demonstrated IMC cores based on 256 × 256 and 512 × 512 crossbar arrays<sup>71,72</sup> in 14 nm technology, designed to perform deep neural network inference. These cores utilized doped GST-based mushroom-type PCM devices. In 2022, TSMC introduced their AIMC chip in 40 nm. <sup>73</sup> Subsequently, IBM presented a fully integrated chip featuring 64 AIMC cores

interconnected through an on-chip communication network, which also included digital activation functions and additional processing capabilities.<sup>74</sup> An alternative version of this chip with an analogue communication fabric was also demonstrated.<sup>75</sup> In 2023, further advancements were made with demonstrations<sup>76</sup> of AIMC cores based on mushroom-type projected PCM devices.

## 3. PART 2: MATERIAL PROPERTIES

Three key characteristics make chalcogenide phase-change materials functional. First, there is a significant contrast in properties between the amorphous and crystalline states. Second, the phase transitions occur within time scales that are relevant for technological applications. Third, and somewhat counterintuitively, these phases exhibit high stability at room temperature despite the rapid transitions. While many materials, including prototypical dielectrics and metallic alloys, undergo solid-state transformations, they typically lack one or more of these critical features. This section explores the essential material properties that enable the unique functionalities of phase-change materials.

#### 3.1. Property A: Glass Formation Ability

The unusually significant nonlinear temperature-dependent viscosity  $\eta(T,t) \propto \exp\left(-\frac{Q}{k_{\rm B}T}\right)t\bigg|_{T=T_{\rm g}}$  plays a key role in the

amorphization (vitrification) in phase-change materials (see the first panel in Figure 3). Here, Q and  $T_{\rm g}$  are the material-dependent activation energy of viscosity and the glass-transition temperature, respectively, and  $k_{\rm B}$  is the Boltzmann constant. Generally, during melt-quenching, as the temperature of the melt decreases, the viscosity  $\eta$  increases (in other words, the atomic diffusivity decreases), reaching a point where the structure can no longer keep up with the temperature change,

resulting in a glassy structure. A high viscosity in the supercooled liquid is a fundamental requirement for glass formation. Good glass formers are strong liquids that exhibit resistance to structural changes with temperature due to strong interatomic interactions (e.g., covalent bonding), leading to minimal reorganization over a wide temperature range. Viscosity, thus behaves in an almost Arrhenius fashion, increasing by several orders of magnitude over a large temperature range. Examples of good glass formers include inorganic materials such as oxides, like silica. In contrast, liquids with softer interatomic interactions, such as organic polymers (with, e.g., ionic, van der Waals bonding) have high fragility, causing viscosity to marginally change near melttemperature, but change rapidly by several orders of magnitude over a small temperature range near  $T_g$ . Interestingly, although inorganic, phase-change materials behave similarly to organic liquids and polymers in their glass formation ability, in that  $\eta(T_{\rm o})$  is very nonlinear. This characteristic is typically

measured in terms of fragility

$$\left(m = \frac{\partial \log \eta(T)}{\partial (T_g/T)}\bigg|_{T=T_g}\right)$$

, and phase-

change materials have  $m \to 100$  (e.g., 90 for liquid GST), much higher than strong liquids (m < 20, e.g. SiO<sub>2</sub>).

This behavior is associated with fragile-to-strong transitions, which are linked to temperature-dependent reordering in the atomic configurations within the supercooled liquid, resulting from more mobile atomic arrangements to rigid ones. Indeed, measurements have identified and quantified liquid-liquid phase transitions in chalcogenide materials. 78,79 Without these transitions, phase-change materials would not form glass at practical cooling rates. Furthermore, at elevated temperatures (around  $T_{crvs}$ , which is the crystallization temperature), high fragility enhances atomic mobility in the amorphous phase, leading to rapid crystallization within nanoseconds during SET operation. For reference, the crystallization temperature  $(T_{crys})$ for GST is 165 °C, and in other prototypical GeTe-Sb<sub>2</sub>Te<sub>3</sub> compositions,  $T_{\text{crys}}$  increases with the GeTe content,<sup>21</sup> rising from 90 °C for  $S\dot{b}_2Te_3$  up to 190 °C. As a comparison  $T_{\rm crys}$  of SiO<sub>2</sub> is 1200 °C. Conversely, the requirement for a strong-tofragile transition significantly restricts atomic mobility during read-out operations (below  $T_g$ ), thereby slowing down crystallization. This ensures the desired retention of the amorphous phase (in GST, approximately 10<sup>8</sup> s at 300 K). Heuristically, the stability of the amorphous phase is expressed as  $t_{\rm failure} \propto \exp\left(-\frac{E_{\rm crys}}{k_{\rm B}T}\right)$ , where  $E_{\rm crys}$  is the activation energy of

as  $t_{\rm failure} \propto \exp\left(-\frac{cys}{k_{\rm B}T}\right)$ , where  $E_{\rm crys}$  is the activation energy of crystallization. Typically, eutectic alloys exhibit poor retention due to their low  $T_{\rm g}$ , generally between 0.33 and 0.66 of the melt temperature. So In compounds like GST, doping with Ge and dielectrics has been shown to raise the activation energies from 2.2 to 3.1 eV, roughly equivalent to a 50 °C increase in the crystallization temperature.

The rapid crystallization behavior of phase-change materials at elevated temperatures poses a significant challenge for characterizing their liquid-state properties. The supercooled liquid regime  $(T_{\rm melt}-T_{\rm crys})$  is often inaccessible using standard techniques for extracting  $\eta$  data. This also makes accurate determination of  $T_{\rm g}$  difficult. The limitation has led to the use of unconventional methods, such as ultrafast differential scanning calorimetry, and analytical data-fitting using transmission electron microscopy measurements on crystal growth. However, there are limitations to these approaches.

For example, phase-change materials exhibit a breakdown of the Stokes–Einstein equation  $^{83,84}$  in their viscosity-diffusivity relationship; the inverse proportionality decouples near  $T_{\rm melt}$  and room temperature. This can impact the interpretations made from the fitted traces across a wide temperature range.

## 3.2. Property B: Crystallization Kinetics

As previously discussed, phase-change materials are marginal glass formers. This observation is also consistently made in the low values of the Turnbull parameter ( $T_{\rm rg} = T_{\rm g}/T_{\rm m}$ ) that establishes an inverse empirical relation to the nucleation rate.  $T_{\rm rg}$  varies between 0.45 and 0.55 for different phase-change materials, implying the materials have a high degree of propensity for crystallization. Indeed, crystallization can occur so swiftly that achieving a stable amorphous state necessitates cooling rates between  $10^9$  and  $10^{11}$  K/s to prevent crystallization. Due to the inherently low thermal conductivity of phase-change materials, rapid cooling is achievable primarily by efficiently transferring heat to adjacent materials. The efficiency of this quenching process improves with an increase in the surface-to-volume ratio of the phase-change region and thus in nanoscaled devices.

The crystallization kinetics in PCM devices at elevated temperatures can be driven by either nucleation or growth processes (see the third panel in Figure 3), and this area has been and continues to be a subject of intensive investigation. Nucleation involves a stochastic process where a crystalline nucleus gradually attains a critical size at which it becomes stable and can grow instead of dissolving. As a consequence, nucleation is expected to occur with equal probability or homogeneously in all parts of the volume. The attainment of this critical-size nucleus requires an incubation period. The size of the critical nucleus is influenced by temperature and is determined by the difference in bulk free energy between the amorphous and crystalline phases (which reduces the critical size as it increases), the interfacial energy density between these phases (which increases the critical size as it increases), and the strain energy (which increases the critical size as it increases).

On the other hand, crystal growth (i.e., the addition of more and more monomers) occurs once the nucleus reaches this critical size and is a deterministic process. Crystal growth velocity is strongly temperature-dependent and is governed by two opposing factors: the difference in free energy between the crystalline phases and liquid, which increases growth velocity as it rises, and the viscosity of the material, which reduces growth velocity as it increases. Thus, the amorphous volume takes the expressions,  $u_{\rm a}=u_{\rm a,o}-\int_{t_0}^{t_{\rm x}}v_{\rm g}(T)\,{\rm d}t$ , where  $u_{\rm a,o}$

denotes the initial amorphous thickness,

$$v_{\rm g}=v_{\rm g\infty}\exp\Bigl(-\frac{E_{\rm G}}{k_{\rm b}T}\Bigr)$$

is the temperature-dependent growth velocity. Depending upon whether nucleation or growth exercises dominant control over the phase transformation process, phase-change materials become differentiated into nucleation-driven and growth-driven. Examples of nucleation-dominated phase-change materials include Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, and Ge<sub>4</sub>Sb<sub>2</sub>Te<sub>2</sub>, while Ag and In doped SbTe, GeSb, GeSnSb, and Ge<sub>3</sub>Sb<sub>6</sub>Te<sub>5</sub> compositions are examples of growth-dominated systems.

However, on the technologically relevant scales of nanometres and nanoseconds in PCM devices, the distinction between these two conjugate crystallization models has been suggested to blur out.<sup>87</sup> This is because the significance of

nucleation diminishes, and the process of crystallization tends to be dominated by the growth of crystals; as the volume of the crystallizing material decreases, the proportion of atoms in contact with the surrounding environment, which in devices can be a crystalline phase of the phase-change material-increases. Therefore, in the compact cells of phase-change material utilized in memory devices, the likelihood of nucleation and growth from the boundary/interface between the crystal and amorphous phase is anticipated to be significantly greater than that of homogeneous-type nucleation. This behavior is further exacerbated by the fact that a substantial number of nuclei are already present due to the melt-quenched nature of the amorphous state. Within electrical devices, such nuclei grow with a peak  $\nu_{\rm g}$  that exceeds > 1 nm ns $^{-1}$  at elevated temperatures.  $^{82,87}$

Experimental evidence that can unambiguously distinguish the contrasting crystal growth behaviors within the same device type, such as variations due to phase configuration and length scale, has yet to be demonstrated. Additionally, because of high computational costs, it remains challenging to model nucleation and heterogeneous growth through molecular dynamics simulations over extended time scales and larger length scales. To address these challenges, newer approaches have been developed, including those based on trainable interatomic potentials using machine learning. S8,89 However, simulations covering the entire volume of the active material in real devices, while accounting for factors like preseeded nuclei, interfaces, and existing electro-thermal gradients, have yet to be demonstrated.

#### 3.3. Property C: Electronic and Atomic Structure

In chalcogenides, strong and weak atomic bonds coexist. For example, Te atoms form 2-fold covalent bonds, creating -Te-Te-Te- coil-like chains that assemble into a hexagonal crystal structure, held together by weak van der Waals forces. These weak interchain forces arise, in part, from the presence of nonbonding lone-pair (LP) p-electrons on the chalcogen atoms, which contribute to the material's polarizability. Melting primarily involves breaking these weaker van der Waals interactions while preserving the stronger covalent bonds. As a result, unlike silicon—which exhibits a high melting temperature ( $T_{\rm melt}$  = 1140 °C) due to its fully covalent network—tellurium melts at a much lower temperature ( $T_{melt}$  $\sim$  450 °C). This bonding asymmetry is also manifested in the electrical properties of the melt: while many chalcogenides maintain semiconducting behavior in the molten state, typical III-V semiconductors become metallic. However, Te exhibits poor glass-forming ability because its 2-fold coordination favors rapid crystallization. To address this, Te-Sb-Ge alloys were developed, where dopants stabilize interchain cross-links through three- and 4-fold coordination. Nonetheless, binary eutectic alloys such as Te-Ge and Te-Sb often undergo phase segregation and fail to retain amorphous phases at moderate temperatures. To overcome these limitations, stoichiometric ternary Ge-Sb-Te compounds  $(Ge_xSb_yTe_{1-x-y})$  were introduced, offering improved thermal stability ( $T_{\rm melt} \sim 600$  °C) and greater resistance to phase separation.

The inherent structural disorder in the amorphous phase leads to significant electronic consequences. While short- and medium-range order is preserved, variations in bond lengths and bond angles introduce a distribution of electronic states that broaden the band edges. This broadening gives rise to Urbach tails, exponentially decaying states extending into the

band gap, as illustrated in the second panel of Figure 3. As a result, the optical band gap in these materials is typically narrower than the mobility band gap. Compounding this effect, the amorphous phase is suggested to carry a high density of localized electronic states arising from LP *p*-electrons. These are valence-alternation pairs, comprised of overcoordinated (C<sup>3+</sup>) and under-coordinated (C<sup>1-</sup>) chalcogen atoms. These LP-induced defect states are argued as a hallmark of chalcogenide glasses and are responsible for features which distinguish them from other covalently bonded semiconductors, such as amorphous -silicon and -III–V compounds. For example, these characteristics include the absence of a dark electron spin resonance signal, and in the middle of the band gap the Fermi level pinned near the middle of the band gap, restricting its ability to shift in response to impurity doping.

In the crystalline state, technologically relevant phases of phase-change materials often exhibit high-symmetry atomic arrangements, such as cubic structures, indicative of dominant p-bonding. This bonding configuration is susceptible to Peierls distortions<sup>23</sup> and favors octahedral coordination over the sp<sup>3</sup> bonding typical of most III-V semiconductors. For instance, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> adopts a rocksalt structure during device operation in which Te atoms occupy one face-centered cubic sublattice, while Ge and Sb atoms randomly populate the other. Within this structure, Te atoms form 2-fold coordinated chains, with Ge atoms linking these chains to Sb-containing planes. The crystalline phase also contains a significant fraction (up to 20%) of vacant Ge and Sb sites,<sup>91</sup> giving rise to Gaussianshaped, acceptor-like trap states with exponentially decaying wave functions. Upon thermal treatment, vacancy ordering has been associated with increased electrical resistivity, indicative of a metal-to-insulator transition. 92 Lastly, the nature of atomic bonding in the crystalline state remains one of the most debated topics in the field. One prevalent theory proposes an entirely new bonding mechanism, suggesting that phasechange materials exhibit electron sharing and transfer characteristics distinct from the more familiar covalent, metallic, and ionic bonds as well as the weaker hydrogen and van der Waals bonds.<sup>93,94</sup> Conversely, an opposing theory argues that no new bonding mechanism is required. Based on electronic wavefunction analysis, the study demonstrates that phase-change materials are governed by a single, unified chemical-bonding framework consisting of conventional twocenter covalent bonds and multicenter lone-pair-antibonding 'hyperbonds'. 95,96

## 3.4. Property D: Structural Relaxation and Noise Characteristics

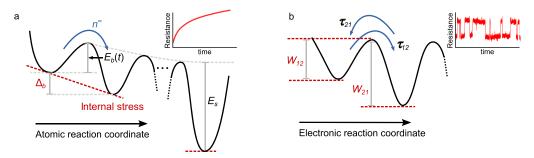

When a phase-change material is rapidly quenched from its molten state, the amorphous state thus formed is a highly stressed glass state, with atoms frozen in unstable configurations. The noncrystallinity in the phase-change material defines excess Gibbs free energy (difference between the amorphous and supercooled liquid state) in the system. As a result, the disordered amorphous structure, as a function of time and temperature relaxes toward the lower energy metastable supercooled liquid configurations. This process is manifested markedly in the embodiment of time-dependent changes in the material properties, including viscosity, density, and the electronic bandgap. More generally, structural relaxation follows three distinct phases. The first is the onset phase wherein, for some amount of time, the properties do not change. In the second phase, relaxation is most profound, and

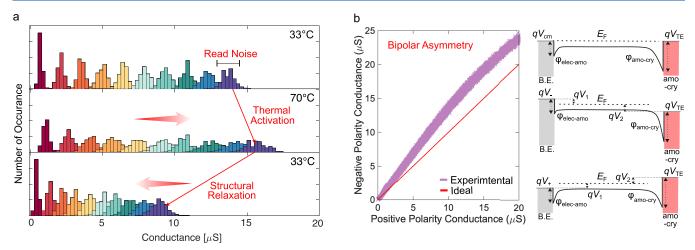

**Figure 4.** Structural relaxation and read noise. (a) The amorphous state is initially unstable and undergoes a series of transitions toward the more energetically favorable supercooled glass state. The activation energy for atomic reconfigurations increases as they involve the movement of atoms that have become progressively stabilized in their positions through prior relaxation steps. The inset shows an increase in device resistance over time due to structural relaxation. (b) A double-well potential model highlighting electronic transitions/switching between two energy minima, separated by a potential barrier. The inset shows fluctuations in device resistance from these transitions. It is further assumed that a distribution of double-well potentials exists to create the 1/f noise behavior typically observed in the devices.

the properties have been observed to change proportionally to log *t*. Finally, approaching the supercooled liquid, the glass reaches a saturation phase and the properties no longer continue to change. Notably, these processes are accelerated with the temperature. However, tracking structural relaxation processes through all three phases is experimentally challenging since the onset occurs in a few nanoseconds, while saturation can take significantly longer times (years) under ambient conditions. Within PCM devices, the amorphous state relaxes after RESET, and the observable metrics, such as electrical conductance and threshold-switching voltage, change due to structural relaxation. This process is commonly referred to as drift. <sup>99</sup>

It is commonly agreed that drift correlates with the consumption of midgap defects and bandgap widening due to local reordering, 100 via a slow evolution of the bond network toward structures with chemical order and coordination numbers similar to those of the crystalline phase. This thereby affects the read-out characteristics of PCM devices. In order to quantitatively capture such a commonly measured log t drift behavior in phase-change materials, the relaxation process most likely proceeds such that the defects with lower activation energies are removed first, followed by those with higher activation energies. In the Gibbs approach, relaxation occurs by the removal of pre-existing defect states with different activation energies. Therefore, the distribution of activation energies for the relaxation of defects serves as the parameter that tracks the state of relaxation of the material at any point in time. In an alternate approach, called collective relaxation, 101 the driving force behind this relaxation process arises from the difference between the local energy minima of adjacent states. The essential idea is that the atomic configurations that are frozen during the glass transition relax collectively (Figure 4a). As the system approaches equilibrium, this driving force diminishes, and the activation energy  $E_b = E_s \times (1 - \sum_{i=1}^{n} (t_i))$ that must be overcome for the next relaxation step increases monotonically, resulting in higher energy barriers for subsequent relaxation steps. Here,  $\sum$  quantifies the relaxation state of the glass ( $\sum = 1$  represents an infinitely unrelaxed state, and  $\sum_{i=0}^{\infty} = 0$  indicates that the system is approaching equilibrium). Notably, unlike the Gibbs approach, this model characterizes relaxation with a single activation energy that evolves over time, thus, providing a physically plausible picture of the relaxation process. More recently, using measurements on powdered samples, atomic rearrangements have been linked to the commonly observed relaxation processes in glassesnamely,  $\beta$  and  $\alpha$  relaxations. The  $\beta$  relaxation represents a secondary, faster process that is structurally distinct from the slower  $\alpha$  relaxation. <sup>102</sup>

Another characteristic of phase-change materials is that the read-out behavior is further characterized by a power spectral density that scales inversely with the frequency, leading to the so-called 1/f or flicker noise. The underlying mechanism that leads to flicker noise remains debated, however, doublepotential-based models (see Figure 4b), typically used in the characterization of trapping-detrapping dynamics of carriers in transistor channels, have been proposed. 103,104 Here, units (carriers or atoms) can reversibly toggle with some distribution in the time constants between two energy minima (trap states) separated by a potential barrier W. The general approach to arrive at a spectrum  $S(f) \propto 1/f$  is to assume that there are many Lorentzian/radio-telegraphic noise  $(1/f^2)$  fluctuation events, each with a relaxation time  $\tau_{12/21} = \tau_0 \exp(W_{12/21}/k_bT)$ , where  $\tau_0^{-1}$  is the attempt frequency to surpass the barrier W. If it is then assumed that W is distributed uniformly, then this approach yields a 1/f spectrum. In the intermediate states, however, random-telegraphic noise, where fluctuations are more pronounced between two tractable electronic states, becomes notable. These have a strong dependency on ambient temperature and applied electric field. Read noise is also generally found to increase with the absolute resistance value. Of all the properties of phase-change materials, read-noise is the least explored. In IMC technology, as we will discuss later, the read-noise determines the ultimate limits to achievable compute precision. Consequently, understanding its physics has become more crucial than before.

## 3.5. Property E: Carrier Transport

In most undoped phase-change materials, current—voltage (I-V) measurements show that the crystalline state exhibits a relatively linear (ohmic) response, while the amorphous state demonstrates distinctly nonlinear behavior under applied voltage. <sup>105,106</sup> In the amorphous OFF state, also referred to as the subthreshold regime near room temperature, the current—voltage characteristics reveal multiple field-dependent regimes: a subexponential increase at low fields, an exponential increase at higher fields, and eventually a transition to an even steeper dependence at very high fields. These behaviors can be described using a multiple-trapping model in which charge carriers are repeatedly trapped and released between localized/bound and extended states. This framework invokes transport mechanisms such as Poole and Poole—Frenkel conduction,

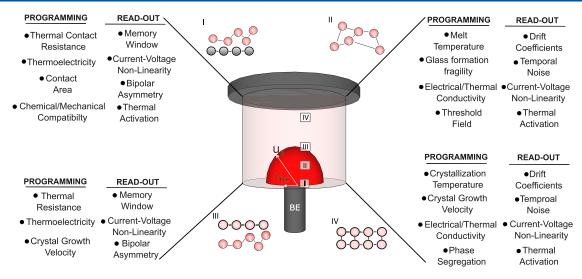

Figure 5. The various structural components associated with a prototypical PCM device. The device consists of various structural components, with conductance varying according to the geometrical scaling of an amorphous dome of size  $(u_a)$  within the bulk phase change material. Additionally, interfaces contribute electrical resistance, which also changes with the dome size. Overall, the device's behavior during programming and read-out operations is governed by various electrical, thermal, chemical, and mechanical properties of the highlighted components. When analyzing and designing computational memory devices, these parameters are carefully considered.

Figure 6. Threshold Switching. (a) A resistor model illustrating a PCM device in series with a load resistor (access device). The programming current and voltage dropped on the PCM device are key parameters governing the RESET and SET operations, respectively. (b) A transmission electron micrograph of a mushroom-type phase-change memory. Insets are TEM images of devices in SET and RESET phase configurations. (c) Illustration of a typical IV characteristic in a PCM device. At low applied voltages, the conductivity of the amorphous off-state is ohmic. As the voltage increases, the conductivity initially rises exponentially and then superexponentially at even higher voltages until the threshold switch occurs. Threshold switching occurs along the load line, determined by the load resistor. The surge in the current flowing through the device can crystallize the amorphous volume.

where thermal emission from ionizable defect centers, modeled as generating a Coulomb potential, plays a central role. In general, a transition from a linear to Poole dependence of current on voltage is observed at low voltages,  $\ln\left(\frac{I}{I_0}\right) = \alpha \cdot V$ . At higher voltages, Poole–Frenkel type behavior is observed, described by  $\ln\left(\frac{I}{I_0}\right) = \beta \cdot \sqrt{V}$  Here, V is the applied voltage, I is the measured current, and the remaining terms represent other measured quantities or constants. Modeling a two-center Coulombic potential in three dimensions helps explain the observed transitions under an applied voltage

(electric field (F)). This electric field, F has been understood to lower the potential barrier or activation energy  $(E_{\rm a})$ , facilitating the release of carriers from bound to free states. The resulting increase in carrier density leads to enhanced electrical conductivity and the transition between different conduction regimes depends on the distance between the two centers. It is also well established that at very high electric fields and low temperatures, transport can occur via thermally assisted tunneling or direct tunneling through the potential barrier, resulting in a stronger field dependence of conductivity. At low temperatures, variable-range hopping becomes the dominant conduction mechanism, as thermal emission of carriers is

significantly suppressed. As in amorphous oxide semiconductors and silicon, <sup>110</sup> the role of tail states in subthreshold transport in prototypical phase-change materials such as GST remains an area requiring deeper understanding. Additionally, the presence of charged defect states suggests that phase-change materials exhibit weaker field-effect behavior under electrostatic gating, since the charges screen the applied electric field. <sup>111</sup> Lastly, note that while the above description holds for typical compositions, it may not always capture a complete picture. Materials such as AIST exhibit deviations from the behavior, for example in the Poole-Frenkel based transport, <sup>107</sup> underscoring the need for further composition dependent investigations of the carrier transport mechanisms. <sup>112</sup>

## 4. PART 3: DEVICE PROPERTIES

Since the atomic arrangements in PCM devices change during programming, they are structurally nonstationary devices. In other words, while the bulk and contact characteristics of standard nanodevices are fixed by fabrication, in PCM devices, these dynamically change during the device operation. Broadly, a PCM device, such as the mushroom type can be described using four components: (I) electrode amor PCM interface, (II) bulk amor PCM volume, (III) amor crys PCM interface, and (IV) bulk crys PCM volume. It has been understood that each component contributes and/or individually governs the various programming and read-out metrics (we will see in a later section that applications can leverage the PCM devices for their read-out, programming characteristics, or both). Therefore, designing a PCM device is both a material selection and an engineering problem, where many parameters are to be optimally engineered. In Figure 5, we have emphasized the key parameters related to an electrical PCM device.

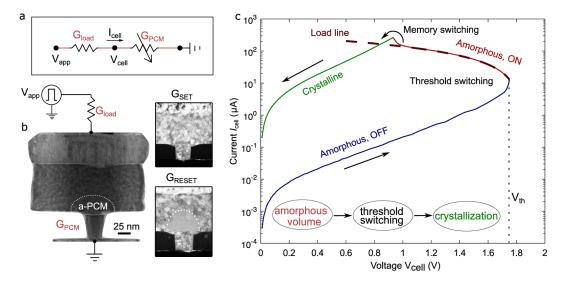

## 4.1. Threshold Switching

Just as the nonlinearity attribute of fragility is so crucial for achieving amorphization, a nonlinear I-V characteristic, is crucial for achieving crystallization. This is a critical feature of PCM technology. Upon reaching a certain voltage, referred to as the threshold switching voltage  $(V_{\rm th})$ , the conductivity of the amorphous phase surges due to a feedback mechanism, leading to a phenomenon known as negative differential conductance,  $^{106,107}$  characterized by a sudden drop in voltage (voltage snapback). For a given material, the threshold voltage scales linearly with its amorphous volume dimensions. However, the absolute values are material-dependent, specified by the band gap dependent threshold field  $(E_{\rm th})$ , leading to  $V_{\rm th} = E_{\rm th} \times u_{\rm a}$ . Binary GeSb compositions are shown to have the smallest threshold field  $^{113}$  in the sub-10 V/ $\mu$ m, compared to GST, in the range of 50 V/ $\mu$ m.

If the current through the device is monitored in voltage mode, as illustrated in Figure 6, the apparent negative differential conductance often corresponds to that of the external load resistor ( $G_{\rm load}$ ) connected in series with the PCM device to cap the current, since the conductance of the PCM device becomes higher than  $G_{\rm load}$  after threshold switching. Within an array configuration, the negative differential conductance is managed by the nonlinear selector device or transistor coupled to the PCM device. The phase immediately after threshold switching is generally termed the amorphous ON state, indicating that while the phase remains amorphous, its electrical conductivity has significantly increased. Persistent current flow through a PCM device in this state for an

adequate duration leads to memory switching, meaning the device transitions to total crystallization, and the I-V characteristic of the amorphous ON state converges with that of the crystalline state.

To gain insight into the significance of nonlinear fielddependent transport, consider a hypothetical situation where the amorphous state exhibits purely ohmic behavior. If the device resistance is  $5 M\Omega$ , and if a mere 5% of the power needed for melting the device (e.g., 900  $\mu$ W) could result in crystallization, a voltage of  $\sqrt{P \cdot R} = 15 \text{ V}$  would be required to induce crystallization. This would clearly make PCM not a usable technology. Another key technological relevance of the highly nonlinear I-V characteristic is the near-infinite read endurance exhibited by the PCM devices. The mechanism behind threshold switching has been a topic of ongoing discussion and remains unclear. Numerous models have been suggested to elucidate this phenomenon in PCM devices; they generally fall into two categories: thermal models, which attribute the switching to an electrothermal instability within the device, and models that propose a purely electronic basis for the switching. In the absence of experimental evidence, there is increasing consensus that models based on filamentation and rupture of crystalline regions are less plausible. More recently, it has been suggested through measurements on high-bandgap chalcogenide materials that threshold switching might be linked to subtle structural rearrangements within the amorphous phase. 114 These rearrangements involve structural motifs with aligned bonds, which increase the density of states around the Fermi level and, in turn, enhance the electrical conductivity. However, these findings have not yet been experimentally validated in terms of I-V characteristics in prototypical phase-change materials, and the similarities of the motifs with the crystalline lattice are still to be confirmed.

## 4.2. Device Failure Modes

State-of-the-art PCM devices can switch reversibly between SET and RESET states over 109 times. Such a number is generally achieved when their stability to electrical and thermal stresses is improved. The main mechanism that affects reversible switching between conductance states arises from both elemental and phase segregation, which occurs within the phase-change materials due to crystallization during the SET operation and melting during the RESET operation. The instability is often thermodynamic, where, for instance, Tebased amorphous eutectic compositions can separate into Tepoor and Te-rich phases within the device's active region. This is why stoichiometric compounds are preferred, as they are more stable (see Figure 7a). However, issues can still arise during melting; for example, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> does not melt congruently, but phase segregates into a Te-rich liquid phase and a Ge-rich solid phase below its melting point.

These effects are intensified by the large electrical and thermal gradients within the device (see Figure 7b), leading to the electrothermal migration of elements, 115,116 which is commonly observed and modeled by

$$\frac{\partial C}{\partial t} = \nabla \cdot \left[ D \left( \underbrace{\nabla C}_{\text{concentration gradient}} + \underbrace{\frac{Z^*}{kT} C \nabla V}_{\text{field gradient}} + \underbrace{\frac{\alpha C \nabla \ln T}{\text{thermal gradient}}} \right) \right]$$

In this equation, C represents the atomic concentration, D denotes the diffusivity that varies with phase and temperature,

Figure 7. Modes of device failure. (a) Nonstoichiometric materials, such as eutectic compositions, can undergo phase segregation during programming operations. (b) High electrothermal fields during programming can induce ion migration, leading to elemental segregation, such as the accumulation of Sb near the electrode. (c) Cyclic volume changes in the device, due to differences in atomic density between the amorphous and crystalline states, can create localized stresses, potentially causing delamination or void formation. Mechanisms (a) and (b) often result in the device being stuck in the SET state, while mechanism (c) leads to the device being in an electrically open state.

$Z^*$  is the effective charge, and  $\alpha$  signifies the thermodiffusion coefficient for each species. The terms enclosed in brackets describe the atomic flux: the first term arises from Fick's first law, indicating diffusion driven by concentration gradients. The second term accounts for diffusion influenced by an electric field, while the third term captures the effect of diffusion due to temperature gradients. In Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, the segregation of positively charged Sb toward the bottom electrode, and negatively charged Te toward the top electrode, is a commonly noted failure-motion. This motion is attributed to the higher electronegativity (5.49 eV) of Te compared to Ge and Sb (4.6 eV and 4.85 eV). These mechanisms also explain the dependency of programming on the polarity of the voltage (i.e., the good or bad programming polarity 117) in the electrical phase-change devices: under bad polarity, the device shows poor memory window and very limited endurance. Single elemental Sb-based PCM devices have been suggested to combat phase segregation-induced failures, however, their endurance limits are yet to be investigated.<sup>31</sup>

Another prominent failure mechanism in devices is related to the change in mass density with the phase transformation. SET to RESET transitions can incur severe volume shrinkage (6.5–9.6%), due to the tighter atomic packing in the amorphous phase. Consequently, this causes void formation in the device, which finally limits the cyclability (see Figure 7c). In cyclic switching experiments, low programming currents, followed by device failure are commonly attributed to void formation. Material compositions with high thermal stability, and minimal-density change characteristics, such as oxygen-incorporated GeTe, have been suggested to reduce such a stress-induced failure mode.

These compositions, however, can be prone to phase segregation. The contact between the phase-change region and the adjacent dielectric (e.g., silicon oxide, silicon nitride) is yet another fundamental concern, since chalcogens show a strong bonding preference for each other over the dielectric for reasons relating to the minimization of strain and surface energies. This results in poor adhesion, <sup>120</sup> and consequently, physical peeling of the phase change film during programming, when the active region is hot. Adhesion with the chalcogenide material is typically achieved with interfacial layers including metal layers and carbon-based films. <sup>76</sup>

#### 4.3. Nonidealities

A key challenge when computing with PCM devices is the temporal variations in the device conductances and the precision of programming a numeric value to a conductance state.

Consequently, this affects the accuracy of the computation.

123,124

The temporal variations arise from intrinsic material physics. The conductance of a programmed state as a function of time can be expressed as

$$G(t, T) = G_0 \cdot \exp\left(-\frac{E_a(t, T)}{K_b T}\right) + \underbrace{\eta_G(t)}_{\text{read noise}}$$

Here,  $G_0$  is the conductance prefactor and  $E_a$  is the activation energy for charge transport. The conductance drift arises from structural relaxation in the RESET state, where the device conductance decreases with time:  $G(t) = G(t_0) \left(\frac{t}{t_0}\right)$  $G(t_0)$  is the conductance measured at time  $t_0$ , and  $\nu$  is the drift exponent. The drift coefficient is both material- and RESET state-dependent, typically in the range of 0.1-0.15. For example, if at t = 1 s the device conductance reads 200  $\mu$ S, it will read 143 and 71  $\mu$ S after 10 and 1000 s, respectively. We also note that in measurements of as-deposited amorphous films, the power law can be extended to include a virtual age  $t_s$ of the sample:  $G(t) = G(t_0) \left(\frac{t+t_s}{t_0}\right)^{-\nu}$ . Here,  $t_s$  represents the time or extent to which the film has drifted before measurement, during deposition and storage. Care must be taken in reporting  $\nu$  values in such cases, as they can be misinterpreted when fitted with the standard power law form.

The second contribution arises from the variations in ambient temperature. Because, phase-change materials are typically low-bandgap semiconductors (0.40–0.90 eV), the variations in the ambient temperature can lead to pronounced fluctuations in the conductance. This is due to the thermally activated nature of electrical transport and is governed by the activation energy. This behavior is again state-dependent. For example, the crystalline state of GST has  $E_a$  of 0.04–0.12 eV, while the amorphous state 0.20–0.30 eV. Therefore, the amorphous phase configurations are more susceptible to temperature variations. <sup>125</sup>

The third contribution to conductance fluctuation is from additive 1/f noise. Similar to the conductance drift, 1/f shows a strong state dependency. The spectral density of the full RESET state can be more than 2 orders of magnitude higher than the full SET state. More generally, the magnitude of noise has a normal distribution with one standard deviation ranging between 5-10% of the mean conductance in the resting state.

Figure 8. Nonidealities in computational PCM. (a) Device data after programming exhibits variability, depicted by wide distributions in analogue conductance states (each unique state represented in a different color) due to imprecise programming and temporal changes in conductance (top panel). This behavior is governed by additive read noise and multiplicative conductance drift. Elevated ambient temperature increases device conductivity through thermal carrier excitation and accelerates structural relaxation (middle panel). Returning to room temperature markedly reduces mean conductance values (bottom panel). (b) Conductance measured in negative voltage polarity as a function of conductance measured in positive voltage polarity. Bipolar current asymmetry in the device results in differences in the absolute values of the current based on the voltage polarity. Band diagrams of the PCM device. The device exhibits Schottky barriers for holes at both interfaces, with the amorphous—crystalline interface having a higher barrier than the electrode—amorphous interface. The bias polarity changes the band profile.

Figure 9. Device architectures. A schematic illustrating various device concepts optimized using two primary strategies: contact area reduction with the phase change material, and volumetric minimization of the phase change material.

Other sources of compute imprecision include the programming noise and the dependency of the conductance at low fields on the voltage polarity. The former determines the precision with which numerical values can be mapped into the conductance values of the PCM devices. A closed-loop programming scheme is generally used in the mapping operation. Here, programming pulses are iteratively shaped to program the conductance of PCM devices within some error margins. It has been shown that the 1/f spectral characteristic of read noise has a significant effect on the near-term temporal evolution of the conductance distribution during programming. That is, the convergence of programming to a target conductance value is fundamentally limited by read

noise, which has a time-dependent distribution  $(\eta_G(t))$ . Thus, a noise-free programmed state is  $G(t)=Z-\eta_G(t)$ , where Z is the actual programmed conductance value that may or may not be within the defined tolerance margins. Due to additive read noise, the conductance values tend to be uniformly distributed around the target conductance at the time of convergence. However, over time, read-out measurements taken after convergence reveal that these states begin to diverge from their intended values. More generally, at a constant temperature, and time  $t_c$  from the last iterative programming pulse it can be shown that the ultimate precision of programming is twice the variance of  $\eta_G(t_c)$ . All the above-described nonideal behaviors are shown in Figure 8a.

The conductance dependence on polarity arises when  $G = \underbrace{f(V, \operatorname{sign}(V))}_{\text{current asymmetry}}$ . This occurs when there are physical

asymmetries in the device, such as when the charge transport barrier heights and/or the contact areas differ at the interfaces between the forcing and sensing current leads. In a GST-based mushroom-type PCM device, Schottky barriers for holes appear at both interfaces, with the barrier of the amorphouscrystalline interface being greater than that of the electrodeamorphous interface. When a positive bias is applied to the top electrode relative to the bottom electrode, the configuration resembles back-to-back diodes, with the amorphous-crystalline interface being reverse-biased and the electrodeamorphous interface being forward-biased. Conversely, this configuration is reversed when the polarity is negative. Consequently, a larger current flows when the dominant diode, namely, the amorphous-crystalline interface, is forwardbiased. This scenario occurs when the applied bias polarity is negative. This dependency on voltage leads to numeric errors when performing matrix-vector multiplications (MVMs) with signed inputs (see Figure 8b).

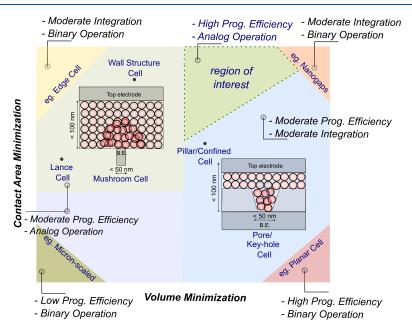

#### 4.4. Cell Geometry

PCM technology demands relatively high currents and power for programming because it necessitates heating of the materials to induce phase transitions. While the SET operation does require surpassing the threshold voltage, the power (and current) used in the SET pulse is typically 40-80% of that required for the RESET pulse. Therefore, the RESET pulse is the primary concern when evaluating whether the access device can provide enough current. In contrast, the SET pulse usually determines the write speed of the PCM technology. Since switching in the devices is governed by heating, two mechanisms are expected to dictate the efficiency with which heating occurs: the efficiency of Joule heat generation in the phase-change film and the resistance to the dissipation of heat, out of the phase-change film. This has led to the development of two primary strategies in device engineering: minimizing the contacts and reducing the phase-change material volume (see Figure 9). By significantly shrinking the bottom electrode or the phase-change material volume, the current density can increase, ensuring that the majority of the electric power is dissipated either at the interface between the phase-change material and the bottom electrode or within the bulk of the phase-change material. This power dissipation results in a temperature rise, 128 which is then balanced by heat being transported away from the device. Indeed, echoing Dennard's principles of transistor scaling, reducing the size of PCM cells and their contacts has resulted in performance improvement. Since the introduction of the first memory chip, the size of PCM devices has reduced by a factor of 1000, accompanied by a similar reduction in switching currents and a 10-fold decrease in switching voltages. Today, exploratory lab scale devices feature RESET currents below 10 µA at a feature size of 5 nm. 45,129 In the realm of commercial technology, where PCM devices are constructed as large arrays, the technology satisfies modest RESET currents of  $\sim 200 \,\mu\text{A}$ , at a feature size of 40 nm.

Combining the simplified Fourier heat transfer equation with the Joule heating equation gives the formula  $T_{\rm a} = T_{\rm amb} + \underbrace{I_{\rm melt}^2 \times R_{\rm ON}}_{\rm Joule\,heating} \times \underbrace{R_{\rm TH}}_{\rm heat\,dissipation}$ , which outlines the

programming efficiency. Here,  $T_a$  represents the temperature at the 'hotspot' or actively heated region, significantly

increasing from the ambient temperature  $T_{\rm amb}$  due to power dissipation through an electrical resistance  $R_{\rm ON}$ . This is the socalled dynamic ON resistance, which encompasses resistive contributions from the melt volume, the crystalline phasechange region, and the electrodes in series. 130 Notably, both  $R_{\rm ON}$  and the thermal resistance  $R_{\rm TH}$  strongly depend on the device's geometry and the phase configuration of the amorphous marks. At first approximation,  $I_{melt}$  thereby decreases proportionally from phase-change material electrode contact and phase-change material volume reductions since both these schemes increase the electrical and thermal resistances. Examples of contact area minimized devices include, mushroom-type. The contact area is more commonly defined by the critical dimension achievable with lithography. Sublithographic electrodes (defined as  $\eta \times F$ , where  $\eta < 1$ ) can be defined with a thin film based edge type contacts, such as in edge-type devices, 131 as well in ring electrode type 4. mushroom-type devices. In the latter, the heater electrode consists of a thin ring of metal surrounding a center dielectric core, which reduces both the RESET current and the variability by decreasing the effective area. Volume minimized devices, include the pore type,<sup>37</sup> bridge or line,<sup>46</sup> and confined or pillar type cells.4

The cell designs discussed so far are known as self-heating types, primarily because the hot spot is located within the phase-change material itself. An alternative design uses a bottom electrode, referred to as a heater, to generate the heat required for the phase transition in the adjacent phase-change material. 44 In these designs, the heater primarily contributes to  $R_{\rm ON}$ , rather than the phase-change channel. As a result, the active heating region is within the heater itself, not at the interface between the bottom electrode and the phase-change material or within the phase-change material. Examples of this architecture include lance-type and wall-structured cells, where the bottom electrode is designed to be resistive and typically longer than in mushroom-type cells. It is also worth noting that in mushroom-type devices if the phase-change material has very low resistivity or the heater has higher resistivity, the devices would not operate as a self-heating type.

Extreme contact and volume minimization, however, pose challenges for large-scale integration in BEOL. The former approach is limited by lithographic and process capabilities, while the latter approach suffers from fabrication challenges and elemental segregation. Both approaches can result in high variability and low reliability when approaching lithographically defined dimensions in the tens of nanometers, thus limiting large-scale manufacturability. Furthermore, improvements in PCM-based IMC hinge on achieving not only high device density and low programming currents but also the capability for multilevel or analogue programming. 15 This is fundamentally required for more precise mapping of numeric values into the nonvolatile conductance states of devices. Therefore, while certain device architectures may achieve programming energies in the tens of femtojoules from extreme reductions in material volume, such miniaturization can impair the analogue programming capabilities due to the minimal material available for melting. Devices featuring nanogap, edgetype, and confined structures, such as Intel Optane, exemplify this limitation and function in binary mode due to their small switchable volume. 45,131 Based on the discussion above, it could be tempting to consider that larger devices with smaller contact areas and increased volume could enable analogue programming. Yet, despite their potentially suitable volume for

this purpose, their larger physical size and the associated high thermal resistances could lead to slower quenching rates, challenging the implementation of precise melt-quench dynamics that is needed for analogue programming. This would be in addition to their poor integration density. In addition to optimizing programming currents and analogue programming capabilities, it is crucial to design a cell architecture with moderate threshold voltages. These voltages should be substantially higher than the noise floor of circuits yet small enough to align with the operating points of individual access devices. For instance, in bridge cells, enhancing programming currents and analogue efficacy can be achieved by extending the length of the phase-change material channel. However, this extension leads to higher threshold voltages, as the required field scales proportionally with the length of the amorphous mark.

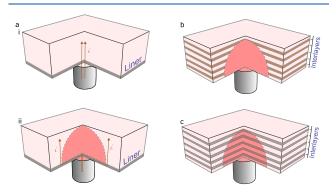

## 4.5. New Device Concepts

There have been two main approaches to improving PCM devices. The first approach involves material engineering, such as selectively doping elements into a host material or exploring new materials<sup>31</sup> like Sb. The second approach involves design engineering of the device. For example, the projected PCM. These devices have a noninsulating projection (liner) segment (see Figure 10a), optimally engineered in

Figure 10. Schematic illustration of emerging PCM device concepts. (a) A projected-type PCM device. (i) Illustrates the phase configuration in the SET state, where the current flows from the bottom electrode into the crystalline phase-change material. (ii) Illustrates the phase configuration in the RESET state, where a substantial portion of the current bypasses the amorphous volume by flowing through the liner, thus masking the nonideal characteristics associated with the amorphous phase. (b) A superlattice-type PCM. The phase-change material consists of highly oriented thin films of two different materials that repeat periodically. In the active region, these thin films intermix during RESET, whereas during the SET operation, they are suggested to separate into distinct phases. (c) A heterostructure-type PCM. The functional layer consists of ultrathin phase-change films separated by noninsulating layers. During programming, only the phase-change layer undergoes structural changes.

electrical properties that run parallel to the phase-change material segment. During the programming process, the projection segment has minimal impact on device operation due to the highly nonlinear I-V characteristics of phase-change materials. However, the projection segment decouples the read-out from the noisy electrical properties of the amorphous phase configurations of the phase-change material. Thus, in effect, the device read-out characteristics become dictated by the properties of the stable projection segment.

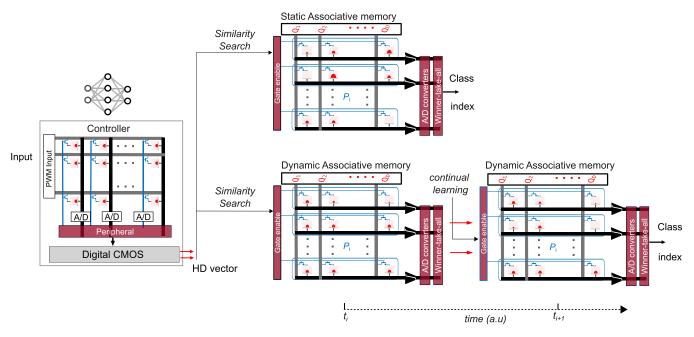

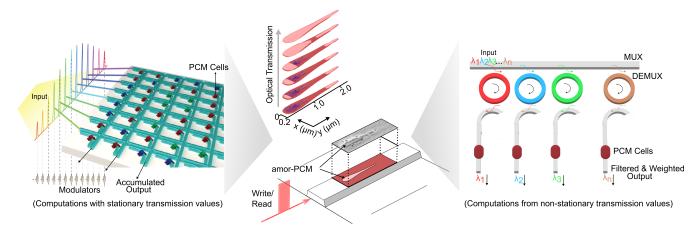

Individual lateral (bridge cell) projected PCM devices have demonstrated in-memory scalar multiplication with an arithmetic precision equivalent to 8-bit fixed-point.<sup>57</sup> Similarly, individual confined-type have shown improvements in computational precision. 135 However, both of these structures pose challenges for large-scale array fabrication. Lateral devices, aside from their large footprint, are susceptible to etch damage on the sidewalls, while confined cells struggle with filling long trenches. Both issues contribute to significant device-to-device variability. Indeed for these reasons, large array demonstrations have been made with mushroom type devices: projectedmushroom type devices have been integrated onto multitile IMC chips fabricated in 14 nm CMOS technology, achieving drift and noise reduction, thus improving inference accuracies.<sup>76</sup> However, although mushroom type device geometry offers a large programming window and is manufacturable, the efficacy of projection itself is fundamentally lesser compared to geometries like the bridge cells, where the current flows parallel to the liner. Research is ongoing to develop manufacturable device structures that achieve also higher projection efficiencies.