# **OPEN**

SUBJECT AREAS: TWO-DIMENSIONAL MATERIALS

**ELECTRONIC DEVICES**

ELECTRONIC PROPERTIES AND MATERIALS

ELECTRICAL AND ELECTRONIC ENGINEERING

Received 15 September 2014

Accepted 12 February 2015

Published 11 March 2015

Correspondence and requests for materials should be addressed to L.B. (balicas@magnet. fsu.edu)

# Hall and field-effect mobilities in few layered p-WSe<sub>2</sub> field-effect transistors

N. R. Pradhan<sup>1</sup>, D. Rhodes<sup>1</sup>, S. Memaran<sup>1</sup>, J. M. Poumirol<sup>1</sup>, D. Smirnov<sup>1</sup>, S. Talapatra<sup>2</sup>, S. Feng<sup>3</sup>, N. Perea-Lopez<sup>3</sup>, A. L. Elias<sup>3</sup>, M. Terrones<sup>3</sup>, P. M. Ajayan<sup>4</sup> & L. Balicas<sup>1</sup>

<sup>1</sup>National High Magnetic Field Laboratory, Florida State University, Tallahassee-FL 32310, USA, <sup>2</sup>Physics Department, Sourthern Illinois University, Carbondale-IL 62901-4401, USA, <sup>3</sup>Department of Physics, Department of Materials Science and Engineering and Materials Research Institute, The Pennsylvania State University, University Park, PA 16802, USA, <sup>4</sup>Department of Mechanical Engineering and Materials Science, Rice University, Houston, TX 77005 USA.

Here, we present a temperature (T) dependent comparison between field-effect and Hall mobilities in field-effect transistors based on few-layered WSe<sub>2</sub> exfoliated onto SiO<sub>2</sub>. Without dielectric engineering and beyond a T-dependent threshold gate-voltage, we observe maximum hole mobilities approaching 350 cm²/Vs at T = 300 K. The hole Hall mobility reaches a maximum value of 650 cm²/Vs as T is lowered below  $\sim$ 150 K, indicating that insofar WSe<sub>2</sub>-based field-effect transistors (FETs) display the largest Hall mobilities among the transition metal dichalcogenides. The gate capacitance, as extracted from the Hall-effect, reveals the presence of spurious charges in the channel, while the two-terminal sheet resistivity displays two-dimensional variable-range hopping behavior, indicating carrier localization induced by disorder at the interface between WSe<sub>2</sub> and SiO<sub>2</sub>. We argue that improvements in the fabrication protocols as, for example, the use of a substrate free of dangling bonds are likely to produce WSe<sub>2</sub>-based FETs displaying higher room temperature mobilities, i.e. approaching those of p-doped Si, which would make it a suitable candidate for high performance opto-electronics.

ield-effect transistors (FETs) based on exfoliated transition-metal dichalcogenides (TMDs)<sup>1-4</sup> were shown to be promising as low-power switching devices and therefore as potential components for high-resolution liquid crystal and organic light-emitting diode displays, particularly in their multi-layered form<sup>5</sup>. Bulk transition metal dichalcogenides (TMD) crystallize in the "2H" or trigonal prismatic structure (space group  $P6_3/mmc$ ), in which each transition metal is surrounded by six chalcogenide atoms defining two triangular prims. Extended planes, which are weakly or van der Waals coupled, result from the tessellation of this basic unit. Contiguous planes are shifted with respect to one another (along both the a- and the b-axis), therefore the unit cell is composed of two planes with a transition metal dependent inter-layer distance c. The covalently bonded layers are expected to display high crystallinity, although as in graphite/graphene, one can expect crystallographic mosaicity between planes stacked along the c-axis. Similarly to graphite, compounds such as MoS<sub>2</sub>, WS<sub>2</sub>, etc., are exfoliable layered materials characterized by a weak inter-planar van der Waals coupling<sup>1</sup>. In contrast to graphene, they exhibit indirect band gaps ranging from ~1 to ~2 eV which become direct in single atomic-layers<sup>6</sup>, making them promising candidates for applications.

Early studies<sup>7</sup> on field-effect transistors (FETs) based on bulk WSe<sub>2</sub> single-crystals using parylene as the gate dielectric, revealed room temperature field-effect mobilities approaching those of p-Si<sup>8</sup> but with a small current ON/OFF ratio. Subsequent investigations<sup>9</sup> on mechanically exfoliated MoS<sub>2</sub> flakes composed of tenths of atomic layers and SiO<sub>2</sub> as the gate dielectrics, revealed considerably lower mobilities (10–50 cm²/Vs), suggesting either a remarkable difference in mobilities between MoS<sub>2</sub> and WSe<sub>2</sub> or that an inadequate choice of gate dielectrics can hinder their performance. More recently<sup>10</sup>, it was suggested that field-effect carrier mobilities surpassing 1000 cm²/Vs could be achieved in dual gated, single-layer MoS<sub>2</sub> FETs through the use of a top gate composed of a high- $\kappa$  dielectric such as HfO<sub>2</sub>. Nevertheless, it was argued that this is an overestimated mobility value due to the capacitive coupling between both top and back gates<sup>11</sup>, a fact that is supported by subsequent reports of much smaller mobilities in similar devices when the gate capacitance is extracted from a Hall-effect study<sup>12,13</sup>. It was also recently argued that remote phonons from dielectric layers such as HfO<sub>2</sub>, can limit carrier mobility and would require the use of an interfacial layer to absorb most of the vibrational energy<sup>14</sup>. Nevertheless, these observations already led to the development of integrated circuits based on single<sup>15</sup>- and on bi-layered MoS<sub>2</sub>. Recent studies in both single- and double- layered MoS<sub>2</sub> revealed Hall mobilities which increase strongly with gate voltage, saturating at maximum values between ~200 and ~375 cm²/Vs at low temperatures<sup>17</sup>. In multi-layered MoS<sub>2</sub>

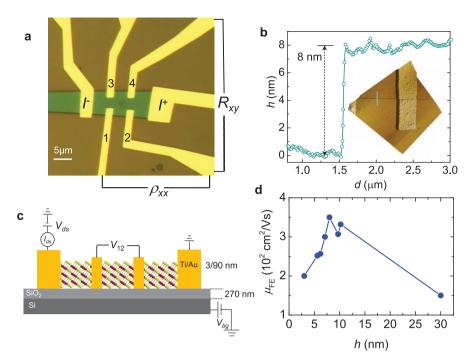

Figure 1 | (a) Micrograph of the one of our WSe<sub>2</sub> field-effect transistors on a 270 nm thick SiO<sub>2</sub> layer on p-doped Si. Contacts, (Ti/Au) used to inject the electrical current ( $I_{ds}$ ), are indicated through labels  $I^+$  (source) and  $I^-$  (drain), while the resistivity of the device  $\rho_{xx}$  was measured through either the pair of voltage contacts labeled as 1 and 2 or pair 3 and 4. The Hall resistance  $R_{xy}$  was measured with an AC excitation either through the pair of contacts 1 and 3 or 2 and 4. Length 1 of the channel, or the separation between the current contacts, is  $I = 15.8 \, \mu m$  while the width of the channel is  $w = 7.7 \, \mu m$ . (b) Height profile (along the blue line shown in the inset) indicating a thickness of 80 Å, or approximately 12 atomic layers for the crystal in (a). Inset: atomic force microscopy image collected from a lateral edge of the WSe<sub>2</sub> crystal in (a). (c) Side view sketch of our field-effect transistor(s), indicating that the Ti/Au pads contact all atomic layers, and of the experimental configuration of measurements. (d) Room temperature field-effect mobility  $\mu_{FE}$  as a function of crystal thickness extracted from several FETs based on WSe<sub>2</sub> exfoliated onto SiO<sub>2</sub>. The maximum mobility is observed for ~12 atomic layers.

the Hall mobility has been found to increase from  $\sim 175$  cm<sup>2</sup>/Vs at 60 K to 311 cm<sup>2</sup>/Vs at T=1 K at back-gate voltages as large as 100 V<sup>18</sup>. However, marked discrepancies were reported between the measured field-effect and the Hall mobilities<sup>17</sup>, which at the light of Refs. 11–13 could be attributed to underestimated values for the gate capacitances.

Similarly to past research on graphene, much of the current effort on TMD-based FETs is focused on understanding the role played by the substrates, annealing conditions and the work functions of the metallic contacts. For example, it was recently argued that most of the above quoted mobilities are determined by the Schottky barriers at the level of the current contacts which limits the current-density that can be extracted from these transistors. The authors of Ref. 19 argue that small Schottky barriers, and therefore nearly Ohmic contacts in TMD based FETs, can only be achieved through the use of metals with small work functions such as Sc. Furthermore, due to the detrimental role played by the SiO<sub>2</sub> substrates, Ref. 19 finds that the highest mobilities (~175 cm<sup>2</sup>/Vs) can be achieved in FETs built on  $\sim$ 10 nm ( $\sim$ 15 layers) thick flakes. Thickness dependent mobilities were also recently reported for MoS<sub>2</sub> based transistors using polymethyl methacrylate (PMMA) as the gate dielectrics<sup>20</sup>. High performance TMD-based FETs have been claimed to have the potential to make a major impact in low power optoelectronics<sup>5,21–23</sup>. Here, to evaluate this assertion, we study and compare field-effect and Hall mobilities in field-effect transistors based on few-layered WSe2 exfoliated onto SiO2, finding that they can display room temperature hole-mobilities approaching those of hole-doped Si<sup>8</sup> with a large ON to OFF ratio (>106) and sharp subthreshold swings (ranging from 250 and 140 mV per decade). This observation is remarkable given that i) carrier mobility is expected to be limited by the scattering from intrinsic24 as well as substrate phonons, ii) the Schottky barriers at the contacts have yet to be optimized, and as

we show iii) the presence of charge traps and disorder at the interface between  $WSe_2$  and  $SiO_2$  should limit the carrier mobility. Improvements in device fabrication, can lead to improved performance with respect to these values open promising prospects for optoelectronic applications.

#### **Results and Discussion**

Figures 1a and b show respectively, a micrograph of a typical device, whose experimental results will be discussed throughout this manuscript, and the sketch of a four-terminal configuration for conductance measurements. Current source  $I^+$  and drain  $I^-$  terminals, as well as the pairs of voltage contacts 1, 2 and 3, 4 are indicated. As shown below, this configuration of contacts allows us to compare electrical transport measurements performed when using a 2-contact configuration (e.g.  $\mu_{FE}$ ) with a 4-terminal one (e.g.  $R_{xy}$  or the Halleffect). Figure 1b shows an atomic force microscopy profile and image (inset) from which we extract a flake thickness of ~8 nm, or approximately 12 atomic layers. We chose to focus on multilayered FETs because our *preliminary* observations agree with those of Refs. 19, 20, indicating that the highest mobilities are observed in flakes with thicknesses between  $\sim$ 10 and 15 atomic layers as shown in Fig. 1d. In addition, as argued in Ref. 5 multilayered flakes should lead to thin film transistors yielding higher drive currents when compared to transistors based on single atomic layers, possibly making multilayered FETs more suitable for high-resolution liquid crystal and organic light-emitting diode displays<sup>5</sup>. Our flakes were mechanically exfoliated and transferred onto a 270 nm thick SiO<sub>2</sub> layer grown on p-doped Si, which is used as a back gate. Throughout this study, we focus on devices with thicknesses ranging from 9 to 15 layers. Three of the devices were annealed at 150 °C, under high vacuum for 24 h, which as reported in Ref. 17, yields higher mobilities particularly at low temperatures. We found very similar overall

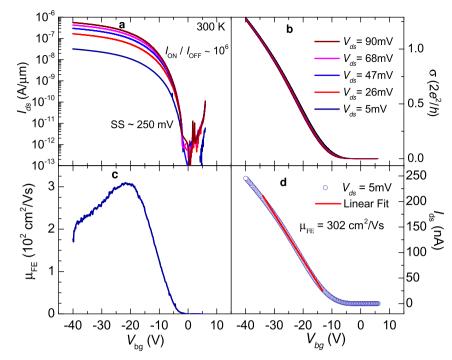

Figure 2 | (a) Current  $I_{\rm ds}$  in a logarithmic scale as extracted from a WSe<sub>2</sub> FET at  $T=300\,$  K and as a function of the gate voltage  $V_{\rm bg}$  for several values of the voltage  $V_{\rm ds}$ , i.e. respectively 5 (dark blue line), 26 (red), 47 (blue), 68 (magenta), and 90 mV (brown), between drain and source contacts. Notice that the ON/OFF ratio approaches  $10^6$  and subthreshold swing SS  $\sim$ 250 mV per decade. We evaluated the resistance  $R_{\rm c}$  of the contacts by performing also 4 terminal measurements (see Fig. 7 a below) through  $R_{\rm c} = V_{\rm ds}/I_{\rm ds} - \rho_{xx} 1/w$ , where  $\rho_{xx}$  is the sheet resistivity of the channel measured in a four-terminal configuration. We found the ratio  $R_{\rm c}/\rho_{xx} \approx 20$  to remain nearly constant as a function of  $V_{\rm bg}$ . (b) Conductivity  $\sigma = S1/w$ , where the conductance  $S = I_{\rm ds}/V_{\rm ds}$  (from (a)), as a function of  $V_{\rm bg}$  and for several values of  $V_{\rm ds}$ . Notice, how all the curves collapse on a single curve, indicating linear dependence on  $V_{\rm ds}$ . As argued below, this linear dependence most likely results from thermionic emission across the Schottky-barrier at the level of the contacts. (c) Field effect mobility  $\mu_{\rm FE} = (1/c_{\rm g} d\sigma/dV_{\rm bg}$  as a function of  $V_{\rm bg}$ , where  $c_{\rm g} = \varepsilon_{\rm r} \varepsilon_{\rm o}/d = 12.789 \times 10^{-9}$  F/cm² (for a  $d=270\,$  nm thick SiO<sub>2</sub> layer). (d)  $I_{\rm ds}$  as a function of  $V_{\rm bg}$  when using an excitation voltage  $V_{\rm ds} = 5\,$  mV. Red line is a linear fit whose slope yields a field-effect mobility  $\mu_{\rm FE} \approx 300\,$  cm²/Vs.

response among the non-annealed samples, as well as among the annealed ones.

Figure 2a shows the extracted field-effect current  $I_{ds}$  as a function of the back gate voltage  $V_{\rm bg}$  for several fixed values of the voltage  $V_{\rm ds}$ across the current contacts, i.e. when using a 2-terminal configuration. From initial studies<sup>7</sup>, but in contrast with Refs. 25,26, WSe<sub>2</sub> is expected to show ambipolar behavior, i.e. a sizable current resulting from the accumulation of either electrons or holes at the WSe<sub>2</sub>/SiO<sub>2</sub> interface due to the electric field-effect. Although we have previously observed such a behavior, all FETs studied here show a rather modest electron current (i.e. saturating at  $\sim 10^{-8}$  A) at positive  $V_{\rm bg}$  values in contrast also with samples covered with Al<sub>2</sub>O<sub>3</sub>, see Ref. 26. Therefore our samples behave as if hole-doped (i.e. sizeable currents only for negative gate voltages). At room temperature the minimum current is observed around  $V_{\rm bg} \approx 0 \, \text{ V}$  while the difference in current between the transistor in its "ON"-state with respect to the OFF- one (on/off ratio) is  $>10^6$ . For all measurements, the maximum channel current was limited in order to prevent damaging our FETs. The subthreshold swing SS is found to be ~250 mV per decade, or ~3.5 times larger than the smallest values extracted from Si MOSFETs at room temperature. Figure 2b shows the conductivity  $\sigma = I_{ds} 1/V_{ds} w$  (from a), as a function of  $V_{\rm bg}$  for several values of  $V_{\rm ds}$ . As indicated in the caption of Fig. 1 the separation between the current contacts, is l = 15.8  $\mu$ m while the width of the channel is  $w = 7.7 \mu$ m. As seen, all curves collapse on a single curve indicating linear behavior, despite the claimed role for Schottky barriers at the level of contacts<sup>19</sup>. See also the Supplemental Information section for linear current-voltage characteristics for the range of excitation voltages used. Figure 2c: the field-effect mobility  $\mu_{FE}$  can be evaluated in the standard way by normalizing by the value of the gate capacitance ( $c_{\rm g} = 12.789 \times$

$10^{-9}$  F/cm²) the derivative of the conductivity with respect to  $V_{\rm bg}$ . As seen,  $\mu_{\rm FE}$  increases sharply above  $V_{\rm bg}\approx 2$  V reaching a maximum of  $\sim 305$  cm²/Vs at  $V_{\rm bg}\sim -20$  V, decreasing again beyond this value. Alternatively, the mobility can be directly evaluated through the slope of  $I_{\rm ds}$  as a function of  $V_{\rm bg}$  in its linear regime, and by normalizing it by the sample geometrical factors, the excitation voltage  $V_{\rm bg}$  and the gate capacitance  $c_{\rm g}$ , yielding a peak value  $\mu_{\rm FE}\approx 302$  cm²/Vs. We have observed  $\mu_{\rm FE}$  values as high as 350 cm²/Vs (see results for sample 2 below). These values, resulting from two-terminal measurements, are comparable to those previously reported by us for multi-layered MoS<sub>2</sub>, where we used a four-terminal configuration to eliminate the detrimental role played by the less than ideal contacts²7.

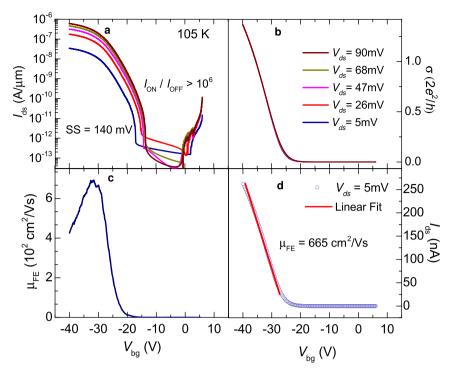

Figures 3a, b, c, and d show respectively,  $I_{ds}$  as a function of  $V_{bg}$  for several values of  $V_{ds}$ , the corresponding conductivities  $\sigma$  as a function of  $V_{\rm bg}$ , and the resulting field-effect mobility as previously extracted through Figs. 2c and d. All curves were acquired at T =105 K. As seen, at lower temperatures  $\sigma(T, V_{bg})$  still shows a linear dependence on  $V_{ds}$  although lower Ts should be less favorable for thermally activated transport across Schottky barriers. In fact, we collected similarly linear data sets at T < 105 K. At T = 105 K,  $\mu_{FE}$  displays considerably higher values, i.e. it surpasses 650 cm<sup>2</sup>/ Vs (accompanied by a reduction in the SS down to  $\sim$ 140 mV per decade). However, as seen in Fig. 3a, lower temperatures increase the threshold gate voltage  $V_{\text{bg}}^{\text{t}}$  required for carrier conduction. Below we argue that this is the result of a prominent role played by disorder and/or charge traps at the interface between WSe<sub>2</sub> and SiO<sub>2</sub> instead of just an effect associated with the Schottky barriers. Large Schottky barriers are expected to lead to non-linear current  $I_{ds}$  as a function of the excitation voltage  $V_{ds}$  characteristics, with a sizeable  $I_{ds}$  emerging only when  $V_{ds}$  surpasses a threshold value determined by the char-

Figure 3 | (a) Current  $I_{\rm ds}$  in a logarithmic scale as extracted from the same WSe<sub>2</sub> FET in Fig. 2 at T=105 K and as a function of the gate voltage  $V_{\rm bg}$  for several values of the voltage  $V_{\rm ds}$ , i.e. respectively 5 (dark blue line), 26 (red), 47 (magenta), 68 (dark yellow), and 90 mV (brown). Notice that the ON/OFF ratio still approaches 10°. (b) Conductivity σ as a function of  $V_{\rm bg}$  for several values of  $V_{\rm ds}$ . Notice that even at lower  $T_{\rm s}$  all the curves collapse on a single curve. Notice how the threshold gate voltage  $V'_{\rm bg}$  for conduction increases from  $\sim$ 0 V at 300 K to  $\sim$ 15 V at 105 K. Below, we argue that the observation of, and the increase of  $V'_{\rm bg}$  as T is lowered, corresponds to evidence for charge localization within the channel. (c) Field effect mobility  $\mu_{\rm FE} = (1/c_{\rm g}) \, d\sigma / dV_{\rm bg}$  as a function of  $V_{\rm bg}$ , (d)  $I_{\rm ds}$  as a function of  $V_{\rm bg}$ , when using an excitation voltage  $V_{\rm ds} = 5$  mV. Red line is a linear fit whose slope yields a field-effect mobility  $\mu_{\rm FE} \approx 665$  cm²/Vs.

acteristic Schottky energy barrier  $\phi$ , as seen for instance in Ref. 28. But according to Figs. 2b and 3b,  $\sigma$  is basically independent on  $V_{\rm ds}$  above a threshold gate voltage, *even at lower temperatures*.

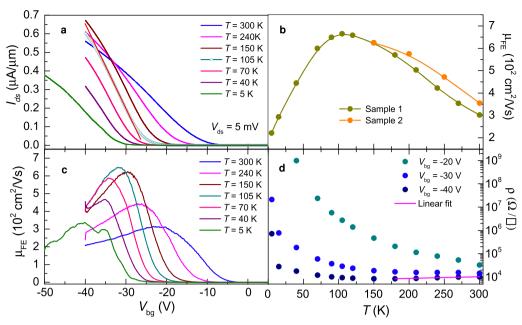

Figure 4a shows  $I_{ds}$  as a function of  $V_{bg}$  for several temperatures and for the crystal shown in Fig. 1a. Fig. 4b shows the resulting fieldeffect mobility  $\mu_{FE}$  as a function of T as extracted from the slopes of  $I_{ds}(V_{bg}, T)$ .  $\mu_{FE}$  is observed to increase, reaching a maximum of  $\sim$ 650 cm<sup>2</sup>/Vs at  $T \sim 100$  K, decreasing subsequently to values around 250 cm<sup>2</sup>/Vs at low temperatures. Orange markers depict  $\mu_{EE}$  for a second, annealed sample whose Hall mobility is discussed below. This decrease is attributable to extrinsic factors, such as chemical residues from the lithographic process, since annealing the samples under high vacuum for at least 24 h considerably increases the mobility at low Ts17, as will be illustrated by the results shown below for a second sample annealed in this way. Figure 4c shows  $\mu_{\text{FE}}$  as a function of  $V_{\rm bg}$  for several temperatures (as extracted from the curves in a). All curves show a maximum at a  $V_{\rm bg}$ -dependent value. As seen, the main effect of lowering T is to increase the threshold back-gate voltage  $V_{\text{bg}}^{\text{t}}$ for carrier conduction. In WS2, by using ambipolar ionic liquid gating, which heavily screens charged defects, the authors of Ref. 29 were able to estimate the size of its semiconducting gap, given roughly by the difference between the threshold voltages required for hole and electron conduction respectively, or  $\sim$ 1.4 V. The much larger  $V_{\rm bg}^{\rm t}$  values observed by us in WSe2 is attributable to intrinsic and extrinsic effects, such as vacancies and charge traps, which limit the carrier mobility becoming particularly relevant at low temperatures, see discussion below. At first glance, at low gate voltages  $\rho$  would seem to follow activated behavior with a small activation gap. On the other hand at high temperatures and high gate voltages, p displays metallic like behavior, usually defined by  $\partial \rho / \partial T > 0$ . Magenta line is a fit to a simple linear-dependence on temperature, suggesting either an unconventional metallic state or most likely, phonon scattering.

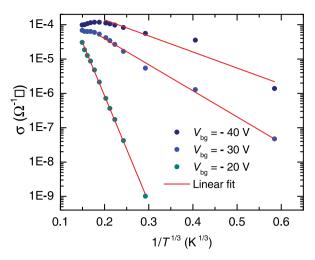

As observed in Figs. 4a and c, the threshold gate-voltage  $V_{\rm bg}^{\rm t}$ required to observe a finite  $\sigma$  increases from  $\sim$ 5 to  $\sim$ 35 V as T is lowered from 300 to 5 K. In order to clarify the dependence of  $V_{\text{bg}}$  on T, we assume that  $V_{\text{bg}}^{\text{t}}$  is dominated by disorder at the interface between WSe2 and SiO2 which leads to charge localization. To illustrate this point, in Fig. 5 we plot  $\sigma(T)$  as function of  $T^{-1/3}$  since from past experience on Si/SiO2 MOSFETs, it is well known that spurious charges intrinsic to the SiO<sub>2</sub> layer<sup>30–32</sup>, in addition to the roughness at the interface between the Si and the glassy SiO<sub>2</sub><sup>33</sup>, produces charge localization leading to variable-range hopping conductivity:  $\sigma(T) =$  $\sigma_0 \exp(-T_0/T)^{1/(1+d)}$  where d is the dimensionality of the system, or d = 2 in our case<sup>34</sup>. As seen in Fig. 5, one observes a crossover from metallic-like to a clear two-dimensional variable-range hopping (2DVRH) conductivity below a gate voltage dependent temperature; red lines are linear fits. At lower gate voltages, the 2DVRH regime is observed over the entire range of temperatures. Therefore, despite the linear transport regime and the relatively large mobilities observed in Figs. 1 through 4, this plot indicates very clearly, that below  $V_{\text{bg}}^{\text{t}}$  the carriers in the channel are localized due to disorder. Notice that similar conclusions were also reported from measurements on MoS<sub>2</sub><sup>35</sup>. Although, at the moment we do not have a clear experimental understanding on the type and on the concomitant role of disorder in these systems (which would allow a deeper theoretical understanding on the origin of the localization), the above experimental plot is unambiguous in revealing the predominant conduction mechanism for gate-voltages below a threshold value.

Now, we are in position of qualitatively explaining the T-dependence of  $V_{\rm bg}$ : thermal activated processes promote carriers across a mobility edge which defines the boundary between extended electronic states and a tail in the density of states composed of localized electronic states. At higher temperatures, more carriers are thermally excited across the mobility edge, or equivalently, can be excited across

Figure 4 | (a)  $I_{\rm ds}$  as a function of the gate voltage  $V_{\rm bg}$  for several temperatures T and for an excitation voltage  $V_{\rm ds}=5\,$  mV. From the slopes of the linear fit (red line) one extracts the respective values of the field-effect mobility  $\mu_{\rm FE}$  as a function of the temperature, shown in (b). Orange markers depicts  $\mu_{\rm FE}$  for a second, annealed sample. The field-effect mobility is seen to increase continuously as the temperature is lowered down to  $T=105\,$  K, beyond which it decreases sharply. (c)  $\mu_{\rm FE}=(1/c_{\rm g})\,d\sigma/dV_{\rm bg}$  as extracted from the curves in (a). Notice that  $\mu_{\rm FE}$  still saturates at a value of  $\approx 300\,$  cm²/Vs at  $T=5\,$  K, d Resistivity  $\rho=1/\sigma$  as a function of T for 3 values of the gate voltage, i.e.  $-20, -30\,$  and  $-40\,$  V, respectively (as extracted from the data in (a) or (c)). Magenta line corresponds to a linear fit, describing the behavior of the metallic resistivity, defined by  $\partial\rho/\partial T>0$ , observed at higher temperatures when  $V_{\rm bg}=-40\,$  V.

the potential well(s) produced by disorder or charge traps, therefore one needs lower gate voltage(s) to untrap the carriers. Once these carriers have moved across the mobility edge, they become mobile and, as our results show, respond linearly as a function of the excitation voltage  $V_{\rm ds}$ . Finally, as  $V_{\rm bg}^{\rm t}$  increases with decreasing T the number of carriers is expected to decrease continuously since they become progressively localized due to the suppression of thermally activated processes which can no longer contribute to carrier detrapping. This is clearly illustrated by Fig. 4b, where one sees an increase in mobility, due to the suppression of phonon scattering, leading to a maximum in the mobility and to its subsequent suppression upon additional cooling. Therefore, at higher temperatures and for gate voltages above the threshold, where one observes a metallic-like state, one has two competing mechanisms at play upon cooling, i.e. the tendency to localization/suppression of carriers which is unfavorable to metallicity, and the suppression of phonon scattering. Suppression of phonon scattering is the only possible explanation for the observed metallic behavior. Hence, one must conclude that this metallic behavior ought to be intrinsic to the compound, but disorder-induced carrier localization dominates  $\sigma$  at lower temperatures.

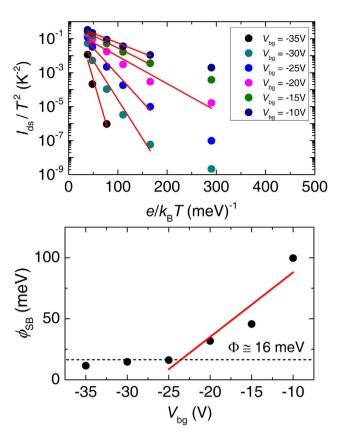

Although, as Figs. 2 and 3 indicate, the conductivity  $\sigma$  as measured through a two-terminal configuration, is linear on excitation voltage  $V_{\rm ds}$  when  $V_{\rm bg} > V_{\rm bg}$ , it was discussed at length that the electrical conduction through the drain and source contacts can by no means be ohmic <sup>19,36</sup>. In effect, a Schottky barrier of ~770 meV is expected as the difference in energy between the work function of Ti, or 4.33 eV, and the ionization energy of WSe<sub>2</sub>, or ~5.1 eV <sup>37,38</sup>. The linear, or apparent ohmic regime presumably would result from thermionic emission or thermionic field emission processes. According to thermionic emission theory, the drain-source current  $I_{\rm ds}$  is related to the Schottky barrier height  $\phi_{\rm SB}$  through the expression:

$$I_{\rm ds} = AA^*T^2 \exp\left(e\phi_{\rm SR}/k_{\rm B}T\right) \tag{1}$$

Where *A* is the area of the Schottky junction,  $A^* = 4\pi e m^* k_B^2 h^{-3}$  is the effective Richardson constant, *e* is the elementary charge,  $k_B$  is the

Boltzmann constant,  $m^*$  is the effective mass and h is the Planck constant<sup>39</sup>. In order to evaluate the Schottky barrier at the level of the contacts, in the top panel of Fig. 6 we plot  $I_{ds}$  normalized by the square of the temperature  $T^2$  as a function of  $e/k_BT$  and for several values of the gate voltage. Red lines are linear fits from which we extract the  $\phi_{SB}(V_{bg})$ . Notice that in the top panel of Fig. 6 the linear fits are limited to higher temperatures since at lower temperatures one observes pronounced, gate dependent, deviations from the thermionic emission theory. The bottom panel of Fig. 6 shows  $\phi_{SB}(V_{bg})$ in a logarithmic scale as a function of  $V_{\rm bg}$ . Red line is a linear fit from whose deviation we extract the size of the Schottky barrier<sup>19</sup>, or  $\Phi$ ~16 meV, indicating a much better band alignment than originally expected. It is perhaps possible that the Eq. (1) might take a different form for layered two-dimensional materials, for example, in such compounds one might need a temperature pre-factor distinct from  $T^2$ . We attempted the use of different temperature pre-factors such as *T* or  $T^{3/2}$ , but it does not improve the linearity of  $\log(I_{ds}/T^{\alpha})$  (with  $2 \ge$  $\alpha \ge 1$ ) as a function of  $ek_B/T$ . In fact, an arbitrary T pre-factor, would not be theoretically justifiable at the moment. Having said that, one has to be very careful with the extraction of the Schottky barrier through this common approach, since the two-terminal measurements contain contributions from both the contacts and the conduction channel. As discussed above, the channel underdoes disorder-induced carrier localization, thus masking the true behavior of the conduction across the contacts. Notice for example, how in Fig. 5 2DVRH fits the behavior of the  $\sigma(T)$  over the entire range of temperatures when  $V_{\rm bg} = -20$  V, while in Fig. 6, thermionic emission can describe the behavior of  $I_{\rm ds}/T^2$  as a function of  $T^{-1}$  only when  $T > 125\,$  K. Therefore the values of  $\phi_{SB}(V_{bg})$  extracted here should be taken with caution.

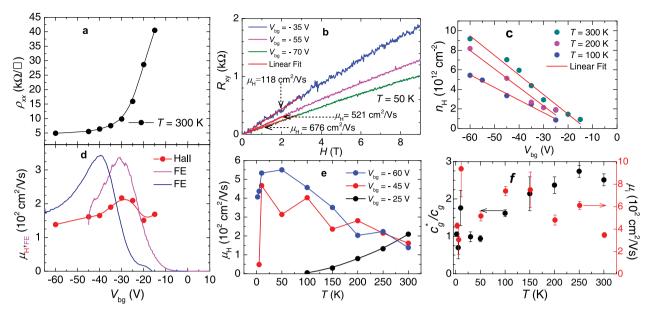

In Figure 7, we compare the above field-effect mobilities with Hall mobility measurements on a second, vacuum annealed flake of similar thickness. Figure 7 a shows the four-terminal sheet resistivity, i.e.  $\rho_{xx} = wV_{\rm ds}/II_{\rm ds}$  as a function of  $V_{\rm bg}$ .  $\rho_{xx}$  was measured with a lock-in technique, for gate voltages where the voltages  $V_{12}$  or  $V_{34}$  were in phase with the excitation signal. We also checked that any pair of

Figure 5 | Conductivity, i.e.  $\sigma = 1/\rho$  (from the data in Fig. 4 d, acquired under  $V_{\rm ds} = 5$  mV) in a logarithmic scale as a function of  $T^{-1/3}$ . Red lines are linear fits, indicating that at lower Ts and for gate voltages below a temperature dependent threshold value  $V_{\rm bg}(T)$ ,  $\sigma(T)$  follows the dependence expected for two-dimensional variable-range hopping.

voltage contacts produced nearly the same value for  $\rho_{xx}$  indicating a nearly uniform current throughout the channel.  $\rho_{xx}$  increases very rapidly, beyond  $10^9 \,\Omega$  as  $V_{\rm bg} \rightarrow 0\,$  V. Also the out-of-phase component of the measured AC signal becomes very large as  $V_{\rm bg} \rightarrow 0$  limiting the  $V_{\rm bg}$  range for our measurements. Figure 7b displays the measured Hall signal  $R_{xy}$  as a function of the magnetic field H at T = 50 K and for several values of  $V_{

m bg}$ . Red lines are linear fits from which we extract the Hall constant  $R_{\rm H}=R_{xy}/H=1/ne$ . In the same Fig. 7b we also indicate the extracted values for the Hall mobilities,  $\mu_H = R_H/$  $\rho_{xx}$ , at different gate voltages. Notice that for T = 50 K and  $V_{bg} =$ 70 V one obtains, in this annealed sample, a  $\mu_H$  value of  $\sim$ 676 cm<sup>2</sup>/ Vs. Figure 7c shows the density of carriers  $n_{\rm H} = 1/eR_{\rm H}$  as a function of  $V_{\rm bg}$  for several Ts. Red lines are linear fits from which we extract the slope  $n_{\rm H}/V_{\rm bg} = c_{\rm g}^*/e$ , where  $c_{\rm g}^*$  is an effective back-gate capacitance: in the absence of extrinsic charged defects at the WSe<sub>2</sub>/SiO<sub>2</sub> interface,  $c_g^*$  should be equal to the previously quoted gate capacitance  $c_g$ . Solid evidence for the existence of ionized impurities acting as hole traps at the interface is provided by the linear fits in Fig. 7c which intercepts the  $n_{\rm H} = 0$  axis at finite threshold gate voltages  $V_{\rm bg}$ . This confirms that practically all holes generated by applying a gate voltage smaller than  $V_{\text{bg}}^{\text{t}}$  remain localized at the interface. Figure 7d shows a comparison between  $\mu_{FE}$  (magenta and blue lines) and  $\mu_{H}$ (red markers) as extracted from the same device at room temperature. The blue line was measured after thermally cycling the FET down to low temperatures. Notice how  $V_{\text{bg}}^{\text{t}}$  increases after thermally cycling the sample, thus suggesting that strain at the interface, resulting from the difference between the thermal expansion coefficients of  $SiO_2$  and  $WSe_2$ , also contributes to  $V_{bg}^t$ . Therefore, strain would seem to be an additional factor contributing to the mobility edge. Notice also that both mobilities initially increase as a function  $|V_{bg}|$ , reaching a maximum at the same  $V_{\rm bg}$  value, decreasing subsequently as the back-gate voltage is further increased. Figure 7e shows  $\mu_H$  as a function of T for several values of  $V_{\text{bg}}$ . Notice how  $\mu_{\text{H}}$  ( $T \rightarrow 0 \text{ K}$ ) is suppressed at low gate voltages due to the charge localization mechanism discussed above.  $\mu_H$  is observed to increase as T is lowered, requiring ever increasing values of  $V_{\rm bg} > V_{\rm bg}^{\rm t}$ , but decreases again below  $T \sim 5$  K. A fit of  $\mu_{\rm H}(T, V_{\rm bg} = -60$  V) to  $AT^{-\alpha}$  yields  $\alpha \sim (1 \pm$ 0.1). Finally Fig. 7f displays the *T*-dependence of the ratio between the measured and the ideal geometrical gate capacitance  $(c_g^* = se)/c_g$ where s corresponds to the slopes extracted from the linear-fits in Fig. 7c. For a perfect FET this ratio should be equal to 1, i.e. the only charges in the conducting channel should be those resulting from the

Figure 6 | Top panel: Drain to source current  $I_{\rm ds}$  as a function of  $(k_{\rm B}T/e)^{-1}$  for several values of the gate voltage  $V_{\rm bg}$  (from the data in Fig. 4a). Red lines are linear fits from which we extract the value of the Schottky energy barrier  $φ_{\rm SB}$ . Bottom panel:  $φ_{\rm SB}$  in a logarithmic scale as a function of  $V_{\rm bg}$ . Red line is a linear fit. The deviation from linearity indicates when the gate voltage matches the flat band condition from which we extract the size of the Schottky barrier  $Φ \approx 16$  meV.

electric field-effect. Therefore, one can estimate the carrier mobility  $\mu_i$  for the nearly ideal device, i.e. with the ideal geometrical capacitance, through  $\mu_i = c_g^*/c_g \mu_H$ , which at T = 300 K would lead to  $V_{bg}$ dependent mobilities ranging from 350 up to 525 cm<sup>2</sup>/Vs. This rough estimate does not take into account scattering processes resulting from for example, other sources of disorder within the channel. In agreement with Ref. 40, this indicates that in our WSe<sub>2</sub> FETs the main scattering mechanism limiting the carrier mobility are not phonons, but ionized impurities and disorder, or that phonon scattering would still allow mobilities approaching, and probably surpassing, 500 cm<sup>2</sup>/Vs at room temperature. In p-doped Si the hole-mobility is observed to saturate at a value of  $\sim$ 475 cm<sup>2</sup>/Vs for doping levels below  $\sim 10^{17}$  per cm<sup>3</sup>, while a doping concentration of  $10^{19}$  per cm<sup>3</sup> yields mobilities of ~200 cm<sup>2</sup>/Vs as observed here<sup>8</sup>. Therefore, our work indicates that if one was able to improve the FET fabrication protocols, by minimizing the disorder such as interface roughness, spurious ionized impurities and dangling bonds at the interface, WSe<sub>2</sub> could match the performance of p-doped Si, thus becoming suitable for specific applications<sup>5</sup> with the added advantage of miniaturization, since the starting point would be just a few atomic layers.

Notice that the  $\mu_{FE}$  values extracted here at higher  $\mathit{Ts}$  would be overestimated if one considers the value of the gate capacitance extracted from the Hall effect, i.e. it would be two to three times larger than the expected geometrical capacitance, thus implying 2 to 3 times smaller values for  $\mu_{FE}$ . A number of reports on TMDs<sup>16,19,20</sup> suggest room temperature field-effect mobilities ranging from 300 to  $\sim$ 700 cm<sup>2</sup>/Vs for MoS<sub>2</sub> based FETs subjected to "dielectric engineering". However, taken together with the debate in Refs. 11, 12

Figure 7 | (a) Four-terminal sheet resistance  $R_{xx}$  measured at a temperature of  $T=300\,$  K and as a function of  $V_{bg}$  for a second multilayered WSe $_2$  FET after annealing it under vacuum for 24 h. (b) Hall response  $R_{xy}=V_H(H)/I_{ds}$  as a function of the external magnetic field H, and for several values of the gate voltage  $V_{bg}$ . Red lines are linear fits from whose slope we extract the values of the Hall constant  $R_H(=V_H/HI_{ds})$ . (c) Density of carriers  $n_H=1/(eR_H)$  induced by the back gate voltage as a function of  $V_{bg}$ . Red lines are linear fits from which, by comparing the resulting slope  $\sigma=n/V_{bg}=c_g*/e$  ( $c_g*$  is the effective gate capacitance). (d) Field-effect  $\mu_{FE}$  (magenta and blue lines) and Hall  $\mu_H=R_H/\rho_{xx}$  (red markers) mobilities (where  $\rho_{xx}=R_{xx}w/l$ , w and l are the width and the length of the channel, respectively) as functions of  $V_{bg}$  at  $T=300\,$  K. (e) Extracted Hall mobility  $\mu_H$  as a function of T and for several values of  $V_{bg}$ .  $\mu_H$  increases as T is lowered, but subsequently it is seen to decrease below a  $V_{bg}$ -dependent T. (f) Ratio between experimentally extracted and the ideal, or geometrical gate capacitances  $c_g*/c_g$  (black markers) and the mobilities  $\mu_i=c_g*/c_g\,\mu_H\,(V_{bg}=-60\,$  V) (red markers) as functions of T.  $\mu_i$  are the mobility values that one would obtain if the gate capacitance displayed its ideal  $c_g$  value in absence of spurious charges in the channel.

concerning the true value of the gate capacitance in dual gated FETs, our study suggests that those values should be carefully re-examined by performing four-terminal Hall-mobility and/or capacitance measurements.

In the Supplemental Information, we show the Raman spectra of  $WSe_2$  whose main Raman modes are observed to sharpen considerably as the number of layers decrease, implying a pronounced increase in phonon lifetimes. Possibly, the main source of disorder in  $WSe_2$  is stacking disorder, which is progressively eliminated as one decreases the number of layers. This also implies a high degree of inplane crystallinity. On the other hand, polarized Raman indicates that most Raman modes in  $WSe_2$  are mixed modes, i.e. composed of in-plane and out-of-plane lattice vibrations, which might affect the strength of its electron-phonon coupling.

Although a gate-voltage dependent Raman study has yet to be performed in WSe<sub>2</sub>, in both single-layer<sup>41</sup> and bi-layer<sup>42</sup> graphene, it was observed that the gate-voltage can tune the interaction between phonons and the charge carriers, leading to changes in the amplitude and in the line-width of the Raman spectra. A similar gate-voltage dependence in WSe<sub>2</sub> might reveal reduced electron-phonon scattering therefore explaining the higher room-temperature Hall mobilities observed here. Notice, that monolayer TMDs have been predicted to display strong piezoelectricity<sup>43</sup>, suggesting that these materials are prone to a strong coupling between lattice degrees of freedom and an external electric field.

# **Conclusions**

In summary field-effect transistors based on multi-layered p-doped WSe $_2$  can display peak hole Hall-mobilities in excess of 200 cm $^2$ /Vs at room temperature. This value increases by a factor >3.3 when the temperature decreases to  $\sim$ 100 K. The carrier density as a function of the gate voltage, as extracted from the Hall-effect, indicates larger than expected gate capacitances thus implying an excess of spurious charges in the channel. Therefore, one should be cautious when

quoting values for the field-effect mobility by using the geometrical gate capacitance value. These spurious charges, in addition to disorder at the  $WSe_2/SiO_2$  interface, leads to carrier localization and to a concomitant mobility edge, which manifests itself in an increasing threshold gate voltage for carrier conduction and, at a fixed gate voltage, to a concomitant decrease in carrier mobility upon cooling (resulting from an increase in the threshold gate voltage). When using Ti:Au for the electrical contacts one obtains a remarkably small value for the size of the Schottky barrier, although thermionic emission theory can only properly fit the transport data at higher temperatures.

We emphasize that our results indicate that WSe2 displays what seemingly are the highest Hall mobilities observed so far in TMDs, particularly among FETs based on few-layered TMDs exfoliated onto SiO<sub>2</sub> and remarkably, without the use of distinct or additional dielectric layers. The Hall mobility values observed here surpass, for example, the  $\mu_H$  values in Ref. 17 for MoS<sub>2</sub> on HfO<sub>2</sub> or the fieldeffect mobilities of thicker multilayered MoS<sub>2</sub> flakes<sup>5</sup> on Al<sub>2</sub>O<sub>3</sub>. This indicates that WSe<sub>2</sub> has the potential to display even higher carrier mobilities, particularly at room temperature, through the identification of suitable substrates (flatter interfaces, absence of impurities and dangling bonds, etc), as well as contact materials. A major materials research effort must be undertaken to clarify the density of point defects (e.g. vacancies, intercalants) in the currently available material and on how to decrease their density. However, our study reveals that WSe<sub>2</sub> has the potential to become as good if not a better material for optoelectronic applications than, for instance, multi-layered MoS<sub>2</sub><sup>5</sup>. Recently, Ref. 44 reported the performance of multi-layered WSe<sub>2</sub> FETs, composed of WSe<sub>2</sub> atomic layers transferred onto a h-BN substrate using graphene for the electrical contacts as well as ionic liquid gating. Remarkably, despite the complexity of this architecture, originally intended to improve the overall performance of multi-layered WSe2 FETs, the simpler devices reported here, still display considerably higher mobilities. We believe this is an import-

ant piece of information for those considering the development of electronic or optoelectronic applications based on transition metal dichalcogenides.

#### **Methods**

WSe<sub>2</sub> single crystals were synthesized through a chemical vapor transport technique using iodine as the transport agent. Multi-layered flakes of WSe2 were exfoliated from these single crystals by using the "scotch-tape" micromechanical cleavage technique, and transferred onto p-doped Si wafers covered with a 270 nm thick layer of SiO<sub>2</sub>. Prior to transferring the WSe2 crystals onto the SiO2 layers, these were cleaned in the following way: SiO<sub>2</sub> was sonicated for 15 min in acetone, isopropanol and deionized water, respectively. It was subsequently dried by a nitrogen gas flow. For making the electrical contacts 90 nm of Au was deposited onto a 4 nm layer of Ti via e-beam evaporation. Contacts were patterned using standard e-beam lithography techniques. After gold deposition, the devices were annealed at 200°C for ~2 h in forming gas. Atomic force microscopy (AFM) imaging was performed using the Asylum Research MFP-3D AFM. Electrical characterization was performed by using a combination of sourcemeter (Keithley 2612 A), Lock-In amplifier (Signal Recovery 7265) and resistance bridges (Lakeshore 370) coupled to a Physical Property Measurement System. The Raman spectra were measured in a backscattering geometry using a 532.1 nm laser excitation. For additional details see the Supplementary Information.

- Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* 7, 699 (2014).

- Chhowalla, M. et al. The Chemistry of Two-Dimensional Layered Transition Metal Dichalcogenide Nanosheets. Nat. Chem. 5, 263–275 (2013).

- Zeng, H. L., Dai, J. F., Yao, W., Xiao, D. & Cui, X. D. Valley Polarization in MoS<sub>2</sub> Monolayers by Optical Pumping. Nat. Nanotechnol. 7, 490–493 (2012).

- Mak, K. F., He, K. L., Shan, J. & Heinz, T. F. Control of Valley Polarization in Monolayer MoS<sub>2</sub> by Optical Helicity. *Nat. Nanotechnol.* 7, 494–498 (2012).

- Kim, S. et al. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. Nat. Commun. 3, 1011 (2012).

- Tonndorf, P. et al. Photoluminescence Emission and Raman Response of Monolayer MoS<sub>2</sub>, MoSe<sub>2</sub>, and WSe<sub>2</sub>. Opt. Express 21, 4908–4916 (2013)

- Podzorov, V., Gershenson, M. E., Kloc, Ch., Zeis, R. & Bucher, E. High-Mobility Field-Effect Transistors Based on Transition Metal Dichalcogenides. *Appl. Phys. Lett.* 84, 3301 (2004).

- Reggiani, S. et al. Electron and Hole Mobility in Silicon at Large Operating Temperatures - Part I: Bulk mobility. IEEE T. Electron. Dev. 49, 490 (2002).

- Ayari, A., Cobas, E., Ogundadegbe, O. & Fuhrer, M. S. Realization and Electrical Characterization of Ultrathin Crystals of Layered Transition-Metal Dichalcogenides. J. Appl. Phys. 101, 014507 (2007).

- Lembke, D. & Kis, A. Breakdown of High-Performance Monolayer MoS<sub>2</sub> Transistors. ACS Nano 6, 10070–10075 (2012).

- Fuhrer, M. S. & Hone, J. Measurement of Mobility in Dual-Gated MoS<sub>2</sub> Transistors. Nat. Nanotechnol. 8, 146–147 (2012).

- Radisavljevic, B. & Kis, A. Measurement of Mobility in Dual-Gated MoS<sub>2</sub> Transistors. Nat. Nanotechnol. 8, 147–148 (2013).

- Radisavljevic, B. & Kis, A. Mobility Engineering and a Metal-Insulator Transition in Monolayer MoS<sub>2</sub>. Nat. Mater. 12, 815 (2013).

- Zeng, L. et al. Remote Phonon and Impurity Screening Effect of Substrate and Gate Dielectric on Electron Dynamics in Single Layer MoS<sub>2</sub>. Appl. Phys. Lett. 103, 113505 (2013)

- Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>. ACS Nano 12, 9934 (2011).

- Wang, H. et al. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. Nano Lett. 12, 4674 (2012).

- 17. Baugher, B. W. H., Churchill, H. O. H., Yang, Y. & Jarillo-Herrero, P. Intrinsic Electronic Transport Properties of High-Quality Monolayer and Bilayer  $MoS_2$ . *Nano Lett.* **13**, 4212–4216 (2013).

- Neal, A. T., Liu, H., Gu, J. & Ye, P. D. Magneto-transport in MoS<sub>2</sub>: Phase Coherence, Spin-Orbit Scattering, and the Hall Factor. ACS Nano 8, 7077–7082 (2013).

- Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* 13, 100–105 (2013).

- Bao, W., Cai, X., Kim, D., Sridhara, K. & Fuhrer, M. S. High Mobility Ambipolar MoS<sub>2</sub> Field-effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* 102, 042104 (2013).

- 21. Yin, Z. et al. Single-Layer MoS<sub>2</sub> Phototransistors. ACS Nano 6, 74 (2012).

- Lee, H. S. et al. MoS<sub>2</sub> Nanosheet Phototransistors with Thickness-Modulated Optical Energy Gap. Nano Lett. 12, 3695 (2012).

- 23. Choi, W. et al. High-Detectivity Multilayer MoS<sub>2</sub> Phototransistors with Spectral Response from Ultraviolet to Infrared. Adv. Mater. 43, 5832 (2012).

- 24. Kaasbjerg, K., Thygesen, K. S. & Jacobsen, K. W. Phys. Rev. B 85, 115317 (2012).

- Fang, H. et al. High-Performance Single Layered WSe<sub>2</sub> p-FETs With Chemically Doped Contacts. Nano Lett. 12, 3788 (2012).

- Liu, W. et al. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe<sub>2</sub> Field Effect Transistors. Nano Lett. 13, 1983–1990 (2013).

- Pradhan, N. R. et al. Intrinsic Carrier Mobility of Multi-Layered MoS<sub>2</sub> Field-Effect Transistors on SiO<sub>2</sub>. Appl. Phys. Lett. 102, 123105 (2013).

- Hwang, W. S. et al. Transistors with Chemically Synthesized Layered Semiconductor WS<sub>2</sub> Exhibiting 10<sup>5</sup> Room Temperature Modulation and Ambipolar Behavior. Appl. Phys. Lett. 101, 013107 (2012).

- Braga, D., Lezama, I. G., Berger, H. & Morpurgo, A. F. Quantitative Determination

of the Band Gap of WS<sub>2</sub> with Ambipolar Ionic Liquid-Gated Transistors. *Nano Lett.* 12, 5218–5223 (2012).

- 30. Fang, F. F. & Fowler, A. B. Transport Properties of Electrons in Inverted Silicon Surfaces. *Phys. Rev.* **169**, 619 (1968).

- Hartstein, A., Ning, T. H. & Fowler, A. B. Electron Scattering in Silicon Inversion Layers by Oxide and Surface Roughness Original Research. Surf. Sci. 58, 178 (1976).

- Hasegawa, H. & Sawada, T. On the Distribution and Properties of Interface States at Compound Semiconductor-Insulator Interfaces. Surf. Sci. 98, 597 (1980).

- 33. Ando, T. Screening Effect and Quantum Transport in a Silicon Inversion Layer in Strong Magnetic Fields. *J. Phys. Soc. Jpn.* **43**, 1616–1626 (1977).

- Mott, N. F. Coulomb Gap and Low-Temperature Conductivity of Disordered Systems. J. Phys. C: Solid State Phys. 8, L239–L240 (1975).

- Ghatak, S., Pal, A. N. & Ghosh, A. Nature of Electronic States in Atomically Thin MoS, Field-Effect Transistors. ACS Nano 5, 7707–7712 (2011).

- 36. Chen, J.-R. *et al.* Control of Schottky Barriers in Single Layer MoS<sub>2</sub> Transistors with Ferromagnetic Contacts. *Nano. Lett.* **13**, 3106–3110 (2013).

- 37. Lang, O., Tomm, Y., Schlaf, R., Pettenkofer, C. & Jaegermann, W. Single Crystalline GaSe/WSe<sub>2</sub> Heterointerfaces Grown by Van der Waals Epitaxy. II. Junction Characterization. J. Appl. Phys. 75, 7814 (1994).

- McDonnel, S. et al. Hole Contacts on Transition Metal Dichalcogenides: Interface Chemistry and Band Alignments. ACS Nano 8, 6265 (2014).

- Yang, H. et al. Graphene Barristor, a Triode Device with a Gate-Controlled Schottky Barrier. Science 336, 1140 (2012).

- 40. Ma, N. & Jena, D. Charge Scattering and Mobility in Atomically Thin Semiconductors. *Phys. Rev. X* **4**, 011043 (2014).

- Yan, J., Zhang, Y., Kim, P. & Pinczuk, A. Electric Field Effect Tuning of Electron-Phonon Coupling in Graphene. Phys. Rev. Lett. 98, 166802 (2007).

- 42. Yan, J., Henriksen, E. A., Kim, P. & Pinczuk, A. Observation of Anomalous Phonon Softening in Bilayer Graphene. *Phys. Rev. Lett.* **101**, 136804 (2008).

- Duerloo, K.-A. N., Ong, M. T. & Reed, E. J. Intrinsic Piezoelectricity in Two-Dimensional Materials. J. Phys. Chem. Lett. 3, 2871 (2012).

- 44. Chuang, H.-J. et al. High Mobility WSe<sub>2</sub> p- and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. Nano Lett. 14, 3594–3601 (2014).

# **Acknowledgments**

This work is supported by the U.S. Army Research Office MURI grant W911NF-11-1-0362. The NHMFL is supported by NSF through NSF-DMR-0084173 and the State of Florida.

#### **Author contributions**

L.B. conceived the project in discussions with N.R.P., S.T., M.T. and P.M.A. D.R. synthesized the WSe $_2$  single crystals. N.R.P. and D.R. characterized the thickness of the used flakes though AFM techniques. N.R.P. fabricated the field-effect transistors. J.M.P., D.S. and M.T. performed polarized Raman experiments and their dependence on number of layers as well as the corresponding analysis. S.F., N.P.L., A.L.E. and M.T. have performed Raman measurements as a function of excitation frequency. N.R.P., S.M. and L.B. performed the electrical transport characterization. N.R.P. and L.B. analyzed the corresponding data. L.B. wrote the manuscript with the input of all co-authors.

### **Additional information**

${\bf Supplementary\ information\ accompanies\ this\ paper\ at\ http://www.nature.com/scientific$ reports

Competing financial interests: The authors declare no competing financial interests.

**How to cite this article:** Pradhan, N.R. *et al.* Hall and field-effect mobilities in few layered *p*-WSe<sub>2</sub> field-effect transistors. Sci. Rep. 5, 8979; DOI:10.1038/srep08979 (2015).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/