# **ARTICLE**

Received 8 Oct 2014 | Accepted 25 Feb 2015 | Published 13 Apr 2015

DOI: 10.1038/ncomms7785

**OPEN**

# Direct electron injection into an oxide insulator using a cathode buffer layer

Eungkyu Lee<sup>1,\*</sup>, Jinwon Lee<sup>1,\*</sup>, Ji-Hoon Kim<sup>2</sup>, Keon-Hee Lim<sup>1</sup>, Jun Seok Byun<sup>2</sup>, Jieun Ko<sup>1</sup>, Young Dong Kim<sup>2</sup>, Yongsup Park<sup>2</sup> & Youn Sang Kim<sup>1,3</sup>

Injecting charge carriers into the mobile bands of an inorganic oxide insulator (for example,  $SiO_2$ ,  $HfO_2$ ) is a highly complicated task, or even impossible without external energy sources such as photons. This is because oxide insulators exhibit very low electron affinity and high ionization energy levels. Here we show that a ZnO layer acting as a cathode buffer layer permits direct electron injection into the conduction bands of various oxide insulators (for example,  $SiO_2$ ,  $Ta_2O_5$ ,  $HfO_2$ ,  $Al_2O_3$ ) from a metal cathode. Studies of current-voltage characteristics reveal that the current ohmically passes through the ZnO/oxide-insulator interface. Our findings suggests that the oxide insulators could be used for simply fabricated, transparent and highly stable electronic valves. With this strategy, we demonstrate an electrostatic discharging diode that uses 100-nm  $SiO_2$  as an active layer exhibiting an on/off ratio of  $\sim 10^7$ , and protects the ZnO thin-film transistors from high electrical stresses.

<sup>&</sup>lt;sup>1</sup> Program in Nano Science and Technology, Graduate School of Convergence Science and Technology, Seoul National University, Seoul 151-742, Republic of Korea. <sup>2</sup> Department of Physics, Research Institute for Basic Sciences, Kyung-Hee University, Seoul 130-701, Republic of Korea. <sup>3</sup> Green Battery Innovation Research Center, Advanced Institutes of Convergence Technology, Gyeonggi-do 443-270, Republic of Korea. \* These authors contributed equally to this work. Correspondence and requests for materials should be addressed to Y.S.K. (email: younskim@snu.ac.kr).

ost inorganic oxide materials (for example, SiO<sub>2</sub>, HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>) are conventionally used for electrically insulating components, because of a large energy level offset (3-4 eV) between its mobile bands and the work function of metal electrodes<sup>1-4</sup>. Meanwhile, carrier injection into the mobile bands of the oxide material from the metal electrode is severely limited by the large energy level offset or only exceptionally permitted by Fowler-Nordheim tunnelling or hot-carrier injection processes, which both demand particular conditions: Fowler-Nordheim tunnelling requires very high electric fields  $(7.5-10 \,\mathrm{MV cm}^{-1})$  at the interface between the oxide component and metal electrodes<sup>5</sup>; the hot-carrier injection process needs extra experimental systems that make electrons energetically jump to the conduction bands of the oxide insulator from a metal cathode by adding additional energy (for example, from a photon) to the electron. These requirements make the electroninjecting process complicated and difficult.

Here we have found that using solution-processed ZnO as a cathode buffer layer (CBL) enables injecting electrons into the conduction bands of oxide insulators from a metal cathode. Studies of the current (J)-voltage (V) characteristics of CBLapplied devices, consisting of P++-Si anode/oxide insulator/6nm ZnO (CBL)/metal cathode, provide evidence that electrical currents ohmically flow at the insulator/ZnO interfaces. In addition, we have confirmed that the cathode engineering strategy using the CBL credibly works for various oxide insulators (for example, SiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>) fabricated by mature and ubiquitous oxide film-fabricating processes. This means that the oxide materials have a wide degree of freedom for being exploited as highly stable electronic valves or gate doors beyond current specific uses as insulators, which allows us to precisely and reliably control flow directions and distributions of the charge carriers. Particularly, as an application, we have successfully demonstrated that a device consisting of P++-Si anode/100-nm SiO<sub>2</sub>/6-nm ZnO (CBL)/Al cathode, showing

current-rectifying ratio of  $\sim 10^7$ , can be directly adapted to electrostatic discharge (ESD) diodes for protecting thin-film transistors (TFTs) from high electrical current inputs.

### Results

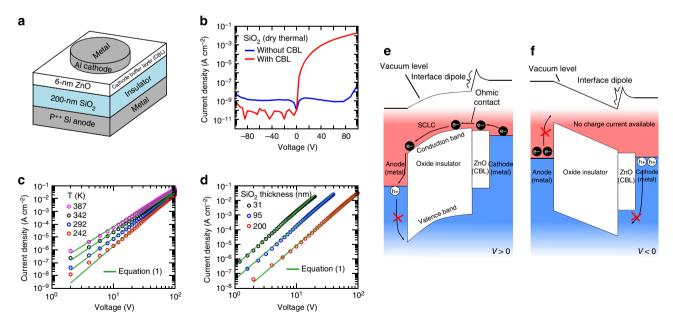

Electrical conductions in SiO<sub>2</sub>/ZnO junction. Figure 1a shows the schematic structure of the P++-Si anode/SiO<sub>2</sub>/ZnO/Al cathode device, and we refer the device to metal/insulator/CBL/ metal (MICM) device. A 200-nm SiO2 layer was grown via dry thermal oxidation on top of highly B-doped Si substrates<sup>7</sup>. A 6nm-thick ZnO layer was deposited by spin-casting a zincammonia complex solution<sup>8,9</sup>. Other experimental details are provided in the Method section. The measured *J–V* characteristics of the MICM device are shown in Fig. 1b. To avoid any electrical contamination effects, the I-V characteristics were measured under a vacuum (~10 mTorr) and in the dark. Surprisingly, it was observed that the device allows large amounts of electrical currents, and it rectifies the current with an on/off ratio of  $\sim 10^8$ within a voltage regime of -100 V < V < 100 V. The current only flows from the P ++ -Si anode to the Al cathode. On the other hand, we also fabricated control devices consisting of P++-Si/200-nm SiO<sub>2</sub>/Al. As shown in Fig. 1b, the *J-V* characteristics of the control device show very low electrical current ( $\sim 10^{-9}$  A) cm<sup>-2</sup>) within the estimated voltage regions, indicating that the thermally grown SiO<sub>2</sub> layer has high-quality electrical insulating properties, and confirming that the electrical current in the MICM devices is attributed to the CBL.

To check whether the observed electrical properties of the MICM device come from the electrical current directly passing through the structure of P $^{++}$ -Si/200-nm SiO<sub>2</sub>/ZnO/Al or not, we investigated followings: (i) the electrical properties of the MICM device with patterned ZnO layer (Supplementary Fig. 1 and Supplementary Note 1); (ii) physical damages of the SiO<sub>2</sub> layer during ZnO fabricating processes (Supplementary Fig. 1 and

Figure 1 | Characteristics and mechanisms of charge conductions in metal/insulator/cathode buffer layer/metal (MICM) structures. (a) Schematic structure of the MICM device consisting of  $P^{++}$ -Si anode/insulator 200-nm  $SiO_2$ /6-nm ZnO/Al cathode. (**b-d**) Current density-voltage characteristics of the MICM devices employing a thermally grown 200-nm  $SiO_2$  as the insulator; (**b**) with (red solid line) and without (blue solid line) the CBL; (**c**) under various temperature (T) conditions (symbols); (**d**) depending on the thickness of the  $SiO_2$  layer (symbols) at T = 292 K. In **c** and **d**, green solid lines indicate theoretical fitting results to the measured curves using equation (1) with fitting parameters shown in Supplementary Table 1. (**e,f**) Schematic of current-rectifying mechanisms of the MICM device, when: (**e**) V > 0, current flows by space-charge-limited currents (SCLCs) of electrons injected from the metal cathode; (**f**) V < 0, charge injection processes are not allowed, and then there are no available space charge currents.

Supplementary Note 1); (iii) in-plane electrical conduction of the ZnO layer on the SiO<sub>2</sub> layer (Supplementary Fig. 2 and Supplementary Note 2); (iv) material and electrical properties of the ZnO layer (Supplementary Fig. 3 and Supplementary Note 3). Consequently, it has been confirmed that the electrical current directly flows through the MICM devices, and it is not an inplane or side-wall electrical current in ZnO films. In addition, the electrical insulating properties of SiO<sub>2</sub> layer have not been changed by the ZnO fabrication processes, and the solution-processed ZnO film on the SiO<sub>2</sub> layer is a conventional nanocrystalline ZnO semiconductor with an optical band gap of  $\sim 3.3~\rm eV$ .

Charge-transporting mechanisms in the MICM devices. To analyse the electrical conduction mechanisms of the MICM devices, the J-V characteristics were investigated at various T. Figure 1c shows the measured J-V curves at  $T=387,\ 342,\ 292$  and 242 K. In log-log scale of the axes, the J-V curves exhibit straight lines, indicating that the conduction mechanism is based on the space-charge-limited currents (SCLCs) of the devices<sup>1</sup>. In addition, as the temperature of the devices decreases, the slope of the J-V curves in the log-log scale gradually increases and the electrical current level at equal voltages decrease. The J-V characteristics depending on T mean that the SCLC in the MICM device is affected by the carrier-trapping state below the transport bands in the insulator  $^{10-12}$ .

An equation for the SCLC in an amorphous insulator with traps can be developed as shown below (details for deriving the expression are in Supplementary Note 4),

$$J = \sigma_0 \left[ \frac{\varepsilon_0 \varepsilon_i l \sin(\pi/l) l^4}{q(l+1) B_c(2\alpha)^3} \right]^l \left( \frac{2l+1}{l+1} \right)^{l+1} \left( \frac{1}{d} \right)^{2l+1} V^{l+1}, \quad (1)$$

where  $\sigma_0$  is the conductivity prefactor;  $B_c$  is the critical number for percolation onset (2.8 in the three-dimensional amorphous system<sup>13</sup>);  $\alpha$  is the effective overlap parameter for the electron-hopping process<sup>13</sup>;  $\varepsilon_i$  is the relative dielectric constant in the insulator;  $\varepsilon_0$  is the electrical permittivity in a vacuum; q is the electronic charge; d is the thickness of the insulator; and  $l = T_0/T$ , where  $T_0$  is the trap-characteristic temperature when the density-of-states traps follow an exponential distribution below transport bands in the insulator<sup>13</sup>. It is assumed that  $\varepsilon_i$  for the SiO<sub>2</sub> layer is 3.9 and d for the MICM device is 200 nm, given that the thickness of the ZnO (6 nm) is much thinner than that of the SiO<sub>2</sub> (200 nm).

Equation (1) shows that the slope of the J-V curves in log-log scale is  $T_0/T + 1$ ; the slope increases as T decreases, corresponding to the experimental results. As a results, the measured J-V curves under the estimated T ranges are clearly fitted by equation (1), with  $T_0 = 758 \,\mathrm{K}$ ,  $\sigma_0 = 5.66 \times 10^{-4} \,\mathrm{S \, cm^{-1}}$ , and  $\alpha = 5.02 \times 10^6$  cm<sup>-1</sup>, as shown in Fig. 1c. In addition, we investigated the J-V characteristics with changes in the thickness of the SiO<sub>2</sub> layer (Fig. 1d), finding that the voltage required to give an equal current density is reduced as the SiO<sub>2</sub> film becomes thinner. The all curves in log-log axes scale exhibit straight lines with very similar slope and well fitted by equation (1). As the SiO<sub>2</sub>-growing conditions are not identical to each others, the fitting parameters for each device are slightly different to each other (see Supplementary Table 1). However, the tendency, where decreasing the thickness of SiO<sub>2</sub> layer leads to reducing required voltage at equal current density, is in good agreement with equation (1). Consequently, the results strictly confirm that the electrical conduction in the MICM device arises entirely from the trap-limited SCLC in the SiO<sub>2</sub> films.

# Origin of the ohmic contact at oxide insulator/CBL interface.

To observe the occurrence of SCLC in a structure of metal/ insulator/metal, it must be required that at least one of the two metal electrodes make 'ohmic contact' with the insulator 10, where the 'ohmic contact' describes that an electron can be efficiently injected into the transport bands of the insulator from the metal electrodes. In this study, the SCLC phenomena in the MICM devices are only observed when negative (or positive) voltages are applied to the Al cathode (or  $P^{++}$ -Si anode), and the I-Vcharacteristics of the control devices show very low electrical current density levels. These results indicate that the hole injection process from the anode is not the main reason for the SCLC in the MICM devices, as the electrical contact properties of P<sup>++</sup>-Si/SiO<sub>2</sub> are identical to both devices. Therefore, the SCLC characteristics of the MICM device come entirely from the electron injection process. It provides evidence that the ohmic contact occurs at the SiO<sub>2</sub>/ZnO interfaces, which means that the conduction band of the ZnO layer is closely located to the conduction band of the SiO<sub>2</sub> layer; thereby electrons in the ZnO layer are efficiently entered to the transport band of the SiO2

The ohmic contact indicates that electrostatic energy band alignments (for example, vacuum level) in the SiO<sub>2</sub>/ZnO junction are modified, as the conduction bands level offset between two materials is about 3 eV at infinite distance 14,15. We have found that such energy band alignments are related to the ZnO thickness,  $t_{\rm zno}$  (see Supplementary Fig. 4 and Supplementary Note 5). When  $t_{\rm zno}$  is  $\sim 0.4$  nm, the MICM device does not exhibit the notable electrical currents, whereas the MICM devices with  $t_{zno}$  of 1.6, 7.7 and 12.7 nm show very similar current-rectifying characteristics compared with each other. It is revealed that the vacuum level modifications are confined to the SiO<sub>2</sub>/ZnO interfaces, suggesting a presence of interface electrical dipoles as shown in Fig. 1e,f16. We have noted that the interface dipoles are not associated to chemical contaminants or residues during the solution process of the ZnO layer, but rather to ZnO layer itself: with a 10-nm-thick ZnO layer fabricated by a sputtering method, a structure of P++-Si/200-nm SiO<sub>2</sub>/10-nm ZnO/Au also shows the remarkable SCLC characteristics (see Supplementary Fig. 5 and Supplementary Note 6).

In semiconductor/metal junctions, a similar effect has been reported that the contact resistance of the junctions is considerably reduced by inserting a thin-insulating layer between the semiconductor and metal layer, where the insulating layer has thickness of lower than  $\sim 2$  nm (refs 17,18). In this geometry, the electron introduced in the metal electrode must be injected to the mobile bands of the semiconductor by quantum mechanical tunnelling effect, and then this type of contact is referred to as 'tunnel contact' or 'tunnel-barrier contact'. Studies of the tunnel-barrier contact have shown that the reduced contact resistance is due to 'Fermi-level unpinning' by that the insertedinsulating layer attenuates metal-induced gap states at the semiconductor/metal junctions<sup>17,18</sup>. However, the MICM devices are well operated when the thickness of the ZnO layer is higher than  $\sim 2$  nm, and the intrinsic energy level off-set between conduction bands of insulator and work function of metals is very high values about  $\sim 3 \, \text{eV}$ . Therefore, it is a reasonable assumption that the electrical conductions in the MICM devices arise from the ohmic contact at the SiO<sub>2</sub>/ZnO interfaces by the electrical dipoles.

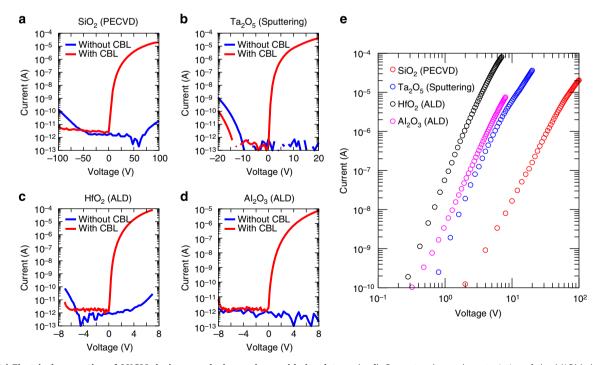

MICM device with various oxide insulators. Next, we investigated whether the CBL can work for other oxide insulators which are fabricated by conventional film-growing techniques. Four types of insulators widely used in commercial applications were

chosen for this study: 200-nm-thick SiO2 grown by the plasma enhanced chemical vapour deposition (PECVD)<sup>19</sup>, 100-nm-thick Ta<sub>2</sub>O<sub>5</sub> fabricated by the radiofrequency magnetron sputtering<sup>20</sup>, and 10-nm-thick HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> deposited by the atomic layer deposition (ALD)<sup>21,22</sup>. Device structures are consisted of P<sup>++</sup>-Si anode/insulator/6-nm ZnO/Au cathode. As shown in Fig. 2a-d, all devices with the CBL allow notable electrical currents flowing from the anode to the cathode with high rectification ratio, whereas the devices without the CBL show very low amount of the electrical current levels. The measured J-V curves of all devices shows straight lines (see Fig. 2e) in log-log axes, which describe the current conduction mechanism is mainly based on the SCLC phenomena. Hence, the CBL modifies the energy band alignment at the interfaces between the metal cathode and the various oxide insulators, which allow that electrons can be directly injected into the conduction band of the oxide materials. In addition, these results reveal that the cathode engineering strategy is well compatible with various oxide insulators grown by conventional film-depositing techniques.

Another interesting feature in results of Fig. 2 is a broad operating-voltage region of each device. With the 200-nm SiO<sub>2</sub> insulator, the MICM device needs operating voltages of  $\sim 100~\rm V$  for achieving electrical current of  $10^{-5}~\rm A$  with rectification ratio of  $\sim 10^6$ . In the case of the 100-nm Ta<sub>2</sub>O<sub>5</sub> insulator-applied device, operation voltages of  $\sim 20~\rm V$  are sufficient for flowing electrical current of  $\sim 10^{-5}~\rm A$ , with on/off ratio of  $\sim 10^6$ . For very-thin Al<sub>2</sub>O<sub>3</sub> (or HfO<sub>2</sub>) insulator, the device can be worked within low-voltage values smaller than  $\sim 8~\rm V$  with currents rectification ratio of  $\sim 10^7$  (or  $10^6$ ). These J-V characteristics depending on the insulator thickness are well corresponded to equation (1), and their properties provide a wide engineering window as a basic electrical element for realizing practical electronic devices.

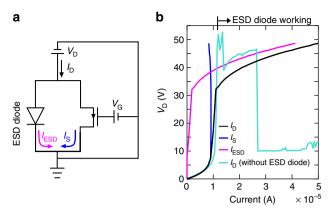

MICM as ESD diode for protecting ZnO TFTs. As an application, we applied the MICM device as ESD diodes to protect ZnO TFTs under high-electrical current input conditions. In the integrated circuits of TFTs, unintended electrostatic charges accumulated by human bodies or film-fabricating processes severely damage the TFTs<sup>23,24</sup>. When electrostatic charges are accumulated at gate or drain electrode, the abruptly introduced high electrical currents escape through the TFTs channel or gate insulators, which melt the channel down or electrically break down gate insulators. To prevent the degradation, ESD diodes are electrically connected to the TFTs with parallel path; the introduced high currents pass through the ESD diodes. To date, in TFT-integrated circuits using oxide semiconductors as channel layers, gate-connected TFT diodes have been used to ESD diodes for protecting the TFTs from the accumulated electrostatic charges<sup>25,26</sup>. However, uncontrollable turn-on voltage shifts in the TFTs have been problematic in that the gate-connected TFT diodes may work at the operating voltage ranges of the TFTs<sup>27,28</sup>. These operation troubles are challenging issues for display panel including oxide TFT-integrated circuits.

Meanwhile, the proposed MICM device as the ESD diode is free from the turn-on voltage problem. Figure 3a shows an equivalent circuit for a ZnO TFT protected by the ESD diode, which is based on the MICM device. The MICM device consists of P  $^{++}$  Si/100-nm SiO<sub>2</sub>/6-nm ZnO/Al electrode, and the ZnO TFT has a bottom gate top contact structure with a channel length (or width) of 50  $\mu$ m (or 1,000  $\mu$ m) and a 100-nm SiO<sub>2</sub> gate dielectric insulator. To check electrical current resistances of the circuit, the currents were injected into the drain electrode (we refer this current to the drain current,  $I_D$ ), and introduced voltages between the drain and source electrodes ( $V_D$ ) were then measured. The gate-source voltage ( $V_G$ ) of the ZnO TFT is maintained to 10 V. In low-current regimes of

Figure 2 | Electrical properties of MICM devices employing various oxide insulators. (a-d) Current-voltage characteristics of the MICM devices employing (a) a 200-nm  $SiO_2$  fabricated by PECVD, (b) a 100-nm  $Ta_2O_5$  deposited by radiofrequency magnetron sputtering, (c) a 10-nm  $HfO_2$  and (d) a 10-nm  $Al_2O_3$  grown by ALD. In a-d, the P<sup>++</sup>-Si and Au were used for metal anode and cathode, respectively; the red and blue solid lines depict the electrical properties of the device with and without the CBL, respectively. (e) Current-voltage characteristics of the MICM devices in a-d represented in log-log scale axes.

**Figure 3** | **An application of MICM devices as electrostatic discharge (ESD) diodes for protecting ZnO TFTs.** (a) An equivalent circuit of the TFT parallel connected with ESD diode;  $I_D$  is the electrical current inputs injecting into a drain electrode of the TFT;  $I_S$  and  $I_{ESD}$  indicate the electrical current passing through the TFT and the ESD diode, respectively;  $V_D$  (or  $V_G$ ) depicts the introduced voltage between the drain (or gate) and source electrode of the TFT. (b) The  $V_D$ -currents characteristics of the circuit in **a**;  $I_D$  with the ESD diode for black,  $I_S$  for blue,  $I_{ESD}$  for magenta and  $I_D$  without the ESD diode for turquoise colour solid line; the insulator and cathode for the MICM device are a thermally-grown 100-nm SiO<sub>2</sub> and AI, respectively; the ZnO TFT has a channel length (or width) of 50 μm (or 1,000 μm) and the 100-nm SiO<sub>2</sub> gate insulator, and the device is under  $V_G = 10$  V.

$0\,\mathrm{A} < I_\mathrm{D} < \sim 1.0 \times 10^{-5}\,\mathrm{A}$ , the most of drain currents flowing into the circuit escape through the ZnO TFT (see blue solid line in Fig. 3b,  $I_{\rm S}$ , the current passing through the source electrode of the ZnO TFTs). As the TFT is under saturation regime, slightly higher injected currents above the saturation current  $(\sim 1.0 \times 10^{-5} \,\mathrm{A})$  of the TFTs drastically increase the applied  $V_{\mathrm{D}}$ values. As a results, the ESD diode turns on for the condition of  $V_{\rm D} = 32 \, {\rm V}$  and  $I_{\rm D} = \sim 1.1 \times 10^{-5} \, {\rm A}$ . At the  $I_{\rm D}$  regions above  $\sim 1.1 \times 10^{-5}$  A, the overloaded current ( $I_{\rm ESD}$ ), which is defined by  $I_{\rm ESD} = I_{\rm D} - I_{\rm S}$ , stably escape to the proposed ESD diode (see magenta solid line in Fig. 3b). Without the ESD diode, however, the ZnO TFT was totally broken down at the  $I_D$  regions higher than  $\sim 1.1 \times 10^{-5}$  A. These results clearly show that the MICM device as the ESD diode has a potential for directly adapting to commercial oxide semiconductor-based TFT-integrated circuits with the structural coherence and highly reliable performance.

### Discussion

In summary, the studies of the J-V characteristics of the MICM devices strictly reveal that the solution-processed ZnO layer as the CBL is critical for direct electron injection into the conduction band of the various oxide insulators. Meanwhile, the unveiling of the ohmic contact between the ZnO and the insulators remains on the scale of electrostatic energy band alignment, and it is also a challenging issue to investigate how the ZnO can interact chemically and electrically with surfaces of the oxide materials, resulting in the ohmic contact. Likewise, it has been reported that electrical dipoles are formed at an interface between high-k oxide insulator and SiO<sub>2</sub>, where the difference of oxygen densities in adjacent oxide layers drives formation of the dipoles via charged-oxygen migrations<sup>29</sup>. Such mechanism should be considered for investigating the ohmic contact. The currentrectifying characteristics of the MICM devices can be easily characterized by insulator thickness and types. The electrical and structural properties of the MICM devices allow them to fill niches not currently occupied by traditional diodes

(for example, *p-n* junction<sup>1,2</sup>, gate-connected transistor<sup>1,2</sup> and metal-insulator-semiconductor-tunnel diodes<sup>30,31</sup>) or to replace the conventionally used current-rectifying devices, since it does not require complex fabricating systems like ion implementations<sup>31</sup>. Furthermore, it can be expected that the novel strategy for direct electron injection into oxide insulator soon meets various relevant applications, given their suitability to conventional oxide-insulator-film deposition techniques, simple fabricating method and transparency to visible light.

### Methods

**Preparations of various oxide insulator thin films.** The SiO<sub>2</sub> layers were grown onto the Si wafers by dry thermal oxidation method (for the 95-nm and 200-nm SiO<sub>2</sub> in Fig. 1 and the 100-nm SiO<sub>2</sub> in Fig. 3) or PECVD (Plasma-Therm 790 series) with SiH<sub>4</sub> and N<sub>2</sub>O gas (for the 200-nm SiO<sub>2</sub> in Fig. 2). The 31-nm SiO<sub>2</sub> in Fig. 1 was made by etching 95-nm-thick thermally grown SiO<sub>2</sub> layer via inductively coupled plasma etching (STS Multiplex ICP) with CF<sub>4</sub>-etching gas. The 100-nm Ta<sub>2</sub>O<sub>5</sub> layers were first deposited onto the Si wafers by radiofrequency magnetron sputtering (ULVAC SME-200E) with Ta<sub>2</sub>O<sub>5</sub> sources and Ar gas, and then the substrates were annealed at 500 °C for 1 h in furnace. The 10-nm HfO<sub>2</sub> (or Al<sub>2</sub>O<sub>3</sub>) layers were deposited onto the Si wafers by ALD (IPS Nano-ALD 2000) with Hf[N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>)]<sub>4</sub> (or Al(CH<sub>3</sub>)<sub>3</sub>) source.

**Preparations of ZnO precursor solutions.** A ZnO solution was prepared by dissolving 0.001 mol of zinc oxide powder (Sigma-Aldrich) into 12 ml of ammonium hydroxide (aq) (Alfa Aesar), which was kept at 4 °C for 12 h until the powder entirely had been dissolved in the solvent.

Fabrications of MICM and TFT devices. All devices were fabricated on highly B-doped p-type Si wafer substrates, which were sequentially cleaned with detergent, de-ionized water, acetone and isopropyl alcohol and exposed to ultraviolet ozone for 30 min for evaporating organic residues. The prepared ZnO precursor solution was spin-coated onto the top of the insulator-coated Si substrates with 3,000 r.p.m. for 30 s, and it then were annealed on hotplate at 300 °C for 1 h in ambient. The Au electrodes as the metal cathode (in Fig. 2) were made by contacting Au wire (a circle with diameter of 100 μm) onto the top of the ZnO layers; the Au wire was welded to a Pt-contact probe with a silver paste, and the end of the wire was brought into contact the ZnO surfaces by using a motioning probe controller with micrometre precision through an optical microscope. The Al electrodes (as a metal cathode for the MICM devices or source and drain electrodes for the TFTs) were deposited via vacuum thermal evaporation at 10<sup>-6</sup> Torr. The area of the MICM device was defined by metal shadow masks; the devices in Figs 1 and 3 have a device area of circle with 1,500 µm diameter. The TFT devices have a channel length of 50 μm and width of 1,000 μm.

**Characterization of the fabricated devices.** The current density-voltage characteristics for all devices were measured using an Agilent 4155B semiconductor parameter analyser at  $10^{-3}$  Torr in the dark. The temperature of the devices during J-V measurements was controlled using liquid nitrogen gas and ceramic-based heating elements.

# References

- 1. Sze, S. M. Physics of Semiconductor Devices (Wiley, 1981).

- 2. Nicollian, E. H. & Brews, J. R. MOS Physics and Technology (Wiley, 1982).

- Robertson, J. High dielectric constant gate oxides for metal oxide Si transistors. Rep. Prog. Phys 69, 327–396 (2006).

- Lee, B. H. et al. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Appl. Phys. Lett. 76, 1926–1928 (2000).

- Lenzlinger, M. & Snow, E. H. Fowler-Nordheim tunneling into thermally grown SiO<sub>2</sub>. J. Appl. Phys. 40, 278 (1969).

- Di Maria, D. J., Feigl, F. J. & Butler, S. R. Capture and emission of electrons at 2.4-eV-deep trap level in SiO2 film. Phys. Rev. B. 11, 5023-5030 (1975).

- 7. Jaeger, R. C. Introduction to Microelectronic Fabrication (Prentice Hall, 2001).

- Park, S. Y. et al. Low temperature, solution-processed and alkali metal doped ZnO for high performance thin film transistors. Adv. Mater. 24, 834–838 (2012).

- Lee, E. et al. Gate capacitance-dependent field-effect mobility in solutionprocessed oxide semiconductor thin-film transistors. Adv. Funct. Mat. 24, 4689–4697 (2014).

- Rose, A. Space-charge-limited current in solids. Phys. Rev. 97, 1538–1544 (1955).

- Muller, R. S. A unified approach to the theory of space-charge-limited currents in an insulator with traps. Solid State Electron. 6, 25–32 (1963).

- Lampert, M. A. Simplified theory of space-charge-limited currents in an insulator with traps. *Phys. Rev.* 103, 1648–1656 (1956).

- Vissenberg, M. C. J. M. & Matters, M. Theory of the field-effect mobility in amorphous organic transistors. *Phys. Rev. B* 57, 12964–12967 (1998).

- Verwey, J. F., Amerasekera, E. A. & Bisschop, J. The physics of SiO<sub>2</sub> layers. Rep. Prog. Phys 53, 1297–1331 (1990).

- Mora-Sero, I. et al. Selective contacts drive charge extraction in quantum dot solids via asymmetry in carrier transfer kinetics. Nat. Commun. 4, 2272 (2013).

- Ishii, H. et al. Energy level alignment and interfacial electronic structures at organic/metal and organic/organic interfaces. Adv. Mater. 11, 605–625 (1999).

- Roy, A. M., Lin, J. & Saraswat, K. C. The effect of fixed charge in tunnel-barrier contacts for Fermi-level depinning in germanium. *IEEE Electron Device Lett.* 33, 761–763 (2012).

- Roy, A. M., Lin, J. Y. J. & Saraswat, K. C. Specific contact resistivity of tunnel barrier contacts used for Fermi level depinning. *IEEE Electron Device Lett.* 31, 1077–1079 (2010).

- Batey, J. & Tierney, E. Low-temperature deposition of high-quality silicon dioxide by plasma enhanced chemical vapor deposition. J. Appl. Phys. 60, 3136 (1986).

- 20. Seki, S., Unagami, T. & Tsujiyama, B. Electron trapping levels in rf-sputtered  $Ta_2O_5$  films. *J. Vac. Sci. Technol. A* 1, 1825–1830 (1983).

- Senzaki, Y., Park, S., Chatham, H., Bartholomew, L. & Nieveen, W. Atomic layer deposition of hafnium oxide and hafnium silicate thin films using liquid precursors and ozone. J. Vac. Sci. Technol. A 22, 1175–1181 (2004).

- Puurunen, R. L. Surface chemistry of atomic layer deposition: a case study for the trimethylaluminum/water process. J. Appl. Phys. 97, 121301 (2005).

- Maloney, T. J. & Khurana, N. Transmission line pulsing techniques for circuit modeling of ESD phenomena. Proc. EOS/ESD Symp. EOS-7, 49-54 (1985).

- Golo, N. T. & Kuper, F. G. Analysis of the electrical breakdown in hydrogenated amorphous silicon thin-film transistors. *IEEE Trans. Electron Devices* 49, 1012–1018 (2002).

- Sasaki, N. Semiconductor integrated circuit device providing a protection circuit. US Patent 4423431, 27 Dec 1983.

- Lee, H.-K. & Kim, Y.-G. Protection circuit and method from electrostatic discharge of TFT-LCD. U. S. Patent 6791632 B2, 14 Sep 2004.

- Suresh, A. & Muth, J. F. Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors. *Appl. Phys. Lett.* 92, 033502 (2008)

- Nomura, K., Kamiya, T., Hirano, M. & Hosono, H. Origins of threshold voltage shifts in room-temperature deposited and annealed a-In-Ga-Zn-O thin-film transistors. Appl. Phys. Lett. 95, 013502 (2009).

- 29. Samares, K. High Permittivity Gate Dielectric Materials Ch. 6 (Springer, 2013).

- Chattopadhyay, P. & Daw, A. N. On the current transport mechanism in a metal-insulator-semiconductor (MIS) diode. Solid State Electron. 29, 555–560 (1986)

- Alivov, Y. a. I. et al. Fabrication of ZnO-based metal-insulator-semiconductor diodes by ion implantation. Solid State Electron. 48, 2343–2346 (2004).

# **Acknowledgements**

This work was supported by the Basic Research Program (2011-0018113) of National Research Foundation (NRF) of Korea and Center for Advanced Soft Electronics as Global Frontier Research Program (2013M3A6A5073177) of the Ministry of Science, ICT and Future Planning of Korea.

### **Author contributions**

E.L., K.-H.L. and Y.S.K. found the SCLC phenomena in the silicon-oxide layer-based MICM device. E.L., J.L. and Y.S.K. designed the experiments and studied in-depth about the MICM devices. E.L., J.L., K.-H.L and J.K. performed the experiments for electrical properties of the devices. E.L., J.-H.K., J.S.B., Y.D.K. and Y.P. discussed the theoretical developments and E.L. carried out numerical calculations. J.L., E.L. and Y.S.K. discussed the rectifying phenomena and the application for the MICM device as the ESD diode. E.L., J.L. and Y.S.K. wrote the manuscript based on discussion with all authors. Y.S.K. supervised the project direction including experimental and theoretical investigations, and the application for the MICM devices.

### **Additional information**

Supplementary Information accompanies this paper at http://www.nature.com/ naturecommunications

Competing financial interests: The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/reprintsandpermissions/

How to cite this article: Lee, E. et al. Direct electron injection into an oxide insulator using a cathode buffer layer. Nat. Commun. 6:6785 doi: 10.1038/ncomms7785 (2015).

(c) (i)

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this

article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/