# OPEN

# Improving carrier mobility of polycrystalline Ge by Sn doping

Kenta Moto<sup>1,2</sup>, Ryota Yoshimine<sup>1</sup>, Takashi Suemasu<sup>1</sup> & Kaoru Toko<sup>1,3</sup>

Received: 26 March 2018 Accepted: 24 September 2018 Published online: 04 October 2018 To improve the performance of electronic devices, extensive research efforts have recently focused on the effect of incorporating Sn into Ge. In the present work, we investigate how Sn composition x ( $0 \le x \le 0.12$ ) and deposition temperature  $T_d$  ( $50 \le T_d \le 200\,^{\circ}\text{C}$ ) of the  $\text{Ge}_{1-x}\text{Sn}_x$  precursor affect subsequent solid-phase crystallization. Upon incorporating 3.2% Sn, which is slightly above the solubility limit of Sn in Ge, the crystal grain size increases and the grain-boundary barrier decreases, which increases the hole mobility from 80 to  $250\,\text{cm}^2/\text{V}$  s. Furthermore, at  $T_d = 125\,^{\circ}\text{C}$ , the hole mobility reaches  $380\,\text{cm}^2/\text{V}$  s, which is tentatively attributed to the formation of a dense amorphous GeSn precursor. This is the highest hole mobility for semiconductor thin films on insulators formed below  $500\,^{\circ}\text{C}$ . These results thus demonstrate the usefulness of Sn doping of polycrystalline Ge and the importance of temperature while incorporating Sn. These findings make it possible to fabricate advanced Ge-based devices including high-speed thin-film transistors.

Research on novel materials to replace Si has been actively pursued for sustainable improvement of electronic devices. Ge has attracted attention as the most promising candidate for next-generation material because it has a higher carrier mobility than Si for both electrons and holes and is compatible with conventional Si processing <sup>1-3</sup>. Effective mobilities in Ge metal-oxide-semiconductor field-effect transistors (MOSFETs) have exceeded those in Si-MOSFETs because of the development of device technologies including gate stacks<sup>4-8</sup>. In addition, Ge has a lower crystallization temperature and grain-boundary potential than Si<sup>9-12</sup>. These properties have motivated researchers to directly synthesize polycrystalline (poly-) Ge on various substrates, where the process temperature is usually limited, to fabricate advanced thin-film transistors (TFTs) for three-dimensional integrated circuits or high-performance mobile terminals<sup>11,13</sup>.

Many crystallization techniques have been developed, including solid-phase crystallization (SPC)<sup>14-16</sup>, laser annealing<sup>17,18</sup>, chemical vapor deposition<sup>19,20</sup>, flash-lamp annealing<sup>21</sup>, the seed layer technique<sup>22</sup>, and metal-induced crystallization<sup>23-25</sup>. By using these techniques, Ge-TFTs have been fabricated on thermally oxidized Si<sup>21,26,27</sup>, glass<sup>28-31</sup>, and even flexible substrates<sup>22,32</sup>. Since gate stack technology for Ge has developed sufficiently<sup>8</sup>, recent Ge-TFTs performance is limited by the properties of the poly-Ge thin film itself<sup>21,22,26-32</sup>. Some of these TFTs exhibited effective hole mobilities greater than 100 cm<sup>2</sup>/V s<sup>22,26,28</sup>. This value is equivalent to the effective mobility of bulk-Si p-MOSFETs; however, much lower than that of bulk-Ge p-MOSFETs<sup>7,8</sup>. Besides, leakage currents are still large due to the defects in the poly-Ge thin films. To further improve Ge-TFTs and put them into practical use, a simple way to form high-mobility, low-defect Ge thin films is strongly desired.

Recently, we reported that the deposition temperature  $T_{\rm d}$  of the Ge precursor for SPC strongly influences the crystal quality and electrical properties of the resulting SPC-Ge<sup>11</sup>. This material has a hole mobility of over  $300\,{\rm cm^2/V}$  s, which is the highest mobility ever recorded for a thin film formed on insulators at temperatures below the melting point of Ge (937 °C). To further improve the electrical properties of the SPC-Ge, the present work incorporates small amount of Sn into Ge. GeSn itself has been studied as a material for high-speed transistors<sup>33–37</sup> and photonic devices<sup>37–40</sup>. In addition, the effects of incorporating Sn into poly-Ge has been getting attentions<sup>37</sup>. The results indicate that the crystallization temperature is lowered<sup>41–43</sup>, the crystal grains are enlarged<sup>44,45</sup>, and the vacancy-induced accepters are reduced<sup>46,47</sup>. However, because of the poor properties of the original Ge, the electrical properties of the resulting GeSn are worse than our recent SPC-Ge<sup>11</sup>. The present study systematically investigates the effects of  $T_{\rm d}$  and Sn concentration x in  ${\rm Ge}_{1-x}{\rm Sn}_x$  ( $x \le 0.12$ ) precursors for subsequent SPC and finds that the hole mobility dramatically increases from 80 to 380 cm<sup>2</sup>/V s.

<sup>1</sup>Institute of Applied Physics, University of Tsukuba, 1-1-1 Tennodai, Tsukuba, Ibaraki, 305-8573, Japan. <sup>2</sup>JSPS Research Fellow, 8 Ichiban-cho, Chiyoda-ku, Tokyo, 102-8472, Japan. <sup>3</sup>PRESTO, Japan Science and Technology Agency, 4-1-8 Honcho, Kawaguchi, Saitama, 332-0012, Japan. Correspondence and requests for materials should be addressed to K.T. (email: toko@bk.tsukuba.ac.jp)

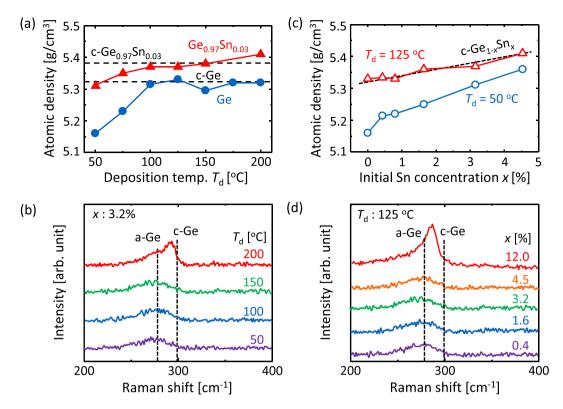

**Figure 1.** Characteristics of as-deposited  $Ge_{1-x}Sn_x$  precursors. (a) Density of Ge and  $Ge_{0.97}Sn_{0.03}$  (corresponding to x=3.2%) as a function of  $T_d$ , obtained from XRR patterns. The data for c-Ge and c-Ge<sub>0.97</sub>Sn<sub>0.03</sub> are shown by the dotted lines. (b) Raman spectra for x=3.2% with  $T_d=50$ , 100, 150, and 200 °C. (c) Density of  $Ge_{1-x}Sn_x$  with  $T_d=50$  and 125 °C as a function of x, obtained from XRR patterns. (d) Raman spectra for  $Ge_{1-x}Sn_x$  samples for  $T_d=125$  °C with  $T_d=50$ , 1.6, 3.2, 4.5, and 12.0%.

#### Results

The as-deposited  $Ge_{1-x}Sn_x$  layers, which are precursors for SPC, were analyzed by using x-ray reflectivity (XRR) and Raman spectroscopy. Figure 1(a) shows that, with increasing  $T_d$ , the atomic density of both precursors Ge and  $Ge_{0.97}Sn_{0.03}$  (corresponding to x = 3.2%) increases and asymptotically approaches that of crystals. In addition, for low  $T_{\rm d}$  ( $\leq 100\,^{\circ}$ C), Sn doping allows the atomic density of the precursor approach that of the crystals. Figure 1(b) shows that  $Ge_{0.97}Sn_{0.03}$  samples with  $T_d = 50$ , 100, and 150 °C exhibit broad peaks near 270 cm<sup>-1</sup>, corresponding to amorphous (a-) Ge. The sample with  $T_{\rm d} = 200\,^{\circ}{\rm C}$  exhibits a sharp peak near  $300\,{\rm cm^{-1}}$ , corresponding to crystalline (c-) Ge, in addition to an a-Ge peak. In this study, clear peaks corresponding to Sn-Sn or Ge-Sn vibrational modes<sup>38</sup> were not observed because of the low x and/or the measurement condition of the Raman system. Figure 1(c) shows that the atomic density of the precursor with  $T_d = 50$  and 125 °C increases with increasing initial Sn concentration x. Over the entire x range  $0 \le x < 0.05$ , the atomic density for  $T_d = 125$  °C exceeds that for  $T_d = 50$  °C and is equivalent to that of crystalline GeSn. Figure 1(d) shows the x dependence of Raman spectra at  $T_{\rm d} = 125\,^{\circ}{\rm C}$ . The samples with x = 0.4% - 4.5% exhibit the a-Ge peak, whereas the sample with x = 12% exhibits both the crystalline Ge peak and the a-Ge peak. The study using transmission electron microscopy confirmed that the Ge layer with  $T_d = 125$  °C is completely amorphous and contained no crystals. The crystallinity, defined as the ratio of the Raman peak intensity of c-Ge to that of a-Ge<sup>11</sup>, was found to be 56% for the Ge<sub>0.97</sub>Sn<sub>0.03</sub> sample with  $T_d = 200\,^{\circ}\text{C}$  [Fig. 1(b)] and 69% for the Ge<sub>0.88</sub>Sn<sub>0.12</sub> sample with  $T_d = 125\,^{\circ}\text{C}$  [Fig. 1(d)]. These results indicate that crystalline nuclei start to form in the a-Ge<sub>1-x</sub>Sn<sub>x</sub> layer for x = 3.2% at  $T_d > 150$  °C and x > 4.5% at  $T_d = 125$  °C. This behavior is consistent with the previous reports that the crystallization of a-Ge<sub>1-x</sub>Sn<sub>x</sub> is facilitated by increasing  $x^{41-43}$  and  $T_d^{-11}$ . Thus, these optical studies reveal that both x and  $T_d$  strongly influence the atomic density and crystalline state in the precursor layer.

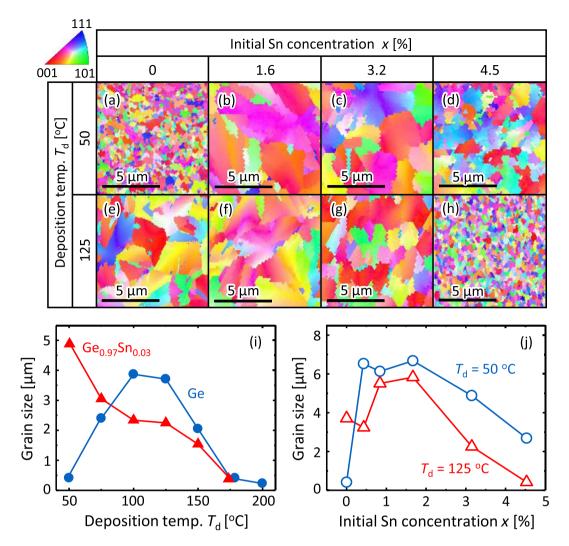

The samples were then annealed for 5 h to induce SPC at a growth temperature  $T_{\rm g}=450\,^{\circ}{\rm C}$ . Figures 2(a–j) show the crystal-orientation maps obtained by electron backscattering diffraction (EBSD), which indicate that the grain size dramatically varies with both x and  $T_{\rm d}$ . Figure 2(i) shows that, with respect to  $T_{\rm d}$ , the grain size evolves differently for Ge and GeSn. For Ge, the grain size increases with increasing  $T_{\rm d}$  and then begins to decrease. As a result, the grain size peaks around  $100 \le T_{\rm d} \le 150\,^{\circ}{\rm C}$ . Conversely, the grain size of  ${\rm Ge}_{0.97}{\rm Sn}_{0.03}$  decreases with increasing  $T_{\rm d}$ . Note that the grain size of  ${\rm Ge}_{0.97}{\rm Sn}_{0.03}$  greatly exceeds that of Ge when the substrate is not heated ( $T_{\rm d}=50\,^{\circ}{\rm C}$ ). Figure 2(j) shows that, for both  $T_{\rm d}=50$  and 125 °C, the grain size of  ${\rm Ge}_{1-x}{\rm Sn}_x$  strongly depends on x and peaks at x=1.6%. For all samples containing  ${\rm Sn}$  (x>0), the grain size is larger at  $T_{\rm d}=50\,^{\circ}{\rm C}$  than at  $T_{\rm d}=125\,^{\circ}{\rm C}$ . The maximum grain size is approximately 7  $\mu{\rm m}$ , which is the largest grain size among semiconductor layers formed by SPC.

**Figure 2.** Grain size of SPC-Ge<sub>1-x</sub>Sn<sub>x</sub> layers. (**a**-**h**) EBSD images organized as a matrix composed of  $T_{\rm d}$  (50 and 125 °C) rows and x (0, 1.6, 3.2, and 4.5%) columns. Average grain size determined by EBSD for (**i**) Ge and Ge<sub>0.97</sub>Sn<sub>0.03</sub> samples as a function of  $T_{\rm d}$  and for (**j**) Ge<sub>1-x</sub>Sn<sub>x</sub> samples for  $T_{\rm d}$  = 50 and 125 °C as a function of x. Here,  $T_{\rm g}$  = 450 °C.

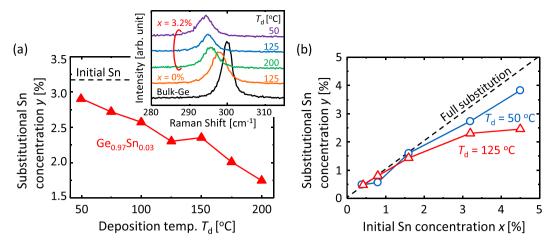

We investigate the origin of this evolution in grain size from the perspective of substitutional Sn concentration y in SPC-GeSn. Since the lattice constant of  $Ge_{1-y}Sn_y$  depends on y, y can be determined from the Ge-Ge peak position in the Raman spectrum<sup>34,38</sup>. We therefore determine y from the Raman spectra by using the following equation proposed by Lin et al.<sup>34</sup>:

$$\Delta\omega(y) = ay + \Delta\omega_{\text{strain}} \tag{1}$$

where  $\Delta\omega(y)$  is the difference between the shift in the Ge-Ge peak of  $\operatorname{Ge}_{1-y}\operatorname{Sn}_y[\omega(y)]$  and that of the c-Ge wafer  $(\omega_{\operatorname{Ge}})$ , a is a constant of 82 cm<sup>-134</sup>, and  $\Delta\omega_{\operatorname{strain}}$  is the shift due to strain. In general, the Ge-Ge peak of  $\operatorname{Ge}[\omega(0)]$  on a glass substrate shifts to the lower wavenumber than  $\omega_{\operatorname{Ge}}$  because of the strain induced by the difference between the thermal expansion coefficients of Ge and the glass substrate 14,44. Assuming that the thermal strain of  $\operatorname{Ge}_{1-y}\operatorname{Sn}_y$  is the same as that of Ge because y is low (<5%), Eq. (1) may be rewritten as

$$\Delta\omega(y) - \Delta\omega_{\text{strain}} = (\omega_{\text{Ge}} - \omega(y)) - (\omega_{\text{Ge}} - \omega(0)) = \omega(0) - \omega(y) = ay$$

(2)

Therefore, we estimate y from Raman spectra, of which examples are shown in the inset of Fig. 3(a). Figure 3(a) shows that y decreases with increasing  $T_d$ . This suggests that higher  $T_d$  makes Sn precipitate, as estimated from the difference between x (=3.2%) and y. This result is likely caused by enhanced surface migration of Sn during precursor deposition. Figure 3(b) shows that y increases with increasing x, which is accompanied by Sn precipitation for x > 1.6%. This behavior can be explained from the perspective of the solid solubility of Sn in Ge  $(1-2\%)^{37}$ . It is well known that y exceeds the solid solubility for GeSn thin films grown in a non-equilibrium system including SPC<sup>41-43</sup>. The relationship between y and growth temperature in this study is approximately consistent with the previous reports. Considering that c-Sn facilitates Ge nucleation<sup>42</sup>, the decrease in grain size at higher  $T_d$  and for x > 1.6% [Fig. 2(i,j)] is attributed to the promotion of Ge nucleation because of Sn precipitation. In contrast, when

**Figure 3.** Substitutional Sn concentration y of SPC-Ge<sub>1-x</sub>Sn<sub>x</sub> layers. (a) y for Ge<sub>0.97</sub>Sn<sub>0.03</sub> samples as a function of  $T_d$  obtained from Raman spectra, some examples of which are shown in the inset. The dotted line corresponds to the initial Sn concentration (x = 3.2%). (b) y for Ge<sub>1-x</sub>Sn<sub>x</sub> samples for  $T_d = 50$  and 125 °C as a function of x. The dotted line shows the line when the initial Sn is fully substituted. Here,  $T_o = 450$  °C.

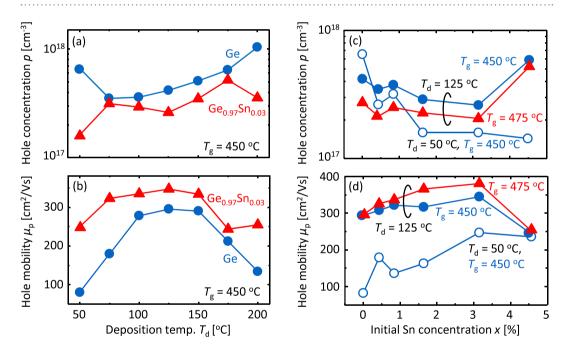

**Figure 4.** Electrical properties of the SPC-Ge<sub>1-x</sub>Sn<sub>x</sub> layers. (a) Hole concentration p and (b) hole mobility  $\mu_p$  for Ge and Ge<sub>0.97</sub>Sn<sub>0.03</sub> samples formed at  $T_g = 450$  °C as a function of  $T_d$ , where  $T_g = 450$  °C. (c) p and (d)  $\mu_p$  for Ge<sub>1-x</sub>Sn<sub>x</sub> samples for  $T_d = 50$  and 125 °C as a function of x, where  $T_g = 450$  and 475 °C.

Sn does not precipitate ( $x \le 1.6\%$ ), the grain size increases with increasing x [Fig. 2(j)]. The mechanism leading to this result remains unclear, but it may possibly be due to Sn doping weakening the amorphous bonds in Ge, which could enhance the lateral growth of crystals.

We used Hall-effect measurements to evaluate the electrical properties of the SPC-Ge $_{1-x}$ Sn $_x$  layers. All samples showed p-type conduction, similar to conventional undoped poly-GeSn $_1^{45,46}$ . This is because the vacancy in Ge provides shallow acceptor levels that generate holes at room temperature $_1^{47}$ . Figure 4(a) shows that Ge $_{0.97}$ Sn $_{0.03}$  samples have lower hole concentration p than Ge samples for all  $T_d$ . Figure 4(b) shows that Ge $_{0.97}$ Sn $_{0.03}$  has higher hole mobility  $\mu_p$  than Ge for all  $T_d$ , whereas Ge $_{0.97}$ Sn $_{0.03}$  has smaller grains than Ge for  $T_d > 75$  °C [Fig. 2(i)]. Figure 4(c,d) show that the electrical properties of Ge $_{1-x}$ Sn $_x$  are influenced by x,  $T_d$ , and  $T_g$ . Figure 4(c) shows that Sn doping effectively lowers p, except for the samples with p and p and

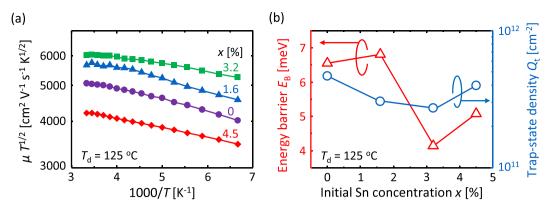

**Figure 5.** Electrical characterization of grain boundaries in SPC-Ge<sub>1-x</sub>Sn<sub>x</sub> layers. (a) Arrhenius plot of  $\mu T^{1/2}$  for samples with x = 0, 1.6, 3.2, and 4.5%. (b) Energy barrier  $E_{\rm B}$  and trap-state density  $Q_{\rm t}$  for grain boundaries as a function of x. Here,  $T_{\rm d} = 125\,^{\circ}{\rm C}$  and  $T_{\rm g} = 475\,^{\circ}{\rm C}$ .

with increasing x and peaks at x=3.2%. The reason why both p and  $\mu_{\rm p}$  increase and decrease at x=4.5% is likely because of the decrease in crystalline quality caused by significant Sn precipitation, as suggested by Figs 2(j) and 3(b). The samples with  $T_{\rm d}=125\,^{\circ}{\rm C}$  exhibit significantly higher  $\mu_{\rm p}$  than the sample with  $T_{\rm d}=50\,^{\circ}{\rm C}$ . Furthermore, the higher  $T_{\rm g}$  provides a higher hole mobility  $\mu_{\rm p}$ . Consequently, the sample with x=3.2%,  $T_{\rm d}=125\,^{\circ}{\rm C}$ , and  $T_{\rm g}=475\,^{\circ}{\rm C}$  exhibits the maximum  $\mu_{\rm p}$  of  $380\,{\rm cm^2/V}$  s.

Considering that grain-boundary scattering is one factor behind decreased mobility, the hole mobility of Ge approaches the trend of grain size in Fig. 2(i). In contrast, the hole mobility of  $Ge_{0.97}Sn_{0.03}$  does not follow this trend. These results suggest that  $\mu_p$  of GeSn is strongly influenced by factors other than grain size. According to the carrier conduction model proposed by Seto for polycrystalline semiconductors<sup>9</sup>, the carrier mobility limited by grain-boundary scattering can be determined by using

$$\mu T^{1/2} = \frac{Lq}{\sqrt{2\pi m^* k}} \exp\left(-\frac{E_B}{kT}\right) \tag{3}$$

where  $\mu$  is the carrier mobility,  $E_{\rm B}$  is the energy barrier of the grain-boundary, T is the absolute temperature, L is the grain size,  $m^*$  is the effective mass, and k is the Boltzmann constant. Figure 5(a) shows that the Arrhenius plot of  $\mu T^{1/2}$  makes almost-downward-sloping straight lines for all x; however, the lines are slightly curved at high temperatures (1000/T < 4) for x = 0–3.2%. The trap-state density  $Q_{\rm t}$  in the grain boundaries can be determined by using<sup>8</sup>

$$Q_t = \frac{\sqrt{8\varepsilon NE_B}}{q} \tag{4}$$

where N is the carrier concentration,  $\varepsilon$  is the dielectric permittivity, and q is the elementary charge. Figure 5(b) shows that  $E_{\rm B}$  and  $Q_{\rm t}$  determined by the slope of  $\mu T^{1/2}$  at low temperatures (1000/T>4) depend on x. Note that the minimum values of  $E_{\rm B}$  and  $Q_{\rm t}$  are obtained for the highest  $\mu_{\rm p}$  sample with x = 3.2% at  $T_{\rm d}$  = 125 °C.

#### Discussion

The hole mobility of SPC-Ge<sub>1-x</sub>Sn<sub>x</sub> strongly depends on both x and  $T_d$ : a maximum mobility of 380 cm<sup>2</sup>/V s occurs for the sample with x=3.2%,  $T_{\rm d}=125\,^{\circ}{\rm C}$ , and  $T_{\rm g}=475\,^{\circ}{\rm C}$  [Fig. 4(d)]. The reason is discussed as follows. According to Matthiessen's rule and Irvin's curve of poly-Ge with p on the order of  $10^{17}\,{\rm cm}^{-3\,1}$ , when  $\mu_{\rm p}$  is less than about 250 cm<sup>2</sup>/V s, it is primarily limited by grain-boundary scattering as well as ordinary polycrystals. Conversely, when  $\mu_{\rm p}$  exceeds 250 cm<sup>2</sup>/V s, impurity scattering influences  $\mu_{\rm p}$  in addition to grain-boundary scattering. For  $T_d = 50$  °C,  $\mu_p$  increases from 80 to 250 cm<sup>2</sup>/V s because of Sn incorporation [Fig. 4(d)], which is attributed to the reduction of grain-boundary scattering, because of increased grain size [Fig. 2(j)] and likely because of the reduction of  $E_{\rm B}$ . By increasing  $T_{\rm d}$  to 125 °C,  $\mu_{\rm p}$  increases for all x, reaching approximately 300 cm<sup>2</sup>/V s for x < 4.5%. We examined the effect of  $T_d$  in our previous study on SPC-Ge<sup>11</sup>: substrate heating at appropriate temperature during precursor deposition ( $T_d = 125$  °C) reduces  $E_B$  and dramatically enhances  $\mu_D$ . This is explained from the perspective of the atomic density of the amorphous precursor. Moreover, increasing  $\dot{T}_{\rm g}$  to 475 °C further improves  $\mu_p$  for all x [Fig. 4(d)]. This is likely due to the reduction of impurity scattering because of decreased p [Fig. 4(c)], which corresponds to the reduction of vacancy-related defects<sup>14,30</sup>. Even for  $T_d = 125$  °C,  $\mu_p$  peaks at x = 3.2% [Fig. 4(d)], although the grain size is relatively small [Fig. 2(g)]. The high  $\mu_p$  is attributed to reduced impurity and grain-boundary scattering due to the decrease in p [Fig. 4(c)] and  $E_B$  [Fig. 5(b)], respectively. The decrease in p is likely caused by Sn passivating the vacancy in Ge, as mentioned in previous studies  $^{37,46}$ . Meanwhile, the SPC of a-GeSn progresses while sweeping Sn, which cannot be solid-solved, to the growth front 43. Considering that the reduction of  $E_B$  is possibly due to Sn existing at the grain-boundary, the Sn may passivate dangling bonds and thereby reduce  $Q_t$  and  $E_B$  [Fig. 5(b)]. Because excessively large x (>3.2%) deteriorates crystal

quality [Fig. 2(j)] and  $\mu_p$  [Fig. 4(d)] due to Sn precipitation, x should be slightly larger than the solubility limit. Therefore, the reduction of both  $E_B$  and p, by controlling x and  $T_d$ , leads to the maximum mobility of 380 cm²/V s.

In conclusion, the precursor conditions of both the initial Sn concentration x and the deposition temperature  $T_{\rm d}$  strongly influence the crystalline quality and electrical properties of SPC-Ge<sub>1-x</sub>Sn<sub>x</sub>. We obtain a grain size of approximately 7  $\mu$ m for x=1.6% and  $T_{\rm d}=50\,^{\circ}{\rm C}$ , which is the maximum value reported to date for semiconductor films formed by SPC. Conversely, the hole mobility  $\mu_{\rm p}$  of GeSn reflects the energy barrier  $E_{\rm B}$  and the hole concentration p rather than the grain size. The sample with x=3.2% and  $T_{\rm d}=125\,^{\circ}{\rm C}$  has  $E_{\rm B}=4.1\,{\rm meV}$  and  $p=2.1\times10^{17}\,{\rm cm^{-3}}$ , resulting in  $\mu_{\rm p}=380\,{\rm cm^2/V}$  s, which is the highest hole mobility among semiconductor layers formed on insulators at less than 500 °C. Since the performance of Ge-TFTs is limited by the properties of poly-Ge thin films, such high  $\mu_{\rm p}$  and low p will directly improve the field effect mobility and leakage current in the Ge-TFTs. Thus, by controlling x and  $T_{\rm d}$  in the Ge<sub>1-x</sub>Sn<sub>x</sub> precursor for SPC, an excellent semiconductor thin film forms at low temperature. The process developed herein is simple enough for practical fabrication of high-speed TFTs for advanced system-in-displays or three-dimensional integrated circuits.

#### Methods

**Sample preparation.** The  $Ge_{1-x}Sn_x$  ( $0 \le x \le 0.12$ ) precursors were deposited on  $SiO_2$  glass substrates by using the Knudsen cells of a molecular beam deposition system (base pressure of  $5 \times 10^{-7}$  Pa). The deposition rate of Ge was fixed at 1.0 nm/min, whereas that of Sn was adjusted to obtain the targeted GeSn composition. The deposition time was 100 min. The Ge and Sn source, manufactured by Furuuchi Chemical Corporation, had a purity of 99.999% and 99.9999%, respectively. The substrate temperature  $T_d$  during the deposition ranged from 50 to 200 °C. Note that  $T_d$  spontaneously rises from room temperature to 50-60 °C without heating the substrate because of the thermal energy radiated from the Knudsen cell, and the notation for this temperature is simplified as  $T_d = 50$  °C. The samples were then loaded into a conventional tube furnace in a  $N_2$  atmosphere and annealed for 5 h at 450 or 475 °C to induce SPC.

**Material characterization.** Rutherford backscattering spectrometry was used to determine x in  $Ge_{1-x}Sn_x$  to be 0, 0.4, 0.8, 1.6, 3.2, 4.5, and 12.0%. XRR was done by using a Rigaku SmartLab, and Raman spectroscopy was done by using a Photon Design RSM-310 with a laser wavelength of 532 nm. The EBSD analyses were done by using a JEOL JSM-7001F with a TSL OIM analysis attachment. The Hall effect was measured by using the Van der Pauw method with a Bio-Rad HL5500PC. The hole mobility and hole concentration were averaged over five measurements for each sample.

#### References

- 1. Irvin, J. C. & Sze, S. M. Resistivity, mobility and impurity levels in GaAs, Ge, and Si at 300 degrees. Solid. State. Electron. 11, 599–602 (1968).

- 2. Nayfeh, A., Chui, C. O., Yonehara, T. & Saraswat, K. C. Fabrication of high-quality p-MOSFET in Ge Grown heteroepitaxially on Si. *IEEE Electron Device Lett.* 26, 311–313 (2005).

- 3. Brunco, D. P. et al. Germanium MOSFET Devices: Advances in Materials Understanding, Process Development, and Electrical Performance. J. Electrochem. Soc. 155, H552 (2008).

- $4.\ \ Pillarisetty, R.\ Academic\ and\ industry\ research\ progress\ in\ germanium\ nanodevices.\ \textit{Nature}\ \textbf{479}, 324-328\ (2011).$

- 5. Zhang, R., Iwasaki, T., Taoka, N., Takenaka, M. & Takagi, Š. High-Mobility Ge pMOSFET With 1-nm EOT Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge Gate Stack Fabricated by Plasma Post Oxidation. *IEEE Trans. Electron Devices* **59**, 335–341 (2012).

- Jung, W.-S., Park, J.-H., Nainani, A., Nam, D. & Saraswat, K. C. Fluorine passivation of vacancy defects in bulk germanium for Ge metal-oxide-semiconductor field-effect transistor application. Appl. Phys. Lett. 101, 72104 (2012).

- Yamamoto, K., Sada, T., Wang, D. & Nakashima, H. Dramatic enhancement of low electric-field hole mobility in metal source/drain Ge p-channel metal-oxide-semiconductor field-effect transistors by introduction of Al and Hf into SiO<sub>2</sub>/GeO<sub>2</sub> gate stack. Appl. Phys. Lett. 103, 122106 (2013).

- 8. Toriumi, A. & Nishimura, T. Germanium CMOS potential from material and process perspectives: Be more positive about germanium. *Jpn. J. Appl. Phys.* 57, 010101 (2018).

- 9. Seto, J. W. Y. The electrical properties of polycrystalline silicon films. J. Appl. Phys. 46, 5247–5254 (1975).

- Watakabe, H., Sameshima, T., Kanno, H., Sadoh, T. & Miyao, M. Electrical and structural properties of poly-SiGe film formed by pulsed-laser annealing. J. Appl. Phys. 95, 6457–6461 (2004).

- 11. Toko, K., Yoshimine, R., Moto, K. & Suemasu, T. High-hole mobility polycrystalline Ge on an insulator formed by controlling precursor atomic density for solid-phase crystallization. *Sci. Rep.* 7, 16981 (2017).

- 12. Dushaq, G., Rasras, M. & Nayfeh, A. Low temperature deposition of germanium on silicon using Radio Frequency Plasma Enhanced Chemical Vapor Deposition. *Thin Solid Films* 636, 585–592 (2017).

- 13. Hu, S., Leu, P. W., Marshall, A. F. & McIntyre, P. C. Single-crystal germanium layers grown on silicon by nanowire seeding. *Nat. Nanotechnol.* 4, 649–53 (2009).

- 14. Toko, K., Nakao, I., Sadoh, T., Noguchi, T. & Miyao, M. Electrical properties of poly-Ge on glass substrate grown by two-step solid-phase crystallization. Solid. State. Electron. 53, 1159–1164 (2009).

- 15. Tsao, C.-Y., Huang, J., Hao, X., Campbell, P. & Green, M. A. Formation of heavily boron-doped hydrogenated polycrystalline germanium thin films by co-sputtering for developing p + emitters of bottom cells. Sol. Energy Mater. Sol. Cells 95, 981–985 (2011).

- Jung, H.-W., Jung, W.-S., Yu, H.-Y. & Park, J.-H. Electrical properties of phosphorus-doped polycrystalline germanium formed by solid-phase and metal-induced crystallization. J. Alloys Compd. 561, 231–233 (2013).

- 17. Yeh, W., Chen, H., Huang, H., Hsiao, C. & Jeng, J. Superlateral growth of a-Ge film by excimer laser annealing. *Appl. Phys. Lett.* **93**, 94103 (2008).

- 18. Sakaike, K., Higashi, S., Murakami, H. & Miyazaki, S. Crystallization of amorphous Ge films induced by semiconductor diode laser annealing. *Thin Solid Films* **516**, 3595–3600 (2008).

- 19. Matsui, T., Kondo, M., Ogata, K., Ozawa, T. & Isomura, M. Influence of alloy composition on carrier transport and solar cell properties of hydrogenated microcrystalline silicon-germanium thin films. *Appl. Phys. Lett.* **89**, 142115 (2006).

- Tada, M. et al. Low Temperature Germanium Growth on Silicon Oxide Using Boron Seed Layer and In Situ Dopant Activation. J. Electrochem. Soc. 157, H371–H376 (2010).

- 21. Usuda, K. et al. High-performance poly-Ge short-channel metal-oxide-semiconductor field-effect transistors formed on SiO<sub>2</sub> layer by flash lamp annealing. Appl. Phys. Express 7, 56501 (2014).

- 22. Asadirad, M. et al. High-Performance Flexible Thin-Film Transistors Based on Single-Crystal-Like Germanium on Glass. Adv. Electron. Mater. 2 (2016).

- 23. Wang, Z. M., Wang, J. Y., Jeurgens, L. P. H., Phillipp, F. & Mittemeijer, E. J. Origins of stress development during metal-induced crystallization and layer exchange: Annealing amorphous Ge/crystalline Al bilayers. *Acta Mater.* 56, 5047–5057 (2008).

- 24. Hu, S., Marshall, A. F. & McIntyre, P. C. Interface-controlled layer exchange in metal-induced crystallization of germanium thin films. *Appl. Phys. Lett.* **97**, 82104 (2010).

- 25. Toko, K. et al. Low-temperature (180 °C) formation of large-grained Ge (111) thin film on insulator using accelerated metal-induced crystallization. Appl. Phys. Lett. 104, 22106 (2014).

- 26. Liao, C.-Y. et al. High-performance p-channel thin-film transistors with lightly doped n-type excimer-laser-crystallized germanium films. *Jpn. J. Appl. Phys.* **56**, 06GF08 (2017).

- 27. Huang, W.-H. et al. Enabling n-type polycrystalline Ge junctionless FinFET of low thermal budget by in situ doping of channel and visible pulsed laser annealing. Appl. Phys. Express 10, 26502 (2017).

- 28. Sadoh, T., Kamizuru, H., Kenjo, A. & Miyao, M. Low-temperature formation (<500 °C) of poly-Ge thin-film transistor with NiGe Schottky source/drain. *Appl. Phys. Lett.* **89**, 192114 (2006).

- 29. Kabuyanagi, S., Nishimura, T., Nagashio, K. & Toriumi, A. Impacts of oxygen passivation on poly-crystalline germanium thin film transistor. *Thin Solid Films* 557, 334–337 (2014).

- 30. Kasahara, K. et al. Electrical properties of pseudo-single-crystalline germanium thin-film-transistors fabricated on glass substrates. Appl. Phys. Lett. 107, 142102 (2015).

- 31. Suzuki, T., Joseph, B. M., Fukai, M., Kamiko, M. & Kyuno, K. Low-temperature (330 °C) crystallization and dopant activation of Ge thin films via AgSb-induced layer exchange: Operation of an n-channel polycrystalline Ge thin-film transistor. *Appl. Phys. Express* 10, 95502 (2017).

- 32. Higashi, H. et al. A crystalline germanium flexible thin-film transistor. Appl. Phys. Lett. 111, 222105 (2017).

- 33. Sau, J. & Cohen, M. Possibility of increased mobility in Ge-Sn alloy system. Phys. Rev. B 75, 45208 (2007).

- 34. Lin, H., Chen, R., Huo, Y., Kamins, T. I. & Harris, J. S. Raman study of strained Ge<sub>1-x</sub>Sn<sub>x</sub> alloys. Appl. Phys. Lett. 98, 261917 (2011).

- Gupta, S., Huang, Y.-C., Kim, Y., Sanchez, E. & Saraswat, K. C. Hole Mobility Enhancement in Compressively Strained Ge<sub>0.93</sub>Sn<sub>0.07</sub> pMOSFETs. IEEE Electron Device Lett. 34, 831–833 (2013).

- 36. Uchida, N. et al. Carrier and heat transport properties of polycrystalline GeSn films on SiO<sub>2</sub>. Appl. Phys. Lett. 107, 232105 (2015).

- Zaima, S. et al. Growth and applications of GeSn-related group-IV semiconductor materials. Sci. Technol. Adv. Mater. 16, 43502 (2015).

- 38. Fournier-Lupien, J. H. *et al.* Strain and composition effects on Raman vibrational modes of silicon-germanium-tin ternary alloys. *Appl. Phys. Lett.* **103**, 10–15 (2013).

- 39. Homewood, K. P. & Lourenço, M. A. The rise of the GeSn laser. Nat. Photonics 9, 78-79 (2015).

- 40. Wirths, S. et al. Lasing in direct-bandgap GeSn alloy grown on Si. Nat. Photonics 9, 88-92 (2015).

- 41. Li, H., Brouillet, J., Salas, A., Wang, X. & Liu, J. Low temperature growth of high crystallinity GeSn on amorphous layers for advanced optoelectronics. *Opt. Mater. Express* 3, 1385 (2013).

- 42. Toko, K., Oya, N., Saitoh, N., Yoshizawa, N. & Suemasu, T. 70 °C synthesis of high-Sn content (25%) GeSn on insulator by Sn-induced crystallization of amorphous Ge. Appl. Phys. Lett. 106, 82109 (2015).

- 43. Matsumura, R. *et al.* Low-temperature (∼180 °C) position-controlled lateral solid-phase crystallization of GeSn with laser-anneal seeding. *Appl. Phys. Lett.* **107**, 262106 (2015).

- 44. Kurosawa, M., Taoka, N., Ikenoue, H., Nakatsuka, O. & Zaima, S. Large grain growth of Ge-rich Ge<sub>1-x</sub>Sn<sub>x</sub> (x≈0.02) on insulating surfaces using pulsed laser annealing in flowing water. *Appl. Phys. Lett.* **104**, 61901 (2014).

- 45. Sadoh, T., Kai, Y., Matsumura, R., Moto, K. & Miyao, M. High carrier mobility of Sn-doped polycrystalline-Ge films on insulators by thickness-dependent low-temperature solid-phase crystallization. *Appl. Phys. Lett.* 109, 232106 (2016).

- 46. Takeuchi, W. et al. High hole mobility tin-doped polycrystalline germanium layers formed on insulating substrates by low-temperature solid-phase crystallization. Appl. Phys. Lett. 107, 22103 (2015).

- 47. Höhler, H., Atodiresei, N., Schroeder, K., Zeller, R. & Dederichs, P. H. Vacancy complexes with oversized impurities in Si and Ge. *Phys. Rev. B Condens. Matter Mater. Phys.* 71, 1–7 (2005).

#### Acknowledgements

This work was financially supported by the Grant-in-aid for JSPS Research Fellow (No. 17J00544), the Nanotech CUPAL, and JST PRESTO (No. JPMJPR17R7). The authors are grateful to Dr. T. Sakurai and Dr. D. Sekiba (University of Tsukuba) for assistance with the Hall effect and Rutherford backscattering spectrometry measurements, respectively, and Dr. N. Fukata (NIMS) for assistance with the Raman measurements. EBSD measurements were conducted at the International Center for Young Scientists at NIMS.

## **Author Contributions**

K.T. conceived and designed the experiments. K.M. and R.Y. conducted the experiments and analyses. K.T. and T.S. managed the research and supervised the project. All the authors discussed the results and commented on the manuscript.

### **Additional Information**

Competing Interests: The authors declare no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2018