# Article Investigation of Intra-Nitride Charge Migration Suppression in SONOS Flash Memory

Seung-Dong Yang <sup>1</sup>, Jun-Kyo Jung <sup>1</sup>, Jae-Gab Lim <sup>1</sup>, Seong-gye Park <sup>2</sup>, Hi-Deok Lee <sup>1</sup> and Ga-Won Lee <sup>1,\*</sup>

- <sup>1</sup> Department of Electronics Engineering, Chungnam National University, Daejeon 305-764, Korea; sdyang83@gmail.com (S.-D.Y.); jjk1006@cnu.ac.kr (J.-K.J.); jaegabi@cnu.ac.kr (J.-G.L.); hdlee@cnu.ac.kr (H.-D.L.)

- <sup>2</sup> SK Hynix Inc., Gyeongchung-daero, Bubal-eub, Icheon-si 17336, Korea; pskg@sk.com

- \* Correspondence: gawon@cnu.ac.kr; Tel.: +82-42-821-7702; Fax: +82-42-823-9544

Received: 24 April 2019; Accepted: 27 May 2019; Published: 29 May 2019

Abstract: In order to suppress the intra-nitride charge spreading in 3D Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) flash memory where the charge trapping layer silicon nitride is shared along the cell string, N<sub>2</sub> plasma treated on the silicon nitride is proposed. Experimental results show that the charge loss decreased in the plasma treated device after baking at 300 °C for 2 h. To extract trap density according to the location in the trapping layer, capacitance-voltage analysis was used and N<sub>2</sub> plasma treatment was shown to be effective to restrain the interface trap formation between blocking oxide and silicon nitride. Moreover, from X-ray Photoelectron Spectroscopy, the reduction of Si-O-N bonding was observed.

**Keywords:** SONOS; flash memory; charge spreading; plasma treatment; Oxygen-related trap; data retention

### 1. Introduction

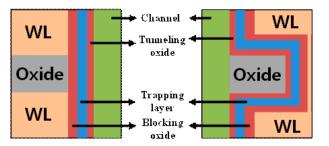

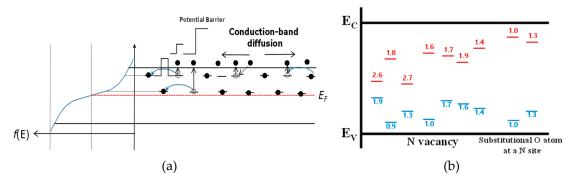

The NAND flash memory market is continuously growing by the successive introduction of mass data storage applications in portable electronic devices, such as USB memory and solid-state drives for tablet PCs and laptops [1]. The cell price as well as bit density are key factors in this application. Until now, it has been possible to reduce the bit cost and increase the bit density through the linear scaling down of cell size, which has been achieved by advanced lithography [2]. Recently, however, the NAND Flash memory industry has faced a scaling limitation of the conventional floating gate (FG) NAND cell. In order to find an alternative technology, Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) device has received attention from researchers, as it provides simpler process steps, lower cell to cell coupling, and virtual immunity to stress-induced leakage current (SILC), when compared to FG [3–5]. However, the down-scaling process is still challenging in SONOS when attempted beyond the 30nm generation. To overcome the problem, SONOS has been fabricated with 3-dimesional (3D) structures such as BiCS [6], P-BiCS [7], TCAT [8], VG-NAND [9] and SMArT [10]. However, in the 3D SONOS structure, the charge trapping layer is not isolated but shared in a cell string, as shown in Figure 1. Due to this continuous trapping layer structure in the 3D scheme, the intra-nitride charge spreading can be a serious problem for data retention properties [11,12]. Charge spreading in silicon nitride has previously been studied in NROM devices, where a trapped charge is locally distributed, and recent research has reported that charge spreading is driven by the spatial concentration difference [13,14]. Figure 2a shows the probable charge spreading mechanism in silicon nitride. For trapped charges in deep-level sites, hopping can happen, yet the possibility is very low because of the long distance between deep-level sites. In the case of shallow-level sites, however, the hopping possibility increases due to relatively high concentration of trapping sites. Charge spreading via the shallow trap sites can be

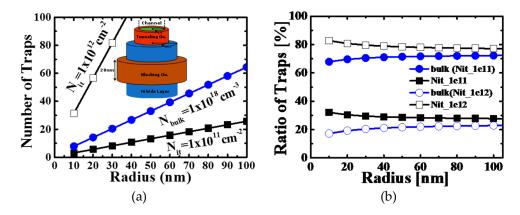

accelerated by conduction band diffusion of thermionic emitted carriers from the trap sites. Figure 2b shows trap energy levels in silicon nitride, and we can see that substitutional oxygen atoms at nitrogen vacancy causes a shallow-level trap site. Considering that the oxygen incorporation is active near the oxide/nitride interface, it is reasonable to estimate that the oxygen and nitrogen vacancy related defects will be formed near the nitride/oxide interface and that they are mainly located in shallow energy level, as reported in [15–17]. Figure 3 shows comparison results on the total number of bulk (N<sub>Bulk</sub>) and interface traps (N<sub>int</sub>) according to the channel radius of a cylinder type 3D SONOS device. Assuming N<sub>Bulk</sub> =  $1.0 \times 10^{18}$  cm<sup>-3</sup>, relative importance of N<sub>int</sub> increases as the channel radius decreases. Therefore, when the energy level of N<sub>int</sub> is shallow, like as the oxygen related traps, the charge spreading via the interface trap sites becomes more critical with shrinkage of device dimension occurring.

Figure 1. The charge trapping layer structure of (a) BiCS 3D NAND and (b) TCAT 3D NAND.

**Figure 2.** (a) Conduction mechanism of programmed Silicon-Oxide-Nitride-Oxide-Silicon (SONOS) memories, (b) energy level of silicon nitride.

**Figure 3.** (a) Total real number of interfaces and bulk traps and (b) the percentage of traps depending on the channel radius of the cylindrical 3D SONOS device. Here, the radius (R<sub>in</sub> in inset figure) was in the range of 10 to 100 nm, trapping layer thickness was 5 nm and gate length was 20 nm.

In this study, N<sub>2</sub> plasma treatment on silicon nitride is proposed to suppress the intra-nitride charge spreading by controlling the interface trap formation. To extract the trap density quantitatively,

3 of 7

the capacitance-voltage (C–V) analysis was made based on the measurement results by a LCR meter (HP 4284A, Agilent, Santa Clara, CA, USA) at a small signal frequency of 1 MHz. To find the bonding state changes induced by plasma treatment, X-ray Photoelectron Spectroscopy (XPS) was also measured with a K-Alpha+ spectrometer (ThermoFisher Scientific, East Grinstead, UK).

## 2. Experiments

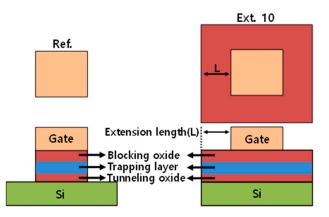

To fabricate SONOS structure, 6 nm SiO<sub>2</sub> for tunneling oxide was thermally grown on a prime grade p-type Si substrate with high-purity oxygen gas via dry oxidation furnace. After the oxidation of Si, N<sub>2</sub> plasma treatment was carried out for 30 sec. The flow rate of nitrogen gas was 45 sccm at a pressure of 10 mTorr, and a plasma power of 200 W. Silicon nitride as a charge storage layer was deposited by low-pressure chemical vapor deposition (LPCVD) at 825 °C with a gas flow rate of SiH<sub>2</sub>Cl<sub>2</sub>:NH<sub>3</sub> = 170:70 sccm on the tunneling oxide. In this experiment, the nitride thickness varied between 7 nm, 15 nm, and 20 nm to extract the trap density by C–V analysis. Following this, N<sub>2</sub> plasma treatment was performed once again on the top of nitride. Then, blocking oxide of 10nm was deposited by LPCVD at 680 °C, and 100 nm titanium (Ti) was deposited by RF-sputter for gate electrode. The test devices have a gate width by length of 100/100  $\mu$ m. In order to investigate the impact of lateral charge migration on data retention, different gate stack structures were fabricated using a lithography mask, as shown in Figure 4. In extended structure (Ext. 10), the charge-trapping layer was extended to 10  $\mu$ m in every direction of the gate electrode. In Ext. 10 structure, the gate etch was stopped on the blocking oxide layer, while the charge trapping layer was etched self-aligned with the gate in the reference devices (Ref.).

**Figure 4.** Lithography mask layout to fabricate the test device with a cross-sectional view of the device. Here, Ext. 10 means the extension length of the charge trapping layer was 10  $\mu$ m. In the case of Ref., the charge trapping layer was etched and self-aligned with the gate and the extension length is 0  $\mu$ m.

### 3. Results and Discussion

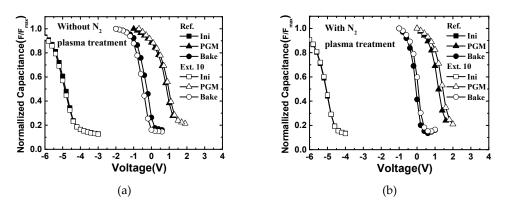

The program and retention behavior of the fabricated devices with and without  $N_2$  plasma treatment were measured as shown in Figure 5 and the charge loss during retention mode were calculated and are summarized in Table 1. The devices with extended trapping layer showed a larger memory window than the reference device, regardless of  $N_2$  plasma treatment. The reason for this is thought to be due to the fringe field effect of the extended devices. Furthermore, the over-etching issue has been shown to occur during the wet etching process in the reference devices, which in turn lowers program efficiency. However, the charge loss was larger after baking at 300 °C for 2 h. implying the intra-nitride charge spreading effect. The lateral charge loss of the extended devices was estimated to be about 28% in total charge loss. After  $N_2$  plasma treatment, the amount of charge loss deceased in the extended devices and the portion of lateral charge loss was 16%. For the quantitative comparison, nitride/oxide interface trap density was extracted using C–V method. When the positive bias was forced to the gate during C–V measurement, the charge was injected from the substrate and

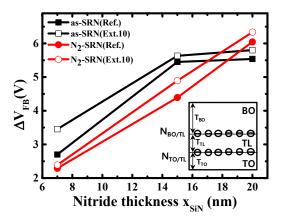

the flatband voltage (V<sub>FB</sub>) shifted due to charges captured at the traps. The V<sub>FB</sub> shift ( $\Delta$ V<sub>FB</sub>) enlarged with the increase in the ratio of occupied traps, and was finally saturated when all the traps were occupied. From the saturated  $\Delta$ V<sub>FB</sub>, according to the trapping layer thickness as shown in Figure 6, a respective trap density of the silicon nitride can be calculated based on the formula below [18].

$$\Delta V_{\rm FB} = \frac{qN_{\rm BO/TL}}{\varepsilon_{\rm SiO_2}\varepsilon_0} T_{BO} + \frac{q}{\varepsilon_{\rm SiN}\varepsilon_0} \int_0^{T_{\rm TL}} xN_{\rm Bulk}(x)dx + \frac{qT_{\rm BO}}{\varepsilon_{\rm SiO_2}\varepsilon_0} \int_0^{T_{\rm TL}} N_{\rm Bulk}(x)dx + \left(\frac{T_{\rm TL}}{\varepsilon_{\rm SiN}\varepsilon_0} + \frac{T_{\rm BO}}{\varepsilon_{\rm SiO_2}\varepsilon_0}\right) qN_{\rm BO/TL} = \frac{qN_{\rm Bulk}}{2\varepsilon_{\rm SiN}\varepsilon_0} T_{\rm TL}^2 + \left(\frac{qT_{\rm BO}N_{\rm Bulk}}{\varepsilon_{\rm SiO_2}\varepsilon_0} + \frac{qN_{\rm BO/TL}}{\varepsilon_{\rm SiN}\varepsilon_0}\right) T_{\rm TL} + \frac{qT_{\rm BO}N_{\rm BO/TL}}{\varepsilon_{\rm SiO_2}\varepsilon_0} + \frac{qT_{\rm BO}N_{\rm TO/TL}}{\varepsilon_{\rm SiO_2}\varepsilon_0}$$

(1)

where  $T_{BO}$ ,  $T_{TL}$ , and  $T_{TO}$  are the thickness of blocking oxide, trapping layer and tunneling oxide.  $N_{Bulk}$  (cm<sup>-3</sup>) is the trap density of trapping layer and  $N_{BO/TL}$  (cm<sup>-2</sup>) and  $N_{TO/TL}$  (cm<sup>-2</sup>) are the interface trap density of blocking oxide/trapping layer and tunneling oxide/trapping layer, respectively, as shown in inset of Figure 6. From the dependency of  $\Delta V_{FB}$  on the trapping layer thickness,  $N_{Bulk}$  can be assumed to be negligible and then, Equation (1) is expressed as follows.

$$\Delta V_{\rm FB} = \frac{qT_{\rm TL}N_{\rm BO/TL}}{\varepsilon_{\rm SiN}\varepsilon_0} + \frac{qT_{\rm BO}N_{\rm BO/TL}}{\varepsilon_{\rm SiO_2}\varepsilon_0} + \frac{qT_{\rm BO}N_{\rm TO/TL}}{\varepsilon_{\rm SiO_2}\varepsilon_0}$$

(2)

**Figure 5.** Measurement results of program and data retention characteristics of the fabricated devices (a) without  $N_2$  plasma treatment and (b) with treatment. Here, the retention properties were measured after baking at 300 °C for 2 h.

**Table 1.** Extracted trap density based on C–V analysis. Here,  $N_{BO/TL}$  and  $N_{TO/TL}$  are the interface trap density of blocking oxide/trapping layer and tunneling oxide/trapping layer, respectively.

| Sample                               | $N_{BO/TL}$ (cm <sup>-2</sup> ) | N <sub>TO/TL</sub> (cm <sup>-2</sup> ) | Charge Loss [%] |

|--------------------------------------|---------------------------------|----------------------------------------|-----------------|

| Ref.                                 | $2.53\times10^{12}$             | $8.91\times10^{11}$                    | 18.6            |

| Ext.10                               | $4.36 \times 10^{12}$           | $7.32 \times 10^{11}$                  | 25.7            |

| N <sub>2</sub> plasma treated Ref.   | $4.35 \times 10^{11}$           | $1.11 \times 10^{12}$                  | 17.3            |

| N <sub>2</sub> plasma treated Ext.10 | $5.21 \times 10^{11}$           | $1.18\times10^{12}$                    | 20.5            |

Based on Equation (2), the extracted trap densities are summarized in Table 1.

We can see that there was a distinct interface trap reduction in  $N_2$  plasma treatment, especially at blocking oxide and trapping layer (BO/TL) interface. Thus, charge loss decreased by 5.2% in extended  $N_2$  plasma devices. In the tunneling oxide and trapping layer (TO/TL) interface, the additional nitrogen supply effect by  $N_2$  plasma was ambiguous, but this may be because the nitrogen contributed to Si-O-N bonding formation on tunneling oxide, rather than curing the N vacancy in the nitride as the nitride was deposited after oxide formation. More consideration is needed to evaluate the accurate nitrogen behavior according to the underlying layer, but the results show that  $N_2$  plasma treatment was effective in reducing the interface trap between blocking oxide and silicon nitride while maintaining the nitride bulk trap.

**Figure 6.** Extracted results of  $V_{FB}$  shift in capacitance-voltage curve according to the trapping layer thickness. Inset shows the oxide/trapping layer interface trap sites in the SONOS device structure.

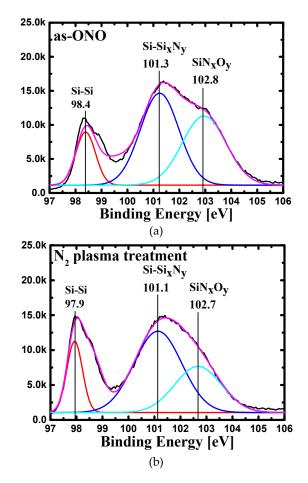

For the physical analysis on  $N_2$  plasma effect, XPS was also measured on the oxide/nitride interface to find the bonding state changes caused by plasma treatment. Figure 7 shows the XPS multi-peak fitting results. After  $N_2$  plasma treatment, the reduction of Si-O-N bonding was observed. The results show that when the additional nitrogen was incorporated into the nitride layer by the plasma treatment, N vacancies in nitride decreased, suppressing subsequent O interactions. This shows that  $N_2$  plasma treatment can be effective method to reduce the aforementioned O-related traps that are located at oxide/nitride interface.

**Figure 7.** X-ray Photoelectron Spectroscopy (XPS) results of Si2p multi peak fitting of nitride/oxide interface (**a**) as-nitride (without N<sub>2</sub> plasma treatment) and (**b**) N<sub>2</sub> plasma treated nitride.

#### 4. Conclusions

In this paper,  $N_2$  plasma treatment on silicon nitride is proposed as a solution to suppress the interface trap formation and charge spreading in a SONOS device. In order to investigate the impact of intra-nitride charge spreading on data retention in a 3D SONOS device where the charge trapping layer is shared in a cell string, different gate structures were fabricated using a lithography mask, and the charge loss appeared to be much more severe after baking at 300 °C for 2 h. After N<sub>2</sub> plasma treatment, both before and after a silicon nitride formation, charge loss was found to decrease. To extract the trap density quantitatively, C–V analysis method was used, which showed an apparent trap decrease, especially in blocking oxide and the trapping layer interface. XPS also showed the reduction of Si-O-N bonding after plasma treatment. The results indicate that N<sub>2</sub> plasma treatment on silicon nitride is effective to control the shallow O-related interface trap and improve the data retention characteristics of SONOS memory devices.

**Author Contributions:** Methodology, Formal Analysis, Investigation, Writing—original draft preparation, S.-D.Y.; Data Curation, Visualization, J.-K.J. and J.-G.L.; Conceptualization, S.-g.P.; Methodology, H.-D.L.; Conceptualization, Methodology, Writing—review and editing and Funding acquisition, Supervision G.-W.L.

**Funding:** This research was financially supported by Hynix semiconductor and the National Research Foundation of Korea (NRF) grant, funded by the Korea government (MSIP) (2017R1D1A1B03033601) and by Nano-Material Technology Development Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT and Future Planning. (2009-0082580).

Acknowledgments: The authors would like to thank Kyu-Suk Cho and Mun-sik Seo for technical comments and advice on the research.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Choi, J.; Seol, K.S. 3D approaches for non-volatile memory. In 2011 Symposium on VLSI Technology-Digest of Technical Papers; IEEE: Piscataway, NJ, USA, 2011; pp. 178–179.

- Jung, S.-M.; Jang, J.; Cho, W.; Cho, H.; Jeong, J.; Chang, Y.; Kim, J.; Rah, Y.; Son, Y.; Park, J.; et al. Three dimensionally stacked NAND flash memory technology using stacking single crystal Si layers on ILD and TANOS structure for beyond 30nm node. In 2006 International Electron Devices Meeting; IEEE: Piscataway, NJ, USA, 2006; pp. 1–4.

- 3. Cho, M.K.; Kim, D.M. High performance SONOS memory cells free of drain turn-on and over-erase: Compatibility issue with current flash technology. *IEEE Electron Device Lett.* **2000**, *21*, 399–401.

- Park, Y.-W.; Choi, J.; Kang, C.; Lee, C.; Shin, Y.; Choi, B.; Kim, J.; Jeon, S.; Sel, J.; Park, J.; et al. Highly Manufacturable 32Gb Multi – Level NAND Flash Memory with 0.0098 μm<sup>2</sup> Cell Size using TANOS (Si – Oxide - Al2O3 - TaN) Cell Technology. In 2006 International Electron Devices Meeting; IEEE: Piscataway, NJ, USA, 2006; pp. 1–4.

- De Salvo, B.; Geradi, C.; van Schaijk, R.; Lombardo, S.A.; Corso, D.; Plantamura, C.; Serafino, S.; Ammendola, G.; van Duuren, M.; Goarin, P.; et al. Performance and reliability features of advanced nonvolatile memories based on discrete traps (silicon nanocrystals, SONOS). *IEEE Trans. Device Mater. Reliab.* 2004, 4, 377–389. [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. In 2007 IEEE Symposium on VLSI Technology; IEEE: Piscataway, NJ, USA, 2007; pp. 14–15.

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Koromi, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra-high density storage devices. In 2009 Symposium on VLSI Technology; IEEE: Piscataway, NJ, USA, 2009; pp. 136–137.

- Jang, J.-H.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jeong, J.H.; Son, B.-K.; Kim, D.W.; Shim, J.-J.; et al. Vertical Cell Array using TCAT (Terabit Cell Array Transistor) Technology for Ultra High Density NAND Flash Memory. In 2009 Symposium on VLSI Technology; IEEE: Piscataway, NJ, USA, 2009; pp. 192–193.

- Kim, W.-J.; Choi, S.; Sung, J.; Lee, T.; Park, C.; Ko, H.; Jung, J.; Yoo, I.; Park, Y. "Multi-layered Vertical Gate NAND Flash overcoming stacking limit for terabit density storage. In 2009 Symposium on VLSI Technology; IEEE: Piscataway, NJ, USA, 2009; pp. 188–189.

- 10. Choi, E.S.; Park, S.K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. In 2012 International Electron Devices Meeting; IEEE: Piscataway, NJ, USA, 2012; pp. 9.4.1–9.4.4.

- 11. Maconi, A.; Arreghini, A.; Compagnoni, C.M.; Spinelli, A.S.; van Houdt, J.; Lacaita, A.L. Impact of lateral charge migration on the retention performance of planar and 3D SONOS devices. In 2011 Proceedings of the European Solid-State Device Research Conference (ESSDERC); IEEE: Piscataway, NJ, USA, 2011; pp. 195–198.

- Kang, C.-S.; Choi, J.; Sim, J.; Lee, C.; Shin, Y.; Park, J.; Sel, J.; Jeon, S.; Park, Y.; Kim, K.-N. Effects of lateral charge spreading on the reliability of TANOS (TaN/AlO/SiN/Oxide/Si) NAND flash memory. In 2007 *IEEE International Reliability Physics Symposium Proceedings*. 45th Annual; IEEE: Piscataway, NJ, USA, 2007; pp. 167–170.

- 13. Maconi, A.; Arreghini, A.; Compagnoni, C.M.; Spinelli, A.S.; van Houdt, J.; Lacaita, A.L. Comprehensive investigation of the impact of lateral charge migration on retention performance of planar and 3D SONOS devices. *Solid-State Electron.* **2012**, *74*, 64–70. [CrossRef]

- 14. Liu, L.; Arreghini, A.; Pan, L.; van Houdt, J. Comprehensive understanding of charge lateral migration in 3D SONOS memories. *Solid-State Electron.* **2016**, *116*, 95–99. [CrossRef]

- Morokov, Y.N.; Novikov, Y.N.; Gritsenko, V.A.; Wong, H. Two-fold coordinated nitrogen atom: an electron trap in MOS devices with silicon oxynitride as the gate dielectric. *Microelectron. Eng.* 1999, 48, 175–178. [CrossRef]

- Wong, H.; Gritsenko, V.A. Defects in silicon oxynitride gate dielectric films. *Microelectron. Reliab.* 2002, 42, 597–605. [CrossRef]

- 17. Perera, R.; Ikeda, A.; Hattori, R.; Kuroki, Y. Effects of post annealing on removal of defect states in silicon oxynitride films grown by oxidation of silicon substrates nitrided in inductively coupled nitrogen plasma. *Thin Solid Films* **2003**, *423*, 212–217. [CrossRef]

- Ishida, T.; Okuyama, Y.; Yamada, R. Characterization of charge traps in metal-oxide-nitride-oxide-semiconductor (MONOS) structures for embedded flash memories. In 2006 IEEE International Reliability Physics Symposium Proceedings; IEEE: Piscataway, NJ, USA, 2006; pp. 516–522.

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).