Video Article

# Writing and Low-Temperature Characterization of Oxide Nanostructures

Akash Levy<sup>1</sup>, Feng Bi<sup>1</sup>, Mengchen Huang<sup>1</sup>, Shicheng Lu<sup>1</sup>, Michelle Tomczyk<sup>1</sup>, Guanglei Cheng<sup>1</sup>, Patrick Irvin<sup>1</sup>, Jeremy Levy<sup>1</sup>

<sup>1</sup>Department of Physics, University of Pittsburgh

Correspondence to: Akash Levy at akl31@pitt.edu

URL: http://www.jove.com/video/51886

DOI: doi:10.3791/51886

Keywords: Physics, Issue 89, oxide nanostructures; nanoelectronics; semiconductor; LaAlO<sub>3</sub>/SrTiO<sub>3</sub>; lithography; AFM nanolithography

Date Published: 7/18/2014

Citation: Levy, A., Bi, F., Huang, M., Lu, S., Tomczyk, M., Cheng, G., Irvin, P., Levy, J. Writing and Low-Temperature Characterization of Oxide

Nanostructures. J. Vis. Exp. (89), e51886, doi:10.3791/51886 (2014).

#### **Abstract**

Oxide nanoelectronics is a rapidly growing field which seeks to develop novel materials with multifunctional behavior at nanoscale dimensions. Oxide interfaces exhibit a wide range of properties that can be controlled include conduction, piezoelectric behavior, ferromagnetism, superconductivity and nonlinear optical properties. Recently, methods for controlling these properties at extreme nanoscale dimensions have been discovered and developed. Here are described explicit step-by-step procedures for creating LaAlO<sub>3</sub>/SrTiO<sub>3</sub> nanostructures using a reversible conductive atomic force microscopy technique. The processing steps for creating electrical contacts to the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface are first described. Conductive nanostructures are created by applying voltages to a conductive atomic force microscope tip and locally switching the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface to a conductive state. A versatile nanolithography toolkit has been developed expressly for the purpose of controlling the atomic force microscope (AFM) tip path and voltage. Then, these nanostructures are placed in a cryostat and transport measurements are performed. The procedures described here should be useful to others wishing to conduct research in oxide nanoelectronics.

### Video Link

The video component of this article can be found at http://www.jove.com/video/51886/

### Introduction

Oxide heterostructures<sup>1-5</sup> exhibit a remarkably wide variety of emergent physical phenomena which are both scientifically interesting and potentially useful for applications<sup>4</sup>. In particular, the interface between LaAlO<sub>3</sub> (LAO) and SrTiO<sub>3</sub> (STO)<sup>6</sup> can exhibit insulating, conducting, superconducting<sup>7</sup>, ferroelectric-like<sup>8</sup>, and ferromagnetic<sup>9</sup> behavior. In 2006, Thiel *et al* showed<sup>10</sup> that there is a sharp insulator-to-metal transition as the thickness of the LAO layer is increased, with a critical thickness of 4 unit cells (4uc). It was subsequently shown that 3uc-LAO/STO structures exhibit a hysteretic transition that can be controlled locally with a conductive atomic-force microscope (c-AFM) probe<sup>11</sup>.

The properties of oxide interfaces such as LaAlO<sub>3</sub>/SrTiO<sub>3</sub> depend on the absence or presence of conducting electrons at the interface. These electrons can be controlled using top gate electrodes <sup>12,13</sup>, back gates <sup>10</sup>, surface adsorbates <sup>14</sup>, ferroelectric layers <sup>15,16</sup> and c-AFM lithography <sup>11</sup>. A unique feature of c-AFM lithography is that very small nanoscale features can be created.

Electrical top gating, combined with two-dimensional confinement, is often used to create quantum dots in III-V semiconductors <sup>17</sup>. Alternatively, quasi-one-dimensional semiconducting nanowires can be electrically gated by proximity. The methods for producing these structures are time-consuming and generally irreversible. By contrast, the c-AFM lithography technique is reversible in the sense that a nanostructure can be created for one experiment, and then "erased" (similar to a whiteboard). Generally, c-AFM writing is performed with positive voltages applied to the AFM tip, while, erasing is performed using negative voltages. The time required to create a particular structure depends on the complexity of the device but is usually less than 30 min; most of that time is spent erasing the canvas. The typical spatial resolution is about 10 nanometers, but with proper tuning features as small as 2 nanometers can be created <sup>18</sup>.

A detailed description of the nanoscale fabrication procedure follows. The detail provided here should be sufficient to allow similar experiments to be performed by interested researchers. The method described here has many advantages over traditional lithographic approaches used to create electronic nanostructures in semiconductors.

The c-AFM lithography method described here is part of a much broader class of scanning-probe-based lithography efforts, including scanning anodic oxidation <sup>19</sup>, dip-pen nanolithography<sup>20</sup>, piezoelectric patterning<sup>21</sup>, and so on. The c-AFM technique described here, coupled with the use of novel oxide interfaces, can produce some of the highest-precision electronic structures with an unprecedented variety of physical properties.

#### **Protocol**

### 1. Obtain LAO/STO Heterostructures

Obtain an oxide heterostructure consisting of 3.4 unit cells of LAO grown by pulsed laser deposition on TiO<sub>2</sub>-terminated STO substrates. Details of sample growth are described in Ref.

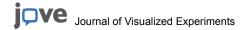

# 2. Photolithographic Processing of Samples

Create electrical contacts to the LAO/STO interface, with bonding pads for wiring canvases to a chip carrier. The individual processing steps are described in detail below.

- Spin photoresist

- 1. Spin photoresist on the samples at 600 rpm for 5 sec, then at 4,000 rpm for 30 sec. The photoresist layer will be about 2 µm thick. Bake the samples at 95 °C for 1 min.

- 2. Expose photoresist using a mask aligner with 320 nm light for 100 sec with a dose of 5 mW/cm<sup>2</sup>.

- 3. Develop the photoresist in photoresist developer for 1 min.

- Ion milling

- 1. Use an Ar<sup>+</sup> ion mill to remove 15 nm of material (LAO and STO) in the areas not covered by photoresist. Place the samples at a 22.5° angle to the direction perpendicular to the incoming Ar+ ion beam. If the Ar+ etching rate is not calibrated, perform a calibration run to ensure that the correct amount of material is removed. Determine the etching depth using AFM or equivalent profilmetry.

- 5. DC sputtering of Ti and Au

- 1. Deposit 4 nm Ti, then 25 nm Au onto the samples so that the Au makes electrical contact with the exposed STO layer. The sputtering pressure is in the range 2-6 x 10<sup>-7</sup> Torr, and the sputtering takes place with the sample at RT. Pre-sputter Ti for 10 min with shutter closed at 100 W, then open shutter and sputter for 20 sec at 100 W. Upon completion, immediately pre-sputter Au for 1 min at 50 W then sputter Au for 30 sec to the samples at 50 W. Calibrate the time to produce the desired Ti and Au thicknesses.

- Lift-off

- Use Acetone/IPA ultrasonic wash to remove photoresist from the surface of the samples.

- Second laver

- 1. A second lithographic process, excluding step 4 (i.e., excluding ion milling), is used to create gold wire connections to individual bonding pads. The two patterns must be well-aligned to ensure that they do not produce electrical shorts.

- Plasma cleaning.

- 1. An IPC Barrel Etcher is used to remove the photoresist residue in the pattern trench. The instrument used at the 100 W and 1 Torr argon for 1 min

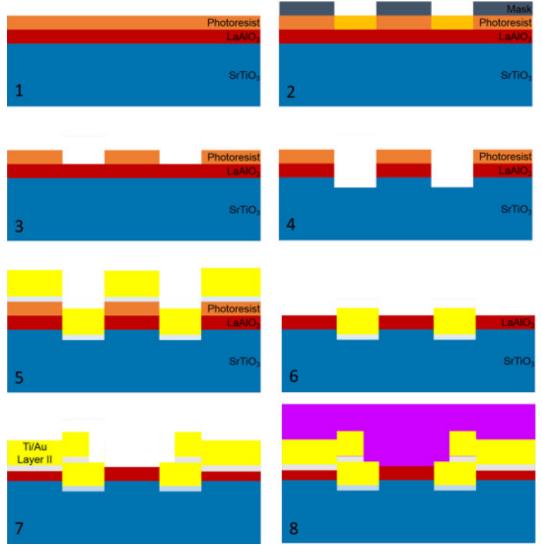

## 3. Wire Bond a Sample to Prepare for Writing

- Mount the LAO/STO sample in a chip carrier (Figure 2A) with 28 available pins.

- Wire bond structure

NOTE: Use a wire bonder to make electrical connections between bonding pads on the sample and the chip carrier. Attach 1 mil (25 micrometer) gold wires between the electrical contacts and the chip carrier. Write nanostructures

## 4. Write Nanostructures

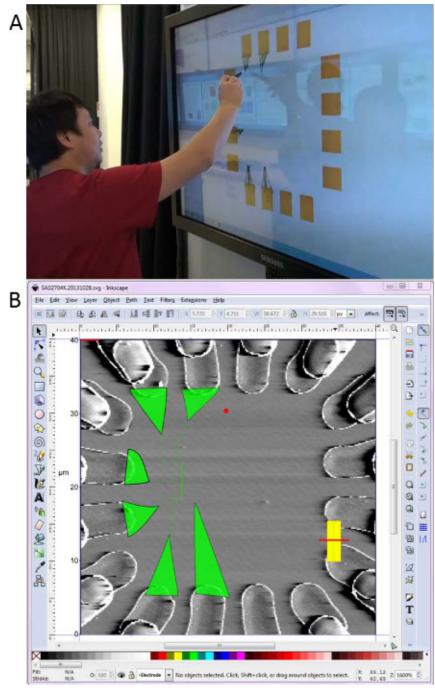

- 1. Create an informal sketch of the conductive nanostructure (Figure 3A).

- 2. Open the scalable vector graphics (SVG) editor (Figure 3B).

- 1. Use a template or define the window size to match that of the AFM image.

- 2. Load the AFM image of the sample into the SVG editor.

- 3. Create nanostructure elements overlaid on the AFM image.

- 3. Load the SVG file into the nanolithography program.

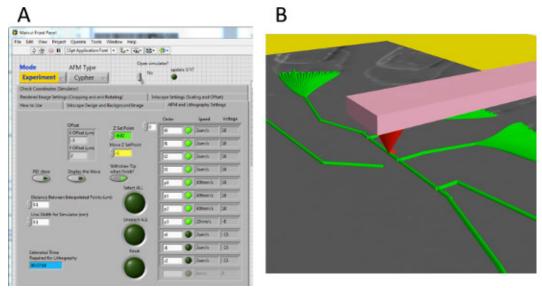

- Run the lithography software to create a conductive nanostructure.

- 1. Use  $V_{tip}$ =+10 V to create nanostructures, and  $V_{tip}$ =-10 V to erase nanostructures.

- 2. Move the c-AFM tip at a speed ranging from 200 nm/sec to 2 µm/sec.

### 5. Cool Device and Take Measurements

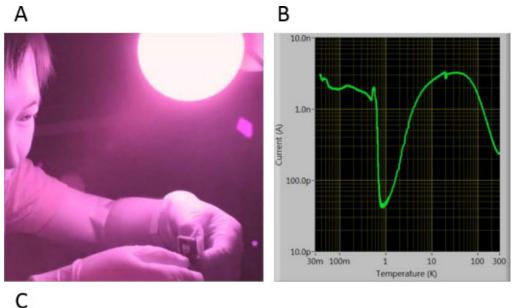

1. Turn off all white lights and use red filters/light sources.

- 2. Extract the sample from the AFM system.

- 3. Load the sample into the dilution refrigerator (A).

- 4. Measure resistance vs. temperature (B) as the sample is cooled.

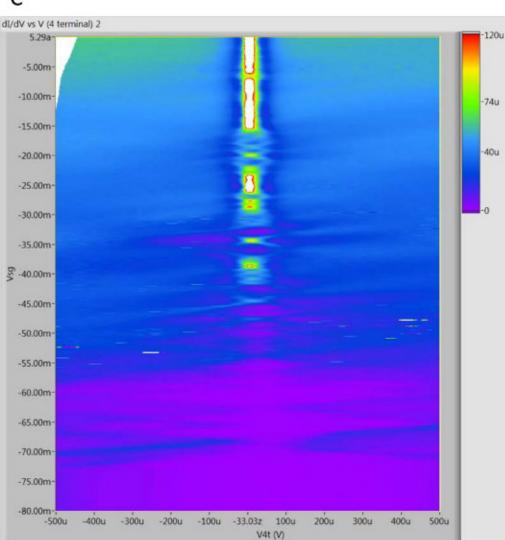

- 5. Measure transport properties at low temperatures (C).

### **Representative Results**

The results shown here are representative of the transport behavior that can be exhibited by this class of nanostructures, and has been described elsewhere in detail<sup>23-26</sup>. In this example, a nanowire cavity has been constructed (**Figure 4**) from a 3.3 unit cell LAO/STO heterostructure. Conductive paths (shown in green) are typically 10 nm wide, as determined by nanowire "cutting" experiments<sup>11</sup>. The tip speed and voltage for each segment is independently configurable from the lithography front panel (**Figure 4B**), as is the tip writing speed. "Virtual electrodes" that interface with the interfacial contacts ensure that there is a highly conductive electrical connection to the nanostructures.

After the nanostructure is written, it is transferred to the dilution refrigerator. Exposure to light at or below 550 nm will produce unwanted photoconduction, so it is important to transfer the device in darkness or with the aid of a red "darkroom" light (**Figure 5A**). Electrical connections should be made at RT, and as with most semiconductor nanostructures, great care should be taken when changing electrical connections at cryogenic temperatures. If the devices is subjected to electrostatic discharge, it will most likely become insulating. Remarkably, the device functionality can be recovered by "cycling" the temperature to 300 K and cooling down again.

During cooldown, it is routine to monitor the two-terminal resistance, and even the four-terminal resistance, as a function of temperature. For these measurements an ac voltage (typically ~1 mV) is applied at a low frequency (<10 Hz) to one of the electrodes, while the ac current is measured using a transimpedance amplifier. Lock-in demodulation and filtering is performed using a home-developed lock-in amplifier. The ac current is monitored as a function of temperature (**Figure 5B**).

Once the device is cooled to the base temperature of the dilution refrigerator (50 mK), four-terminal transport measurements are performed (**Figure 5C**). For these measurements, current is sourced through the main channel of the device, while voltage across the device is simultaneously measured. Instead of measuring with a lock-in amplifier, a full current-voltage (I-V) trace is measured. This method contains more information and the differential conduction can be calculated via numerical differentiation. For the particular device, the differential conduction is measured as a function of the side-gate voltage  $V_{sg}$ . This gate allows the chemical potential of the device to be changed. The transport through the device shows a strong non-monotonic dependence, indicating regions in which Coulomb blockade takes place for smaller values, and strong superconductivity for larger values of  $V_{sg}$ . Details about the physical interpretation for this class of device will be described elsewhere.

**Figure 1. Photolithographic processing steps.** Step 1: spin photoresist. Step 2: expose photoresist using mask aligner. Step 3: develop photoresist. Step 4: ion milling. Step 5: DC sputtering to deposit Ti and Au. Step 6: lift-off. Step 7: deposit the second layer. Step 8: plasma cleaning.

Figure 2. Images of lithographically patterned LAO/STO heterostructures. (A) Image showing 5mm x 5mm sample wire bonded to a chip carrier. (B) Optical image showing bonding pads and one of the canvases. (C) Close-up of a single canvas. Please click here to view a larger version of this figure.

Figure 3. (A) Informal design of LAO/STO nanostructure. (B) Precise layout of nanostructure using an open-source scalable vector graphics (SVG) editor.

Figure 4. (A) Lithography front panel for c-AFM patterning. (B) Screenshot from 3D simulator showing position and voltage of c-AFM tip. Please click here to view a larger version of this figure.

Figure 5. (A) LAO/STO nanostructure being inserted into dilution refrigerator. (B) Monitoring of sample resistance as it is cooled from 300 K to 50 mK. (C) Monitoring of four-terminal differential conductance of device as a function of side gate voltage Vsg and voltage across the device (V4t). Intensity graph displayed in units of siemens (S), and voltages are displayed in units of volts (V).

### **Discussion**

Successful creation of nanostructures depends on several critical steps. It is important that the LAO/STO samples are grown with a thickness that is known to be at the boundary between the insulating and conductive phase. (Details of sample growth fall outside the scope of this paper, but are crucial for overall success.) Second, it is important to have relative humidity within the range 25-45% for successful c-AFM writing. Values below 25% are unlikely to produce conductive nanostructures, while too high humidity will generally produce uncontrollably large features. Also, temperature control of the AFM is important if the c-AFM tip needs to achieve precise registry over long periods of time. Once the nanostructures are created, they must be placed in a vacuum environment if experiments lasting longer than a few hours are to be performed. For the experiments described here, the structure is created and within minutes transferred to a vacuum environment.

It is recommend before writing that a "writing test" be performed on all relevant electrodes. In such a test, two virtual electrodes are first created, and a single nanowire is written while simultaneously monitoring the conductance. A similar test of erasure can be performed by "cutting" the nanowire shortly afterwards. If the nanostructure is decaying rapidly, the issue is most likely due either to the interfacial contacts or the canvas itself. To distinguish between these two effects, a four-terminal measurement of the conductance should be performed, and the two-terminal conductance should be compared with the four-terminal conductance as a function of time. If the two-terminal conductance is decaying more rapidly than the four-terminal conductance, then the issue is related to the electrical contacts to the interface. If the four-terminal conductance is decaying at a comparable rate, then most likely the canvas is not suitable and should be replaced.

There are natural limitations of the current method for creating nanostructures. Specifically, the writing speed for the smallest devices is limited to a few hundred nanometers per second. Speeds far above that value lead to unpredictable results. Use of parallel writing techniques are possible<sup>27,28</sup>, but are not highly developed and have their own drawbacks. The size of nanostructures that can be created is naturally limited by the scan range of the AFM being used. A high-quality AFM with closed-loop feedback in the two scan directions is highly recommended. Tracking of point-like objects on the sample surface should be performed to monitor temporal drift of the sample.

Once creation of conductive nanostructures at oxide interfaces has been mastered, there are a wide range of experimental directions that can be explored. Using this technique, a wide variety of nanostructures and devices have already been demonstrated, including nanowires 18, tunnel barriers 29, rectifying junctions 30, field-effect transistors 18, single-electron transistors 31, superconducting nanowires 32, nanoscale optical detectors 33, and nanoscale THz emitters and detectors 34.

#### **Disclosures**

The authors have nothing to disclose.

### **Acknowledgements**

The long-standing collaboration with Chang-Beom Eom at the University of Wisconsin-Madison, who provided the LAO/STO samples, is gratefully acknowledged. Video editing assistance from Christopher Solis is greatly appreciated. This work is supported by NSF (DMR-1104191, DMR-1124131), ARO (W911NF-08-1-0317), and AFOSR (FA9550-10-1-0524, FA9550-12-1-0268, FA9550-12-1-0057).

### References

- Sulpizio, J. A., Ilani, S., Irvin, P., & Levy, J. i. Annual Review of Materials Research, in press. (2014).

- Mannhart, J., Blank, D. H. A., Hwang, H. Y., Millis, A. J., & Triscone, J. M. Two-Dimensional Electron Gases at Oxide Interfaces. Mrs Bulletin. 33, 1027-1034, doi:10.1557/mrs2008.222 (2008).

- Zubko, P., Gariglio, S., Gabay, M., Ghosez, P., & Triscone, J.-M. Vol. . Annual Review of Condensed Matter Physics. (ed J. S. Langer) 'Interface Physics in Complex Oxide Heterostructures' 141-165 doi:10.1146/annurev-conmatphys-062910-140445 (2011).

- Bogorin, D. F., Irvin, P., Cen, C., & Levy, J. i. Multifunctional Oxide Heterostructures. eds Evgeny Y. Tsymbal, Elbio R. A. Dagotto, Chang-Beom Eom., & Ramamoorthy Ramesh) Ch. 13, 'LaAlO<sub>3</sub>/SrTiO<sub>3</sub>-Based Device Concepts' doi:10.1093/acprof:oso/9780199584123.003.0013 Oxford University Press (2012).

- 5. Granozio, F. M., Koster, G., & Rijnders, G. Functional Oxide Interfaces. MRS Bulletin. 38, 1017-1023, doi:10.1557/mrs.2013.282 (2013).

- Ohtomo, A., & Hwang, H. Y. A high-mobility electron gas at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterointerface. Nature. 427, 423-426, doi:10.1038/ nature02308 (2004).

- 7. Revren, N. et al. Superconducting interfaces between insulating oxides. Science, 317, 1196-1199, doi:10.1126/science.1146006 (2007).

- Bark, C. W. et al. Switchable Induced Polarization in LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Heterostructures. Nano Letters. 12, 1765-1771, doi:10.1021/nl3001088 (2012).

- Brinkman, A. et al. Magnetic effects at the interface between non-magnetic oxides. Nature Materials. 6, 493-496 (2007).

- 10. Thiel, S., Hammerl, G., Schmehl, A., Schneider, C. W., & Mannhart, J. Tunable quasi-two-dimensional electron gases in oxide heterostructures. Science. 313, 1942-1945, doi:10.1126/science.1131091 (2006).

- 11. Cen, C. et al. Nanoscale control of an interfacial metal-insulator transition at room temperature. Nature Materials. 7, 298-302, doi:10.1038/ nmat2136 (2008).

- 12. Singh-Bhalla, G. et al. Built-in and induced polarization across LaAlO<sub>3</sub>/SrTiO<sub>3</sub> heterojunctions. Nature Physics. 7, 80-86, doi:10.1038/ nphys1814 (2011).

- 13. Li, L. et al. Very Large Capacitance Enhancement in a Two-Dimensional Electron System. Science. 332, 825-828, doi:10.1126/ science.1204168 (2011).

- 14. Xie, Y., Hikita, Y., Bell, C., & Hwang, H. Y. Control of electronic conduction at an oxide heterointerface using surface polar adsorbates. Nature Communications. 2, 494, doi:10.1038/ncomms1501 (2011).

- Bark, C. W. et al. Tailoring a two-dimensional electron gas at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> (001) interface by epitaxial strain. PNAS. 108, 4720-4724, doi:10.1073/pnas.1014849108 (2011).

- Tra, V. T. et al. Ferroelectric Control of the Conduction at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Heterointerface. Adv Mater. 25, 3357-3364, doi:10.1002/adma.201300757 (2013).

- 17. Cronenwett, S. M., Oosterkamp, T. H., & Kouwenhoven, L. P. A Tunable Kondo Effect in Quantum Dots. Science. 281, 540-544, doi:10.1126/science.281.5376.540 (1998).

- 18. Cen, C., Thiel, S., Mannhart, J., & Levy, J. Oxide Nanoelectronics on Demand. *Science*. **323**, 1026-1030, doi:DOI 10.1126/science.1168294 (2009).

- 19. Kalinin, S. V., & Gruverman, A. Scanning probe microscopy: electrical and electromechanical phenomena at the nanoscale. Vol. 1 Springer (2007).

- 20. Piner, R. D., Zhu, J., Xu, F., Hong, S. H., & Mirkin, C. A. 'Dip-pen' nanolithography. *Science*. **283**, 661-663, doi:10.1126/science.283.5402.661 (1999).

- Ahn, C. H. et al. Local, Nonvolatile Electronic Writing of Epitaxial Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub>/SrRuO<sub>3</sub> Heterostructures. Science. 276, 1100-1103, doi:10.1126/science.276.5315.1100 (1997).

- 22. Bi, F. et al. 'Water-cycle' mechanism for writing and erasing nanostructures at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface. Applied Physics Letters. **97**, 173110, doi:10.1063/1.3506509 (2010).

- 23. Cheng, G. *et al.* Anomalous Transport in Sketched Nanostructures at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Interface. *Phys Rev X.* **3**, 011021, doi:10.1103/PhysRevX.3.011021 (2013).

- 24. Veazey, J. P. et al. Nonlocal current-voltage characteristics of gated superconducting sketched oxide nanostructures. *Europhys Lett.* **103**, 57001, doi:10.1209/0295-5075/103/57001 (2013).

- Veazey, J. P. et al. Oxide-based platform for reconfigurable superconducting nanoelectronics. Nanotechnology. 24, 375201, doi:10.1088/0957-4484/24/37/375201 (2013).

- 26. Irvin, P. et al. Anomalous High Mobility in LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Nanowires. Nano Letters. 13, 364-368, doi:10.1021/nl3033729 (2013).

- 27. Salaita, K. et al. Massively Parallel Dip—Pen Nanolithography with 55 000-Pen Two-Dimensional Arrays. Angewandte Chemie. 118, 7378-7381, doi:10.1002/ange.200603142 (2006).

- 28. Li, S. et al. Parallel Conductive-AFM Lithography on LaAlO3/SrTiO3 Interfaces. leee T Nanotechnol. 12, 518-520, doi:Doi 10.1109/Tnano.2013.2256465 (2013).

- 29. Cen, C., Bogorin, D. F., & Levy, J. Thermal activation and quantum field emission in a sketch-based oxide nanotransistor. *Nanotechnology*. **21**, 475201, doi:10.1088/0957-4484/21/47/475201 (2010).

- 30. Bogorin, D. F. et al. Nanoscale rectification at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface. *Applied Physics Letters.* **97**, 013102, doi:10.1063/1.3459138 (2010).

- 31. Cheng, G. et al. Sketched Oxide Single-Electron Transistor. Nature Nanotech. 6, 343-347 (2011).

- 32. Joshua, A., Ruhman, J., Pecker, S., Altman, E., & Ilani, S. Gate-tunable polarized phase of two-dimensional electrons at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> interface. *PNAS.* **110**, 9633, doi:10.1073/pnas.1221453110 (2013).

- 33. Irvin, P. et al. Rewritable Nanoscale Oxide Photodetector. Nature Photon. 4, 849-852, doi:10.1038/nphoton.2010.238 (2010).

- 34. Ma, Y. et al. Broadband Terahertz Generation and Detection at 10 nm Scale. Nano Letters. 13, 2884-2888, doi:10.1021/nl401219v (2013).